Из таблиц видно, что Т-триггер выполняет сложение по модулю два входного сигнала и внутреннего состояния Q и его характеристическое уравнение есть уравнение сумматора по модулю два:

![]()

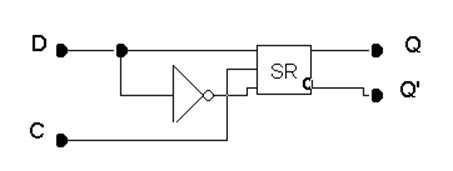

1.4. D-триггеры. Недостаток SR-триггера, заключающийся в наличии неопределенных состояний, устранить можно еще одним способом – просто не допускать их введением нового входа D = S = R', т.е. соединить входы S и R через инвертор. Этому соединению (без входа синхронизации С) соответствует таблица переходов SR-триггера (табл. 4.1) со строками, где на входы S и R подаются противофазные сигналы. При этом получается бесполезный триггер, который просто повторяет сигнал на входе S = D. D-триггер приобретает смысл, если использовать не асинхронный, а синхронный SR-триггер, как показано на рис. 4.5.

Рис. 4.5. Структурная схема D-триггера

При этом характеристическое уравнение D-триггера (его легко получить) имеет следующий вид:

![]()

Тогда, как следует из уравнения, при С = 1 D-триггер воспроизводит входной сигнал и представляет собой элемент задержки; при С = 0 запоминается предшествующее состояние Q. Таблицу переходов состояний и словарь переходов синхронных D-триггеров мы не приводим, они элементарны.

Чтобы обойти недостаток управляемых состоянием D-триггеров, который заключается во влиянии помех во время тактового импульса , применяют двухступенчатые триггеры или триггеры с управлением по фронтам. Нарисуйте схему двухступенчатого синхронного D-триггера на основе двухступенчатого SR-тригерра (рис. 4.2).

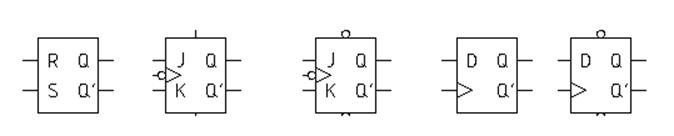

4.5. Модели триггеров в программе EWB.В библиотеке EWB триггеры представлены тремя типами: RS, JK и D, показанными на рис. 4.6.

Рис. 4.6 Модели триггеров программы EWB

Назначение выводов триггеров соответствуют нашим обозначениям в тексте. Приведем лишь некоторые уточняющие сведения. Для JK триггера: > — тактовый вход; вывод сверху – асинхронная предустановка триггера в единичное состояние (Q=1); вывод внизу – асинхронная предустановка триггера в нулевое состояние (очистка триггера, после которой Q’ = 1). Наличие кружочков на изображениях выводов обозначает, что активными являются сигналы низкого уровня, а для тактового входа – что переключение триггера производится по заднему фронту тактового импульса.

2. Сдвигающие регистры

Регистры – это семейство последовательностных цифровых устройств, выполняющих следующие функции памяти: приема (запоминания), хранения, передачи (забывания) и преобразования информации. Регистры состоят из цепочки триггеров; их число определяет разрядность регистра. Триггеры связываются между собой комбинационными схемами управления, которые определяют многочисленные типы регистров. Регистры – самые распространенные устройства в цифровой технике. Типы регистров определяются способами приема и выдачи данных: параллельные, последовательные (сдвигающие) и параллельно-последовательные.

Здесь мы рассмотрим один из основных типов регистров – сдвигающиерегистры, у которых функции памяти реализуются на триггерах с помощью управляющего сигнала сдвига. При этом сигнал сдвига играет роль синхроимпульса и наоборот. Применения сдвигающих регистров очень разнообразны. В арифметических операциях, например, сдвиг числа на один разряд влево соответствует умножению его на 2, сдвиг вправо – делению на 2. Вообще регистры сдвига используются в центральных процессорах компьютеров при проведении арифметических операций и служат специальными запоминающими устройствами. Кроме того, они также применяются для последовательно-параллельного и параллельно-последовательного преобразования кодов. При этом сдвигающие регистры могут иметь следующие свойства:

· возможность переключения направления сдвига (влево—вправо);

· наличие параллельных входов для одновременной установки триггеров;

· наличие параллельных выходов;

· наличие последовательных входов и выходов.

Уважаемый посетитель!

Чтобы распечатать файл, скачайте его (в формате Word).

Ссылка на скачивание - внизу страницы.