Данный способ наращивания размерности мультиплексоров является общим и сводится к каскадному соединению мультиплексоров меньшей размерности. На первом ярусе соединения количество мультиплексоров определяется количеством каналов. Количество входных каналов для последующих ярусов последовательно уменьшается в 2n раз, где n – количество каналов используемого для наращивания мультиплексора. Например, для мультиплексора 16-1, построенного на мультиплексорах 4-1, первый ярус, очевидно, будет состоять из четырех мультиплексоров 4-1, а второй ярус – из одного. Этот же мультиплексор 16-1, построенный на мультиплексорах 2-1, будет состоять из восьми MUX 2-1 первого яруса, из четырех MUX 2-1 второго яруса и одного MUX 2-1 третьего яруса. При соединении мультиплексоров одноименные адресные входы на всех ярусах соединяются и образуют адресные входы составного мультиплексора. При этом младшие разряды образуются на первом ярусе и далее по порядку до последнего яруса, где образуется старший разряд.

2. Демультиплексоры (распределители данных)

2.1.Построение логических схем демультиплексоров.

Демультиплексоры ( DMUX ) – это комбинационные устройства, выполняющие функции многопозиционных переключателей (распределителей) одного цифрового канала на один из нескольких, работающие под цифровым управлением. Между мультиплексорами и демультиплексорами существует связь. Именно, при одинаковом числе переключаемых каналов, мультиплексор подключает один из нескольких входных каналов на один выход, а демультиплексор наоборот — подключает один входной канал на один из нескольких выходных. При этом при равном числе каналов для цифрового управления мультиплексор и демультиплексор имеют одинаковую разрядность адресных входов. Отсюда следует, что для синтеза схем демультиплексоров можно использовать методику составления таблиц истинности мультиплексоров, где в колонке входных каналов данных D проставляем один канал – D0, а вместо одного канала на выходе мультиплексора F, вводим необходимое число каналов демультиплексора: F0, F1 , … Fn.

Синтезируем схему базового демультиплексора 1-2 по составленной таблице истинности (табл. 3.3), соответствующей мультиплексору 2-1 (табл. 3.1) .

Таблица 3.3.

|

А0 |

D |

F1 |

F0 |

|

0 |

D0 |

0 |

1 |

|

1 |

D0 |

1 |

0 |

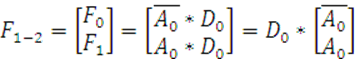

Из табл. 3.3 имеем

![]()

![]() (3.4)

(3.4)

Демультиплексор 2-1 имеет два выхода и описывается системой логических функций, которую можно представить в векторной форме как

(3.5)

(3.5)

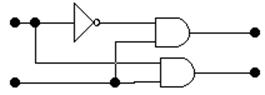

Полученные формулы просты, и логическая схема базового DMUX 1-2, определяемая выражениями (3.4) или (3.5), показана на рис. 3.4

|

|

Рис. 3.4. Логическая схема DMUX 1- 2 .

Таблицы истинности демультиплексоров обладают уникальным свойством: выходные каналы кодируются расположением единственной 1 в многоразрядном коде, в нашем случае — в двухразрядном F1F0 (см. табл. 3.3). В общем случае, если n — номер канала, то его код на выходе демультиплексора — (10)2n . Вообще двоичный n-разрядный код с 1 в одном разряде и с 0 в других называется унарным.

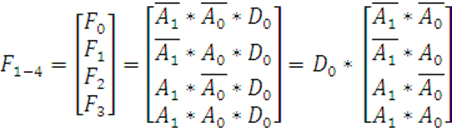

Теперь, имея общее правило записи системы логических формул для демультиплексоров с произвольным количеством каналов, запишем систему логических функций для DMUX 1- 4 без составления таблицы истинности.

(3.6)

(3.6)

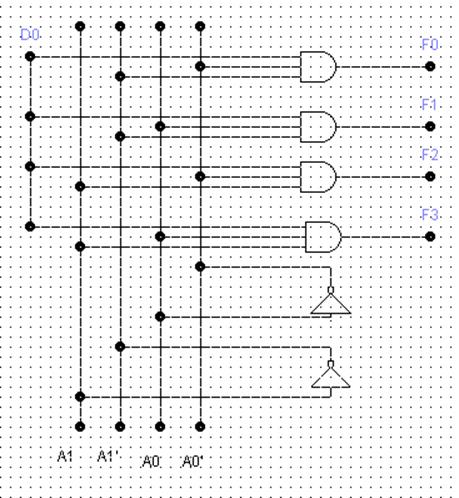

Прямой способ реализации системы логических уравнений (3.6) приводит к следующей схеме DMUX 1-4 (рис. 3.5).

Рис. 3.5. Логическая схема DMUX 1- 4 на элементах И, НЕ.

2.2. Наращивание размерности демультиплексоров

Уважаемый посетитель!

Чтобы распечатать файл, скачайте его (в формате Word).

Ссылка на скачивание - внизу страницы.