Министерство образования Республики Беларусь

Беларусcкий Государственный Университет

Информатики и Радиоэлектроники

Кафедра ЭВМ

К защите допускаю:

____________ / /

«___» мая 1998 г.

Пояснительная записка

к курсовой работе по АИЛОВТ

на тему:

“ Синтез устройства умножения двоично-четверичных

чисел в дополнительных кодах “

Выполнил: студент гр.650501

Вольнов И

Руководитель:

Минск 1998

Cодержание

1. Постановка задачи ......................................................................................... 3

2. Разработка алгоритма умножения ................................................................. 4

3. Разработка структурной схемы ..................................................................... 6

4. Разработка функциональных схем ............................................................... 9

4.1. Логический синтез ОЧУС .............................................................................. 9

4.2. Логический синтез ОЧС .............................................................................. 14

5. Синтез ОЧС на мультиплексорах ............................................................... 27

6. Синтез управляющего автомата .................................................................... 28

7. Литература ....................................................................................................... 33

1. Постановка задачи

В данной курсовой работе необходимо синтезировать цифровые схемы арифметических устройств, выполняющих операцию умножения в дополнительных кодах над числами представленными в форме с плавающей запятой в двоичной и двоично-четверичной системе счисления.

Исходные данные:

· Табл.1 задает кодирование четверичных чисел их двоичными эквивалентами для работы в двоично-четверичной системе счисления.

Таблица 1.

|

Цифра |

1 |

2 |

3 |

4 |

|

Код |

00 |

10 |

01 |

11 |

· В табл.2 приведены исходные операнды - десятичные числа.

Таблица 2.

|

Мн |

Мт |

|

48.51 |

69.11 |

· Типы синтезируемых устройств:

ОЧУС – одноразрядный четверичный умножитель-сумматор. ОЧС -- одноразрядный четве-ричный сумматор.

· Алгоритм умножения - “Б” (с младших разрядов множителя со сдвигом частичных произведе-ний влево) ;

· Способ минимизации устройств :

OЧУС -- с помощью карт Карно-Вейча. ОЧС – алгоритмом Рота.

· Табл.3 определяет логические элементы, входящие в состав заданных логических базисов для построения ОЧС и ОЧУС.

Таблица 3

|

Тип устройства |

Функционально-полный базис. |

Базовые логические элементы |

|

ОЧУС |

Х1Х2 |

|

|

ОЧС |

X1X2 X |

2.Разработка алгоритма умножения

Перевод сомножителей из десятичной системы счисления в четверичную:

Мн 10 à Мн 4 Мн 4 = 300,2002

Мн 2/4

=

110000,010000

Мн 2/4

=

110000,010000

48 4 0. 51

4 12 4 4

8 12 3 4 2. 04

8 0 4

0 0. 16

4

0, 64

Мт 10 à Мт 4 Мт 4 = 1011,013

Мт 2/4 = 10001010,0010

69 4 0, 11

68 17 4 4

1 16 4 4 0, 44

1 4 1 4

0 1, 76

4

3, 04

Сомножители в форме с плавающей запятой:

Мн2 = 0,110000010000 0.0011 Мт2 = 0,100010100010 0.1000

Порядок произведения:

Р1=0. 0011 3

Р2=0.1000 4

Р =0.1011 7

Перемножение мантисс приведено в табл. 4

Таблица 4

|

Четверичная с/c |

2/4 система счисления |

|||

|

1 такт |

||||

|

Мн |

0000000 |

3002000 |

00000000000000 |

11000001000000 |

|

Мт |

1011132 |

10001010101101 |

||

|

0000001 |

2010000 |

00000000000010 |

01001000000000 |

|

|

2 такт |

||||

|

Мн |

0000003 |

0022230 |

00000000000011 |

00000101011100 |

|

Мт |

0101113 |

00100010101011 |

||

|

0000022 |

2211122 |

00000000000101 |

01011010100101 |

|

|

3 такт |

||||

|

Мн |

0000030 |

0222300 |

00000000001100 |

00010101110000 |

|

Мт |

0010111 |

00001000101010 |

||

|

0000112 |

3100022 |

00000000101001 |

11100000000101 |

|

|

4 такт |

||||

|

Мн |

0000300 |

1113000 |

00000000110000 |

01010111000000 |

|

Мт |

0001011 |

00000010001010 |

||

|

0001013 |

1323022 |

00000010001011 |

10110111000101 |

|

|

5 такт |

||||

|

Мн |

0003002 |

2230000 |

00000011000001 |

01011100000000 |

|

Мт |

0000101 |

00000000100010 |

||

|

0010021 |

0213022 |

00001000000110 |

00011011000101 |

|

|

6 такт |

||||

|

Мн |

0030022 |

2300000 |

00001100000101 |

01110000000000 |

|

Мт |

0000010 |

00000000001000 |

||

|

0010021 |

0213022 |

00001000000110 |

00011011000101 |

|

|

7 такт |

||||

|

Мн |

0300222 |

3000000 |

00110000010101 |

11000000000000 |

|

Мт |

0000001 |

00000000000010 |

||

|

0310303 |

3213022 |

00111000110011 |

11011011000101 |

|

![]() До округления: Мн*Мт = 0.0011100011001111

До округления: Мн*Мт = 0.0011100011001111

01

После округления: Мн*Мт = 0.0011100011010000

n-разрядов

Полученный результат: Мн*Мт 2/4 = 0.00111000110100 Р = 0.1011

Мн*Мт 4 = 310330

Мн*Мт 10 = 3387

Результат прямого перемножения операндов: Мн 10 *Мт 10 = 3352,

![]() Абсолютная погрешность: = 3387-3352,53 = 38,47

Абсолютная погрешность: = 3387-3352,53 = 38,47

Относительная погрешность: 1%

3. Разработка структурной схемы

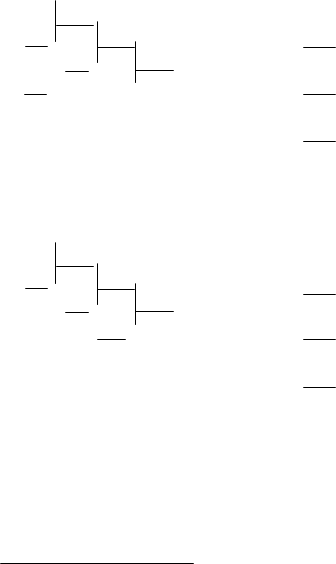

Структурная схема строится на основе следующих блоков

· Многоразрядный регистр сдвига

D1

D1

Q1 сдвиг

Dn

С Qn

S1

S2

“+1”

Предназначен для хранения и сдвига n-разрядного значения числа. Регистр имеет n информационных входов D1 – Dn , управляющий вход разрешения записи в регистр С , управ ляющие входы сдвига содержимого регистра влево S1 и вправо S2 , управляющий вход добавления 1 к содержимому регистра “+1”, выходов Q1- Qn . Все управляющие функции выполняются при поступлении 1 на соответствующий управляющий вход.

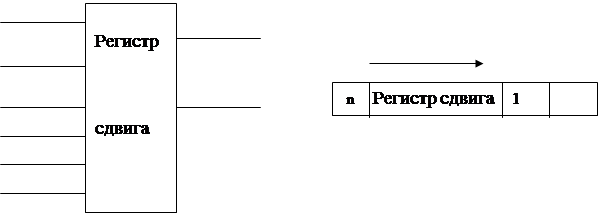

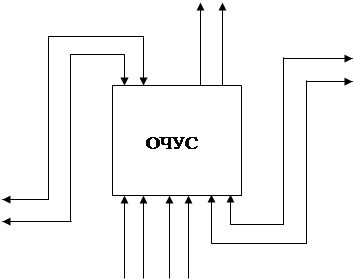

· Одноразрядный четверичный умножитель - сумматор (ОЧУС)

Р3 Р4

P1 P2 Р1’

P2’ от младшего

ОЧУС к старшему

ОЧУС

Х1 Х2 Y1 Y2

ОЧУС предназначен для получения одной четверичной цифры путем перемножения диады множимого (Х1,Х2) и диады множителя (Y1,Y2), и прибавления к полученному результату диады, поступающей в виде переноса от младшего ОЧУС.

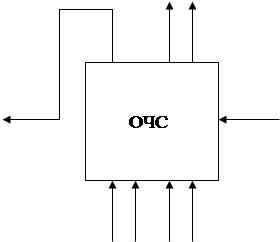

· Одноразрядный четверичный сумматор (ОЧС)

Предназначен для суммирования двух четверичных цифр и прибавления к полученной сумме единицы переноса от предыдущего ОЧС. Формирует единицу переноса в следующий ОЧС.

S1 S2

П Z

P1 P2 P3 P4

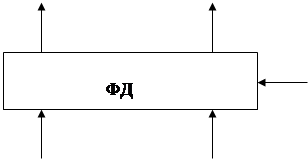

· Многоразрядный формирователь дополнения (ФД).

Предназначен для получения дополнения многоразрядного четверичного числа. ФД имеет n двоичных входов (X1-Xn), n двоичных выходов (Y1-Yn) и управляющий вход f. Если на него подана логическая “1”, то ФД формирует дополнение входного числа.

Yn Y1

Yn Y1

f

Xn X1

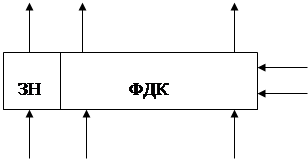

· Многоразрядный формирователь дополнительного кода (ФДК)

Знак Yn Y1

f1

f2

Знак Xn X1

Предназначен для получения дополнительного кода многоразрядного четверичного числа. ФДК имеет n двоичных входов (Х1-Хn), n двоичных выходов (Y1-Yn), отдельный вход для знака преобразуемого числа, а также управляющие входы (f1) и (f2). При подаче управляющего сигнала (“1”) на вход f1 ФДК формирует дополнительный код числа в сооответствии с его знаком. При подаче управляющего сигнала (“1”) на вход f2 ФДК формирует двойной дополнительный код числа.

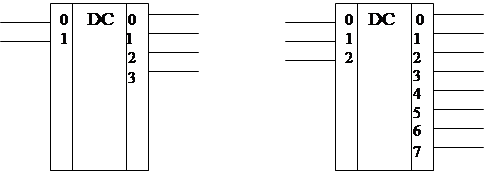

· Дешифраторы 4 из 2-х и 8 из 4-х

D1 Q0 D1 Q0

D2 . D2

. Q4 D3

Qn

Дешифратор предназначен для преобразования двоичного кода на входе в напряжение высокого уровня, появляющееся на том выходе, десятичный номер которого соответсствует двоичному коду на входе.

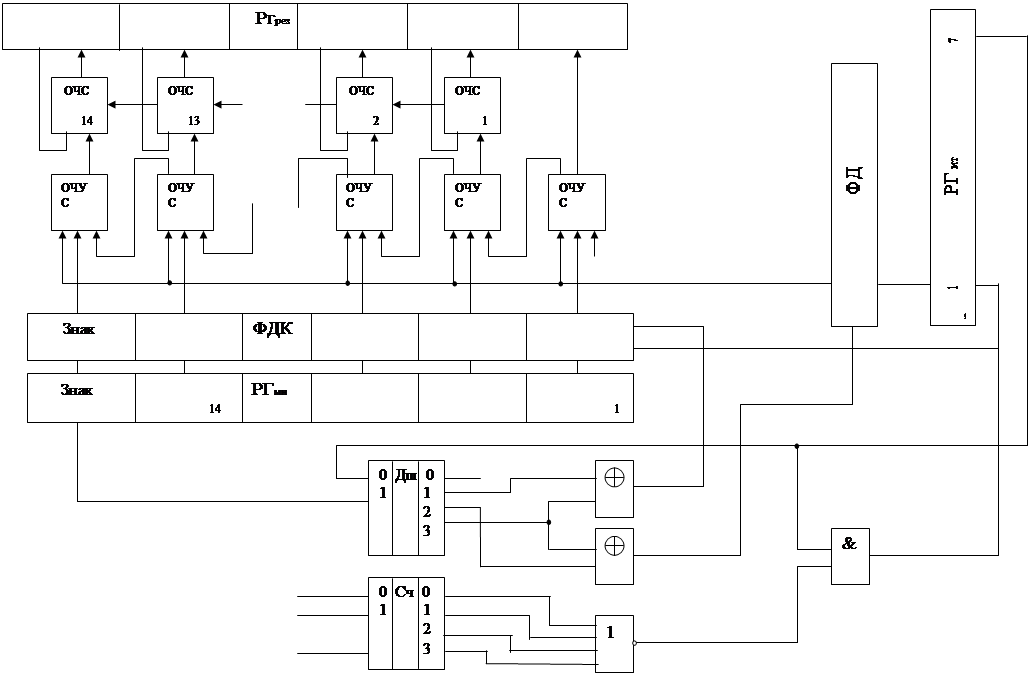

Структурная схема устройства приведена на рис.1. Она содержит регистры: множимого (Рг Мн), множителя (Рг Мт), результата (Рг Рез), формирователи дополнительного кода (ФДК) и дополнения (ФД), 14 блоков ОЧС, 15 блоков ОЧУС, счетчик для подсчета кооличества произведенных операций (Сч), дешифратор (Дш) и цепочка из 3 логических элементов для анализа знаков сомножителей.

Устройство умножения работает следующим образом:

· После записи исходных сомножителей в регистры Рг Мн , Рг Мт, и обнуления Рг Рез дешифратор анализирует знаки сомножителей и формирует соответствующие управляющие сигналы на ФДК и ФД – f1 и f соттветственно. Одновременно происходит запись в счётчик Сч, работающий в режиме обратного счёта, количества тактов.

· С выходов ФД и ФДК на входы ОЧУС поступают по 2 двоичные цифры. Результат операции поступает в ОЧС, где суммируется с содержимым Рг Рез и записывается снова в Рг Рез.

· После проведения этих операций происходит сдвиг Рг Мн , Рг Мт и уменьшение содержимого счетчика Сч путем подачи управляющего сигнала на его вход С.

· После окончания всех операций умножения и суммирования Сч содержит нулевое значение (“0” на всех выходах), которое преобразуется элементом ‘И-НЕ’ в “1”, поступающую на логический элемент ‘И’ . Если знак множителя –отрицательный, то вводится поправка по следующему правилу: если знак множимого положителен, то к произведению, содержащемуся в регистре Рг Рез необходимо прибавить множимое с отрицательным знаком в дополнительном коде, что осуществляется подачей “1” на вход f2 ФДК , записи в Рг Мт единицы и проведения еще одного цикла умножения-сложения, если же знак множимого отрицателен, то в качестве поправки прибавляется положительное множимое, что достигается подачей “1” на вход f2 ФДК (получение двойного дополнительного кода), и, далее, всё как указано выше.

Временные затраты на умножение семиразрядных сомножителей определяются в основном затратами на образование частичных произведений, получаемых на выходах ОЧУС, и примерно равны:

Ту = 7 (tсдв + t ОЧУС + 7 t ОЧС), где t ОЧС - время формирования единицы переноса в ОЧС

t ОЧУС – время умножения на одном ОЧУС

tсдв -время сдвига множимого (множителя)

|

. . . .

. . .

“0”

“1”

f1 f

f2

Рисунок 1.Структурная схема умножителя.

4. Разработка функциональных схем

4.1. Логический синтез ОЧУС

Для синтеза ОЧУС составляется таблица истинности (табл.5), в которой X1Х2 и Y1Y2 соответст- венно Мн и Мт, представленные двоичными эквивалентами, согласно принятому кодированию чет- веричных цифр, P1`P2`-перенос из младшего ОЧУС, P1P2 –перенос в старший ОЧУС, P3P4 –результат операции.

Таблица 5

|

№ |

X1 |

X2 |

Y1 |

Y2 |

P1` |

P2` |

P1 |

P2 |

P3 |

P4 |

н.н |

|

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

|

|

1 |

0 |

0 |

0 |

0 |

0 |

1 |

0 |

0 |

0 |

1 |

|

|

2 |

0 |

0 |

0 |

0 |

1 |

0 |

0 |

0 |

1 |

0 |

|

|

3 |

0 |

0 |

0 |

0 |

1 |

1 |

0 |

0 |

1 |

1 |

* |

|

4 |

0 |

0 |

0 |

1 |

0 |

0 |

0 |

0 |

0 |

0 |

|

|

5 |

0 |

0 |

0 |

1 |

0 |

1 |

0 |

0 |

0 |

1 |

|

|

6 |

0 |

0 |

0 |

1 |

1 |

0 |

0 |

0 |

1 |

0 |

|

|

7 |

0 |

0 |

0 |

1 |

1 |

1 |

0 |

0 |

1 |

1 |

* |

|

8 |

0 |

0 |

1 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

|

|

9 |

0 |

0 |

1 |

0 |

0 |

1 |

0 |

0 |

0 |

1 |

|

|

10 |

0 |

0 |

1 |

0 |

1 |

0 |

0 |

0 |

1 |

0 |

|

|

11 |

0 |

0 |

1 |

0 |

1 |

1 |

0 |

0 |

1 |

1 |

* |

|

12 |

0 |

0 |

1 |

1 |

0 |

0 |

0 |

0 |

0 |

0 |

|

|

13 |

0 |

0 |

1 |

1 |

0 |

1 |

0 |

0 |

0 |

1 |

|

|

14 |

0 |

0 |

1 |

1 |

1 |

0 |

0 |

0 |

1 |

0 |

|

|

15 |

0 |

0 |

1 |

1 |

1 |

1 |

0 |

0 |

1 |

1 |

* |

|

16 |

0 |

1 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

|

|

17 |

0 |

1 |

0 |

0 |

0 |

1 |

0 |

0 |

0 |

1 |

|

|

18 |

0 |

1 |

0 |

0 |

1 |

0 |

0 |

0 |

1 |

0 |

|

|

19 |

0 |

1 |

0 |

0 |

1 |

1 |

0 |

0 |

1 |

1 |

* |

|

20 |

0 |

1 |

0 |

1 |

0 |

0 |

1 |

0 |

0 |

0 |

|

|

21 |

0 |

1 |

0 |

1 |

0 |

1 |

1 |

0 |

0 |

1 |

|

|

22 |

0 |

1 |

0 |

1 |

1 |

0 |

1 |

0 |

1 |

0 |

|

|

23 |

0 |

1 |

0 |

1 |

1 |

1 |

1 |

0 |

1 |

1 |

* |

|

24 |

0 |

1 |

1 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

|

|

25 |

0 |

1 |

1 |

0 |

0 |

1 |

1 |

0 |

0 |

1 |

|

|

26 |

0 |

1 |

1 |

0 |

1 |

0 |

0 |

0 |

1 |

0 |

|

|

27 |

0 |

1 |

1 |

0 |

1 |

1 |

1 |

0 |

1 |

1 |

* |

|

28 |

0 |

1 |

1 |

1 |

0 |

0 |

1 |

0 |

0 |

1 |

|

|

29 |

0 |

1 |

1 |

1 |

0 |

1 |

0 |

1 |

0 |

0 |

|

|

30 |

0 |

1 |

1 |

1 |

1 |

0 |

1 |

0 |

1 |

1 |

|

|

31 |

0 |

1 |

1 |

1 |

1 |

1 |

0 |

1 |

1 |

0 |

* |

|

32 |

1 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

|

|

33 |

1 |

0 |

0 |

0 |

0 |

1 |

0 |

0 |

0 |

1 |

|

|

34 |

1 |

0 |

0 |

0 |

1 |

0 |

0 |

0 |

1 |

0 |

|

|

35 |

1 |

0 |

0 |

0 |

1 |

1 |

0 |

0 |

1 |

1 |

* |

|

36 |

1 |

0 |

0 |

1 |

0 |

0 |

0 |

0 |

1 |

0 |

|

|

37 |

1 |

0 |

0 |

1 |

0 |

1 |

1 |

0 |

0 |

0 |

|

|

38 |

1 |

0 |

0 |

1 |

1 |

0 |

0 |

0 |

1 |

1 |

|

|

39 |

1 |

0 |

0 |

1 |

1 |

1 |

1 |

0 |

1 |

0 |

* |

|

40 |

1 |

0 |

1 |

0 |

0 |

0 |

0 |

0 |

1 |

0 |

|

|

41 |

1 |

0 |

1 |

0 |

0 |

1 |

0 |

0 |

1 |

1 |

|

|

42 |

1 |

0 |

1 |

0 |

1 |

0 |

0 |

0 |

0 |

1 |

|

|

43 |

1 |

0 |

1 |

0 |

1 |

1 |

1 |

0 |

0 |

0 |

* |

|

44 |

1 |

0 |

1 |

1 |

0 |

0 |

0 |

0 |

1 |

1 |

|

|

45 |

1 |

0 |

1 |

1 |

0 |

1 |

1 |

0 |

1 |

0 |

|

|

46 |

1 |

0 |

1 |

1 |

1 |

0 |

1 |

0 |

0 |

0 |

|

|

47 |

1 |

0 |

1 |

1 |

1 |

1 |

1 |

0 |

0 |

1 |

* |

|

48 |

1 |

1 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

|

|

59 |

1 |

1 |

0 |

0 |

0 |

1 |

0 |

0 |

0 |

1 |

|

|

50 |

1 |

1 |

0 |

0 |

1 |

0 |

0 |

0 |

1 |

0 |

|

|

51 |

1 |

1 |

0 |

0 |

1 |

1 |

0 |

0 |

1 |

1 |

* |

|

52 |

1 |

1 |

0 |

1 |

0 |

0 |

1 |

0 |

0 |

1 |

|

|

53 |

1 |

1 |

0 |

1 |

0 |

1 |

0 |

1 |

0 |

0 |

|

|

54 |

1 |

1 |

0 |

1 |

1 |

0 |

1 |

0 |

1 |

1 |

|

|

55 |

1 |

1 |

0 |

1 |

1 |

1 |

0 |

1 |

1 |

0 |

* |

|

56 |

1 |

1 |

1 |

0 |

0 |

0 |

0 |

0 |

1 |

1 |

|

|

57 |

1 |

1 |

1 |

0 |

0 |

1 |

1 |

0 |

1 |

0 |

|

|

58 |

1 |

1 |

1 |

0 |

1 |

0 |

1 |

0 |

0 |

0 |

|

|

59 |

1 |

1 |

1 |

0 |

1 |

1 |

1 |

0 |

0 |

1 |

* |

|

60 |

1 |

1 |

1 |

1 |

0 |

0 |

0 |

1 |

1 |

0 |

|

|

61 |

1 |

1 |

1 |

1 |

0 |

1 |

0 |

1 |

1 |

1 |

|

|

62 |

1 |

1 |

1 |

1 |

1 |

0 |

0 |

1 |

0 |

1 |

|

|

63 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

0 |

0 |

* |

Минимизация функции Р1

|

1 |

|||||||

|

* |

* |

1 |

1 |

* |

* |

||

|

* |

* |

* |

* |

1 |

|||

|

1 |

1 |

1 |

1 |

1 |

1 |

||

|

1 |

|||||||

|

1 |

* |

* |

1 |

* |

* |

||

|

* |

* |

* |

* |

||||

Минимальное покрытие Cmin = 10111X, 11101X, 0101XX, 01X1X0, X101X0, X110X1, 10X1X1.

Или после преобразований и приведению к виду входных переменных

Уважаемый посетитель!

Чтобы распечатать файл, скачайте его (в формате Word).

Ссылка на скачивание - внизу страницы.