Санкт-Петербургский Государственный Политехнический Университет

_____________________________________________________________________________

Факультет Технической Кибернетики

Кафедра Автоматики и Вычислительной Техники

Отчет

по лабораторной

Триггеры

Схемотехника

Работу выполнил:

группа 3081/1

Работу принял:

Подпись преподавателя:___________________

Санкт-Петербург

2009

1. Цель работы:

· закрепить знания характеристик и режимов работы триггеров основных типов;

· получить практические навыки тестирования и управления триггерами;

· получить навыки ввода проекта в графическом редакторе пакета Quartus II, тестирования и отладки проекта и анализа временных характеристик триггеров;

· получить навыки отладки цифровых устройств данного класса на физической модели: конфигурировать СБИС ПЛ и экспериментально проверить работу типовых устройств с триггерами при использовании лабораторной платы DiLab.

2. Выполнение работы:

2.1 Асинхронный RS-триггер

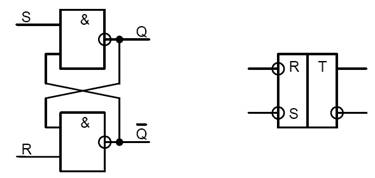

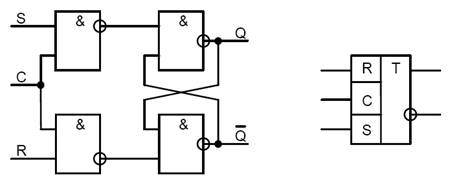

Рис 2.1.1 Функциональная схема и условное изображение асинхронного RS-триггера

Таблица 2.1 Переходы асинхронного RS-триггера

|

Дискретное время |

Входные переменные |

Состояния |

Режим работы |

||

|

t |

S |

R |

Q |

nQ |

|

|

0. |

0 |

1 |

1 |

0 |

Установка 1 |

|

|

1 |

1 |

1 |

0 |

Хранение 1 |

|

|

1 |

0 |

0 |

1 |

Установка 0 |

|

|

1 |

1 |

0 |

1 |

Хранение 0 |

|

|

0 |

1 |

1 |

0 |

Установка 1 |

|

|

0 |

0 |

1 |

1 |

Особое состояние |

|

|

1 |

0 |

0 |

1 |

Установка 0 |

|

|

0 |

0 |

1 |

1 |

Особое состояние |

|

|

0 |

1 |

1 |

0 |

Установка 1 |

Моделирование в САПР Quartus II:

Рис 2.1.2 Block Diagram/Schematic File

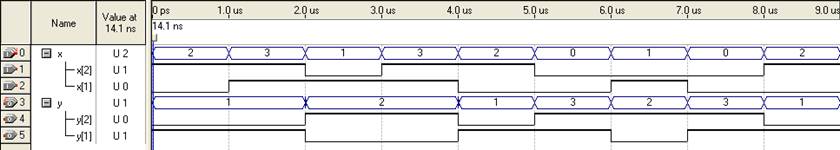

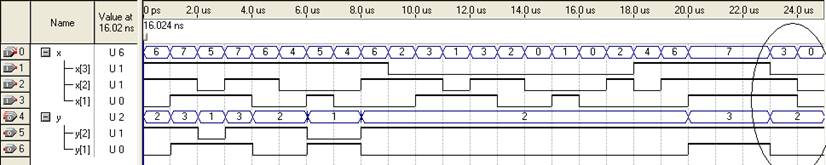

Рис 2.1.3 Vector Waveform File

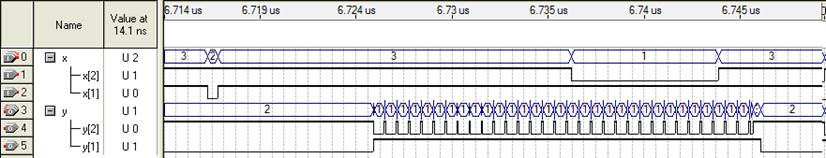

Рис 2.1.3 Режим генерации (при подаче коротких (порядка долей нс) импульсов на вход S)

Устройство переходит в режим генерации при подаче на вход S 250псек и меньше.

2.2 RS-триггер, синхронизируемый уровнем

Рис 2.2.1 Функциональная схема и условное изображение RS-триггера, синхронизируемого уровнем

Таблица 2.2 Переходы RS-триггера, синхронизируемого уровнем

|

Уровень |

Входные переменные |

Состояния |

||

|

С |

S |

R |

Q |

nQ |

|

0 |

х |

х |

Q |

nQ |

|

1 |

0 |

0 |

Q |

nQ |

|

1 |

0 |

1 |

0 |

1 |

|

1 |

1 |

0 |

1 |

0 |

|

1 |

1 |

1 |

1 |

1 |

Моделирование в САПР Quartus II:

Рис 2.2.2 BlockDiagram/SchematicFile

Сначала рассмотрим триггер без задержки между элементами:

Рис 2.2.3 VectorWaveformFile

При отсутствии задержки триггер из особого состояния переходит в устойчивое состояние хранения 0. (см. рис 2.2.3: спад на С при R=S=1)

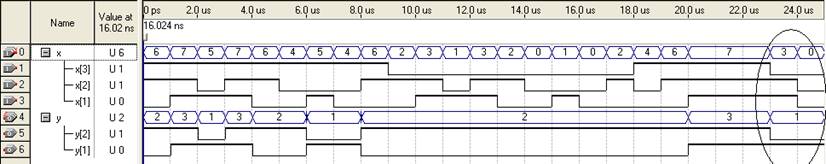

Теперь добавим задержку между логическими элементами (рис.2.2.2):

Рис 2.2.4 VectorWaveformFile

При наличии задержки триггер из особого состояния переходит в устойчивое состояние хранения 1.

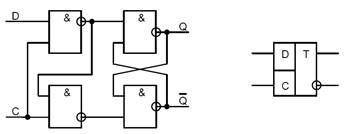

2.3 D-триггер, синхронизируемый уровнем

Рис 2.3.1 Функциональная схема и условное изображение D-триггера, синхронизируемого уровнем

Уважаемый посетитель!

Чтобы распечатать файл, скачайте его (в формате Word).

Ссылка на скачивание - внизу страницы.