Таблица 2.3 Переходы D-триггера, синхронизируемого уровнем

|

Уровень |

Входные перем. |

Состояния |

|

|

C |

D |

Q |

nQ |

|

0 |

0 |

x |

x |

|

1 |

0 |

0 |

1 |

|

0 |

1 |

1 |

0 |

|

1 |

1 |

1 |

0 |

Моделирование в САПР Quartus II:

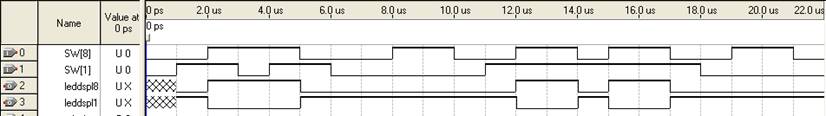

Рис 2.3.2 Block Diagram/Schematic File

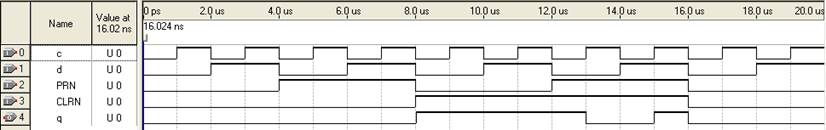

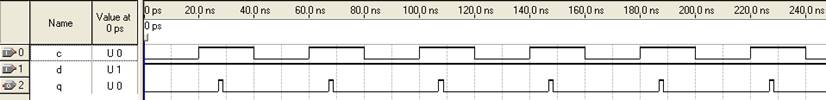

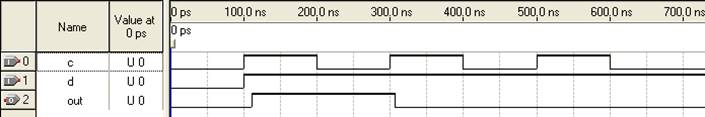

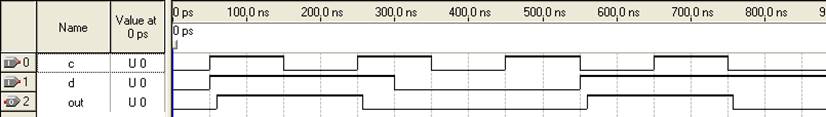

Рис 2.3.3 Vector Waveform File

2.4 Примитивы DFFE и JKFFE

Рис 2.4.1 D-триггер с входом разрешения работы

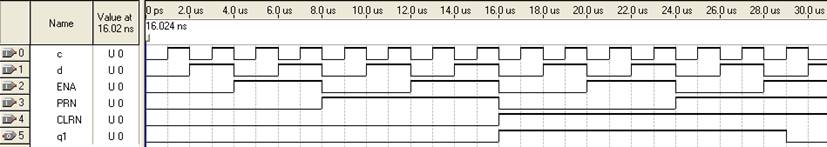

CLK - синхровод, D - информационный вход, PRN - вход асинхронной установки, CLRN - вход асинхронного сброса (последние два – инверсные, т.е. имеют активный уровень 0), ENA - дополнительный управляющий вход (при подаче 1 триггер работает в обычном режиме, при подаче 0 синхронные команды смены состояния блокируются).

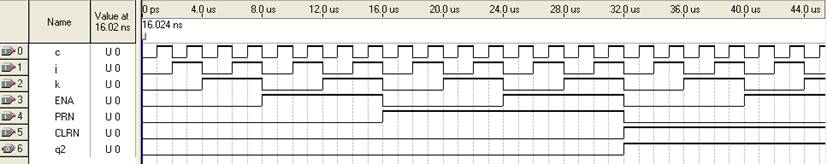

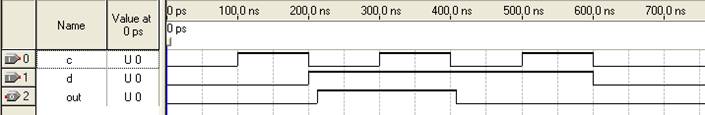

Рис 2.4.2 Vector Waveform File

Рис 2.4.3 JK-триггер с входом разрешения работы

Рис 2.4.4 Vector Waveform File

2.5 DFF-триггер

Рис 2.5.1 D-триггер с входом разрешения работы

Рис 2.5.2 VectorWaveformFile

2.6 Генератор коротких импульсов (на основе DFF-триггера)

Генератор коротких импульсов создается на основе DFF-триггера путем соединения через инвертор выход триггера с одним из асинхронных входов и подачей на вход D константу. Данное устройство по приходу очередного синхроимпульса синхронно переключается в противоположное начальному состояние, а затем, за счет обратной связи, быстро переключается обратно.

Рис 2.6.1 Генератор коротких импульсов

Рис 2.6.2 VectorWaveformFile

Длина импульса 775 псек, если увеличить задержку (добавить элементы LCELL), то длина импульса увеличится до 1,35 нсек.

2.7 Устройство удвоения частоты

Устройство удвоения частоты получается путем объединения двух устройств формирования коротких импульсов так, чтобы одно из устройств формировало импульс при положительном перепаде на входе, а другое – при отрицательном.

Рис 2.7.1 Устройство удвоения частоты

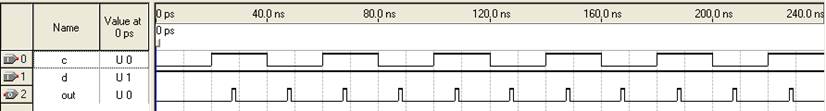

Рис 2.7.2 VectorWaveformFile

Из рисунка видно, что импульсы генерируются с частотой, вдвое большей, чем на рис. 2.5.2 при обычном генераторе коротких импульсов.

2.8 Устройство выявления фронта

Рис 2.8.1 Устройство выявления фронта

Данное устройство должно формировать единичный импульс длительностью в 1 такт при положительном перепаде на его входе.

Рис 2.8.2 VectorWaveformFile

2.9 Устройство выявления спада

Рис 2.9.1 Устройство выявления спада

Рис 2.9.2 VectorWaveformFile

Устройство формирует единичный импульс длительностью в 1 такт при отрицательном перепаде на его входе.

2.10 Устройство выявления фронта и спада

Рис 2.10.1 Устройство выявления фронта и спада

Рис 2.10.2 VectorWaveformFile

Устройство формирует единичный импульс длительностью в 1 такт при положительном и отрицательном перепадах на его входе.

В самом начале работы был исследован асинхронный RS-триггер (элементарная ячейка памяти). Он является основой всех триггерных устройств. В RS-триггер производится парафазная запись, т.е. сигналы подаются на входы R и S. Временная диаграмма работы триггера была построена по экспериментальным данным, которые совпадают с теоретическими (проверены по таблице переходов).

В D-триггер производится однофазная запись. В работе был рассмотрен D-триггер, синхронизируемый уровнем. Если C=0, никакое изменения состояния D не влияет на состояние триггера. При C=1 происходит установка триггера, и ведет он себя в течение этого интервала времени как асинхронный триггер, т.е. изменения сигналов на входе сразу же вызывают соответствующие изменения состояний выхода.

На временных диаграммах работы примитивов DFFE и JKFFE видна приоритетность асинхронных входов перед синхронными.

В работе также были исследованы генератор коротких импульсов, устройство удвоения частоты, устройство выявления фронта/спада, созданные с помощью примитива DFF и цепей обратной связи.

Уважаемый посетитель!

Чтобы распечатать файл, скачайте его (в формате Word).

Ссылка на скачивание - внизу страницы.