Санкт-Петербургский Государственный политехнический университет

Кафедра автоматики и вычислительной техники

Лабораторная работа №4

«Исследование счетчиков»

Выполнил

3081/4

Проверил

Санкт-Петербург, 2009

Цель работы

Исследование счетчиков, построенных по различной архитектуре, и типовых функциональных устройств с их использованием.

Выполнение работы

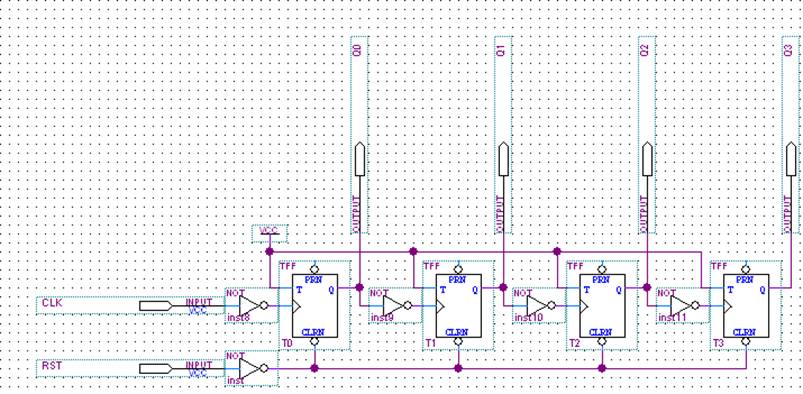

Счетчик с последовательным переносом:

Аппаратурные затраты составили четыре

логических элемента. альная тактовая частота — 360,10 Мгц. Задержка

между перепадом на входе и сигналом на выходе — до 11,165 нс.

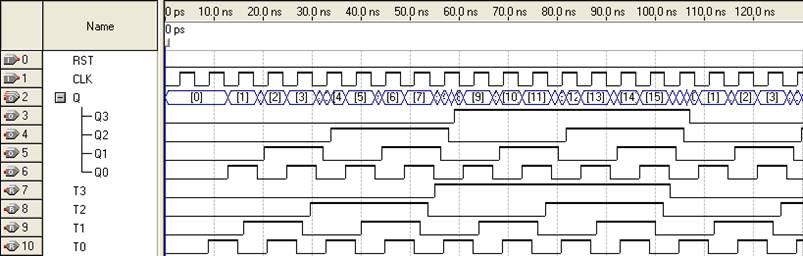

Моделирование его работы:

Реальная задержка для самого медленного выхода

(старшего разряда) — порядка 8,2 нс. Наибольшая разница в tco (между младшим и старшим разрядом) — 4,2 нс. Тогда

время, в течение которого для заданного периода (6 нс) на выходах сигналы

относятся к одному коду (в худшем случае, то есть, при смене всех разрядов) —

1,8 нс.

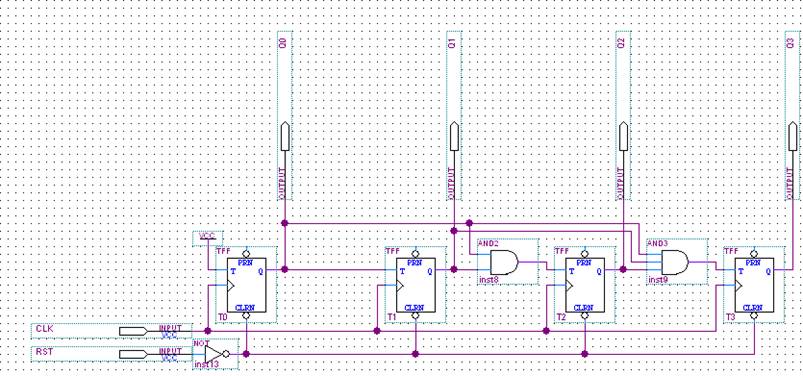

Счетчик с параллельным переносом:

Аппаратурные затраты — 4 логических

элемента. Ограничение тактовой частоты — 340,02 МГц. альное время

задержки — 8,002 нс.

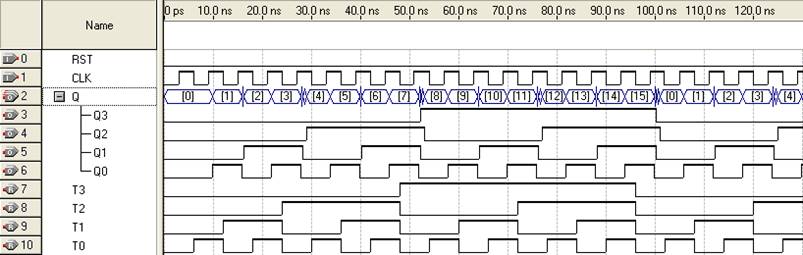

Исследование на модели:

Разница между самым быстрым и самым медленным

изменением сигнала (здесь это нулевой и второй разряды соответственно) — 1,1

нс.

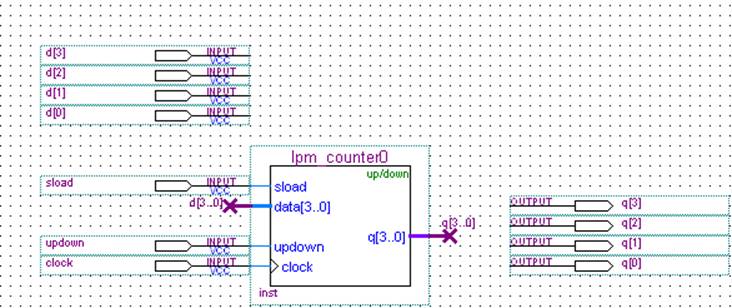

Счетчик, реализованный с помощью мегафункции LPM_COUNTER:

Для этого счетчика быстродействие

ограничено 340,02 МГц, аппаратурные затраты составляют все те же четыре

элемента, наибольшее tco

– 10,037 нс.

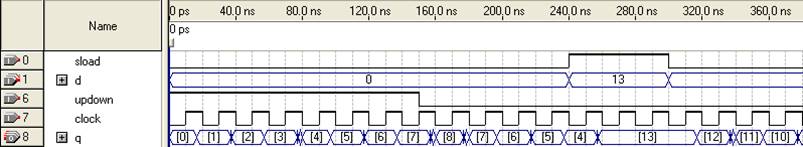

Временная диаграмма:

На ней видно, что при направлении

изменения счета сохраняется состояние (а также то, что для сигнала up/down существует некое время удержания, так как при

совпадении фронта синхроимпульса с моментом переключения режима счетчик еще

срабатывает на сложение). При синхронной загрузке счетчик начинает работу

только после исчезновения активного уровня на входе sload.

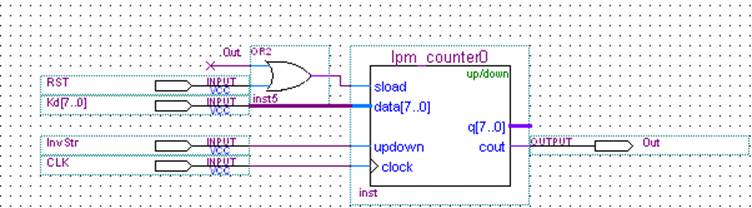

Делитель частоты:

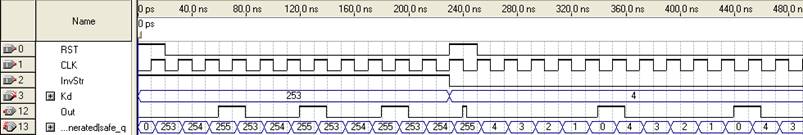

Его моделирование:

Видно, что при работе в режиме сложения выполняется

равенство Кд = 256 − data[] (период

выходного сигнала равен трем периодам синхросигнала, а на информационный вход

подается 253), а в режиме вычитания — Кд = data[] + 1 (5 = 4 + 1).

Дребезг контактов перключателя SW:

|

Переключение |

Количество импульсов (по модулю 256) |

|

0→1 |

31 |

|

1→0 |

10 |

|

0→1 |

237 |

|

1→0 |

3 |

|

0→1 |

3 |

|

1→0 |

12 |

|

0→1 |

15 |

|

1→0 |

3 |

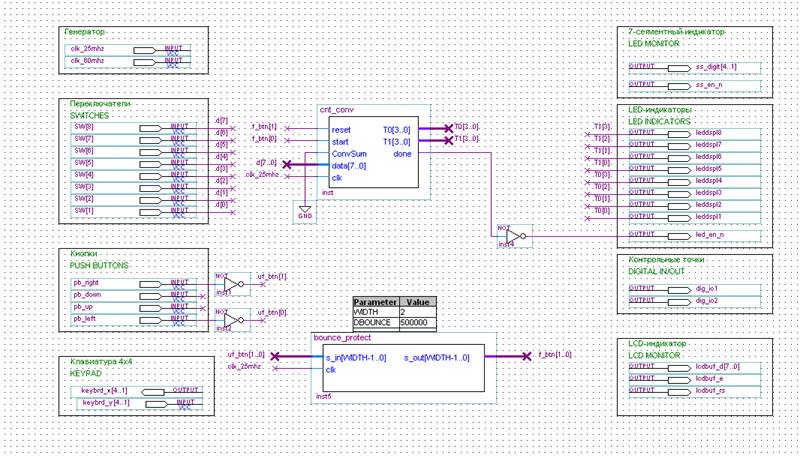

Устройство фильтрации коротких импульсов, подключенное к переключателю SW1:

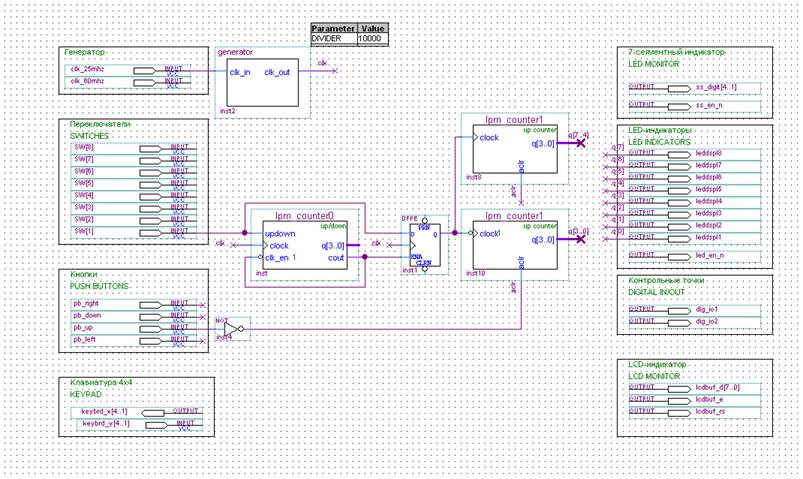

Непосредственно устройство состоит из

триггера и четырехразрядного счетчика, на который поступает синхросигнал,

поданный через делитель частоты (счетчик большой разрядности). К выходу фильтра

подключены еще два счетчика, один из которых выводит на светодиоды количество

фронтов выходного сигнала, а второй — спадов. По результатам эксперимента было

установлено, что схема действительно выдает непрерывное значение, изменяющееся

при смене положения переключателя лишь однократно.

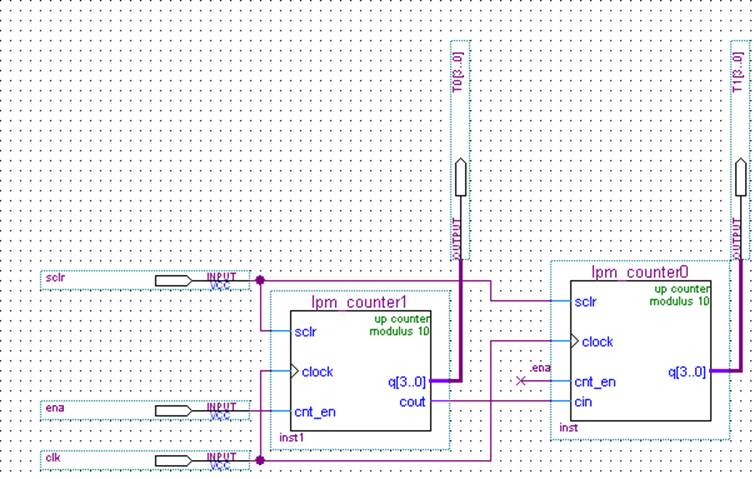

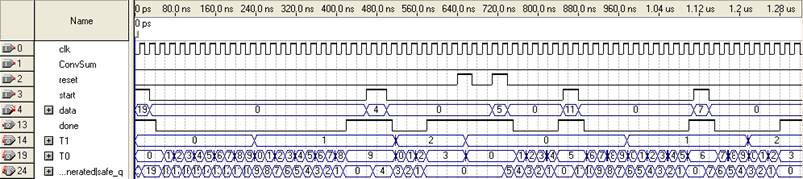

Двухтетрадный двоично-десятичный счетчик:

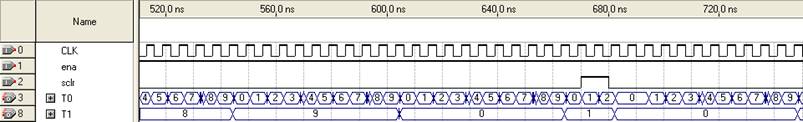

Временная диаграмма работы:

Она иллюстрирует то, что переключение

старшего разряда действительно происходит при смене максимального значения

младшего — девяти — на ноль, и то, что старший ограничен тем же значением.

Также присутствует проверка работы входа обнуления.

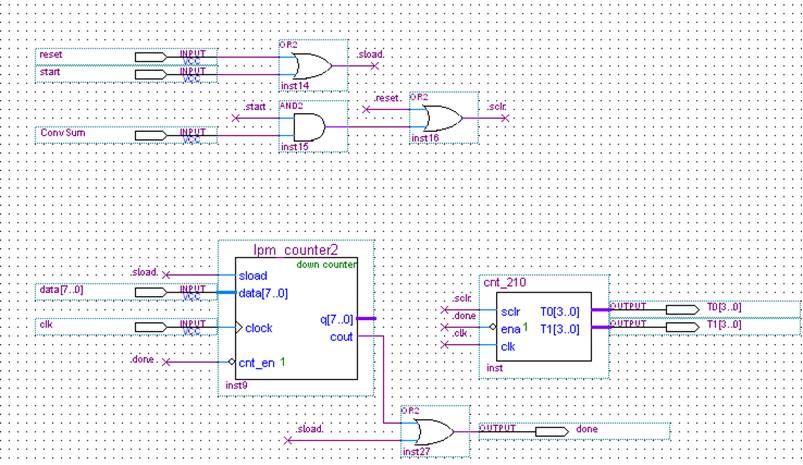

Схема преобразования двоичного кода в двоично-десятичный:

Схема может работать и в режиме

накапливающего сумматора, для чего введен вход Conv/Sum.

(Можно было не вводить четкого разделения режимов, а для функционирования как

преобразователя каждый раз подавать сигнал сброса, однако отдельный вход

однозначно различает варианты использования, для которых в работе предполагается

раздельное исследование.)

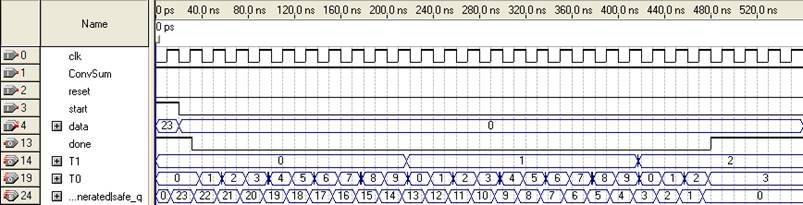

Работа преобразователя:

Первая диаграмма демонстрирует штатное

функционирование, вторая показывает, что приход нового сигнала в то время,

когда еще не закончен пересчет старого значения, не приводит к отклонениям в

работе схемы.

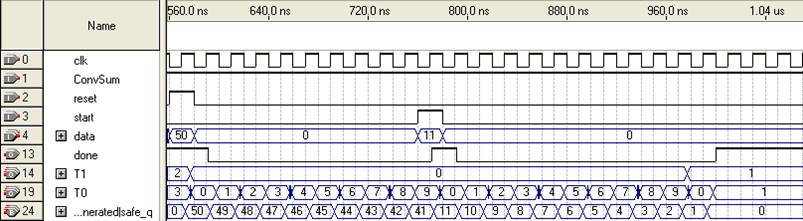

Работа накапливающего сумматора:

Функционирование сумматора проверено на стенде:

Двоичный код задается на переключателях SW[8..1], запуск сложения (возможно, с первоначальным

обнулением) производится с помощью кнопок, подключенных через схему защиты от

дребезга. Четверки светодиодов служат индикатором значения соответствующей

тетрады.

Выводы

Счетчики являются устройствами с обширной функциональностью, на базе которых могут быть реализованы схемы весьма разнообразного назначения. Из рассмотренных в работе архитектур счетчики с последовательным переносом показали несколько большее быстродействие, чем с параллельным (360 МГц против 340 МГц), однако из-за того, что каждый следующий разряд требует переключения предыдущего триггера, такие счетчики демонстрируют большее время задержки (11,2 нс, у последовательных — 8,0 нс), а главное — бóльшую разницу между задержками различных триггеров, существенно сокращая время, в течение которого на выходах может быть получен корректный сигнал (при периоде в 6 нс — 1,8 нс против 4,9 нс). Аппаратурные затраты при реализации на заданной микросхеме оказались одинаковыми для обеих архитектур (четыре элемента). Такими же они остались и при использовании готовой мегафункции LPM_COUNTER. Быстродействие такого счетчика совпадает с ручной реализацией с параллельным переносом (340 МГц), tco лежит между рассмотренными архитектурами (10,0 нс). При этом счетчик, синтезированный средствами Quartus II не требует ввода схемы и предоставляет больший набор функций.

Уважаемый посетитель!

Чтобы распечатать файл, скачайте его (в формате Word).

Ссылка на скачивание - внизу страницы.