Санкт-Петербургский государственный политехнический университет

Факультет технической кибернетики

Кафедра автоматики и вычислительной техники

Отчет по лабораторной работе №4

(Учебная дисциплина «Автоматизации проектирования дискретных устройств»)

Работу выполнил студент группы №3081/2

Работу принял преподаватель___________

Санкт-Петербург

2010

1. Последовательное умножающее устройство.

Устройство работает по алгоритму умножения младшими разрядами вперед со сдвигом частичной суммы.

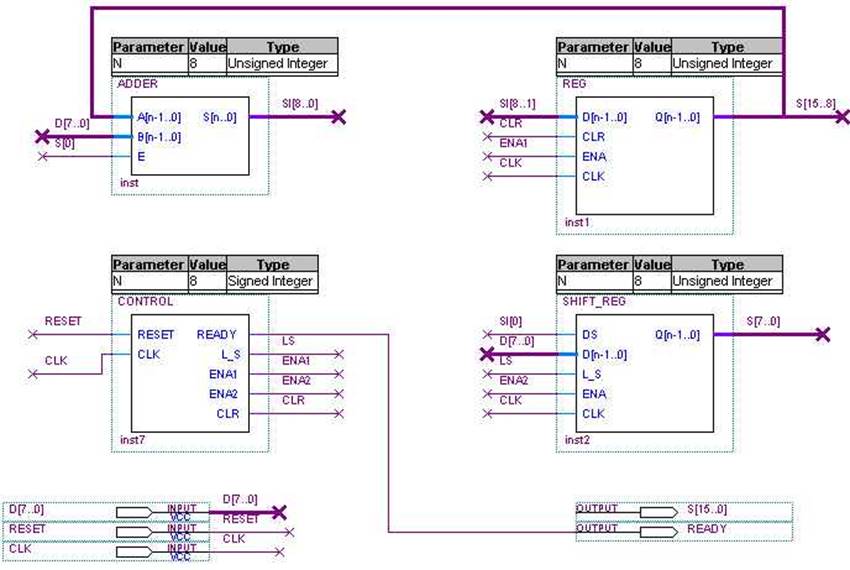

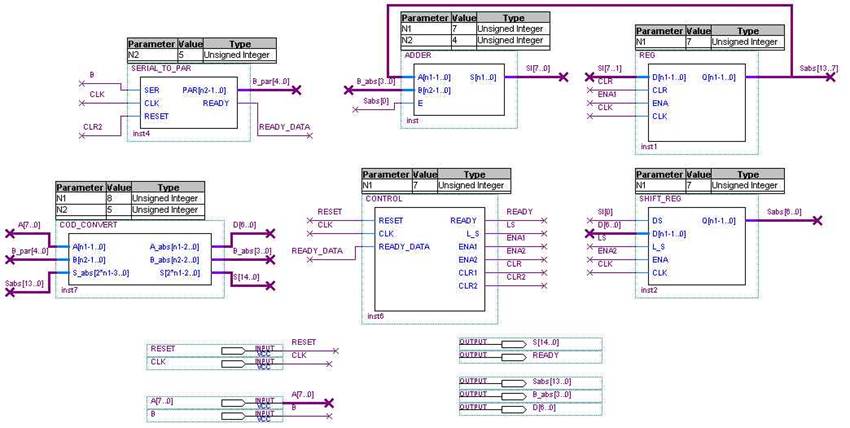

Схема устройства умножения двух чисел разрядности N = 8 изображена на следующем рисунке.

рис.1.1. Схема умножающего

устройства.

Сумматор ADDER осуществляет в зависимости от S[0] либо сложение операндов , либо передачу А на выход устройства.

В регистрах REG и SHIFT_REG накапливается сумма частичных произведений.

Сдвиг частичной суммы производится структурно — с выхода сумматора ADDER младший бит идет на SHIFT_REG, а остальные биты на REG.

Блок CONTROL осуществляет установку начальных условий и выдает определенные управляющие сигналы на остальные устройства, для выполнения алгоритма.

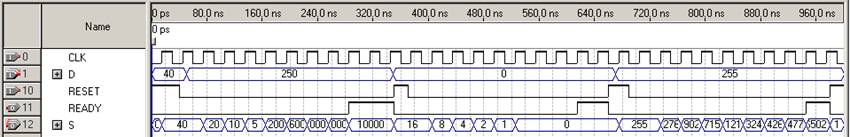

Временная диаграмма работы такого устройства:

Рис. 1.2. Временная

диаграмма работы последовательного умножителя.

Данные для умножения подаются оба по шине D. Сначала 1й операнд в регистр SHIFT_REG, когда RESET = 1 и SHIFT_REG находится в режиме загрузки, когда RESET = 0, то подается 2й операнд и он идет на вход B сумматора ADDER.

READY = 1 говорит о том, что результат на шине S готов.

2. Последовательное умножающее устройство. Индивидуальное задание.

Задание:

|

Разр. A |

Разр. B |

Код A |

Код B |

Код S |

Порт A |

Порт B |

|

8 |

5 |

прям |

обр |

доп |

пар |

посл |

Устройство отличается от описанного в 1ом пункте тем, что предназначено для умножения чисел со знаком, с заданной разрядность и представленных в опрпделенных кодах.

Схема разработанного устройства:

рис.2.1. Схема умножающего

устройства для чисел со знаком.

Это устройство представляет собой последовательный умножитель из пункта 1, в который добавлены еще 2 блока — COD_CONVERT и SERIAL_TO_PAR.

SERIAL_TO_PAR, преобразует число B из последовательного кода в параллельный, и выдает сигнал готовности данных для умножения на блок CONTROL.

COD_CONVERT выделяет модули операндов и анализирует их знаки, также осуществляет преобразование результата в требуемый код.

Остальные блоки абсолютно аналогичны блокам устройства из пункта 1. У них только изменена разрядность чисел с которыми производится работа с помощью настраиваемых параметров.

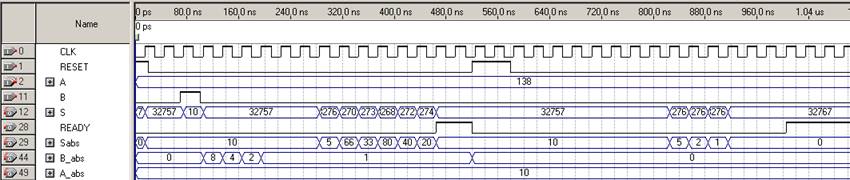

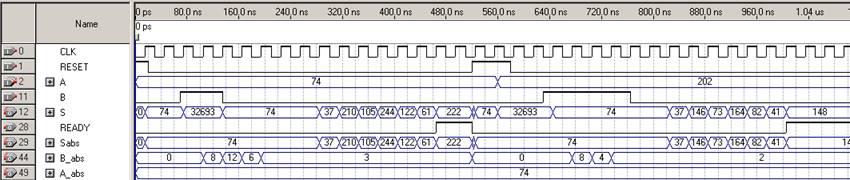

Диаграммы работы такого устройства. На диаграммах представлены различные варианты — умножение чисел с одинаковыми и разными знаками, получение в результате умножения на ноль положительного и отрицательного нуля (обратный код).

Рис. 2.2. Временная диаграмма

работы последовательного умножителя чисел со знаком.

Первое умножение — B = 1, A = -10(138 прямом коде), результат S = 32757 (-10 в обратном коде).

Второе умножение — B = 0, A = -10(138 прямом коде), результат S = 32767 — отрицательный ноль.

Рис. 2.3. Временная диаграмма

работы последовательного умножителя чисел со знаком.

Первое умножение — B = 3, A = 74, результат S = 222.

Второе умножение — B = -2 (30 в дополнительном коде), A = -74 (202 прямом коде), результат S = 146 положительное число в обратном коде.

Все блоки устройства описаны на VHDL. Исходный код, и синтезируемые в результате компиляции схемы для всех блоков.

Листинг 1. ADDER.vhd.

LIBRARY IEEE;

USE IEEE.std_logic_1164.all;

ENTITY ADDER is

generic(

N1 : integer := 7;

N2 : integer := 4

);

port(

A : in std_logic_vector(N1-1 downto 0);

B : in std_logic_vector(N2-1 downto 0);

E : in std_logic;

S : out std_logic_vector(N1 downto 0)

);

END ADDER;

ARCHITECTURE ADDER_arch of ADDER is

signal tmp : std_logic_vector (N1-1 downto N2);

BEGIN

tmp <= (others => '0');

with E select

S(N1 downto 0) <=

('0' & A(N1-1 downto 0) ) when '0',

(tmp & B(N2-1 downto 0)) + ('0'&A(N1-1 downto 0)) when '1';

END ADDER_arch;

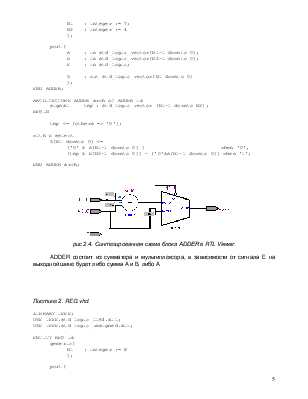

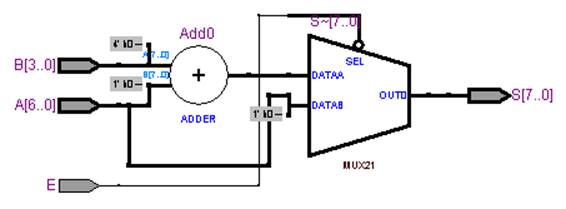

рис 2.4. Синтезированная схема

блока ADDER

вRTL Viewer.

ADDER состоит из сумматора и мультиплексора, в зависимости от сигнала E на выходной шине будет либо сумма A и B, либо A.

Листинг 2. REG.vhd.

LIBRARY IEEE;

USE IEEE.std_logic_1164.all;

USE IEEE.std_logic_unsigned.all;

ENTITY REG is

generic(

N1 : integer := 8

);

port(

D : in std_logic_vector (N1-1 downto 0);

CLR : in std_logic;

ENA : in std_logic;

CLK : in std_logic;

Q : out std_logic_vector (N1-1 downto 0)

);

END REG;

ARCHITECTURE REG_arch of REG is

Уважаемый посетитель!

Чтобы распечатать файл, скачайте его (в формате Word).

Ссылка на скачивание - внизу страницы.