BEGIN

PROCESS (CLR, ENA, CLK)

BEGIN

if (CLR = '1') then

Q <= (others => '0');

elsif (ENA = '0') then

null;

elsif (CLK'event) and (CLK = '1') then

Q <= D;

end if;

END PROCESS;

END REG_arch;

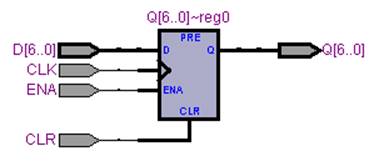

рис 2.5. Синтезированная схема блока REG вRTL Viewer.

Видно, что блок REG представляет собой регистр с асинхронным сбросом, через который по RESET осуществляется установка начальных условий, и разрешением работы.

Листинг 3. SHIFT_REG.vhd.

LIBRARY IEEE;

USE IEEE.std_logic_1164.all;

ENTITY SHIFT_REG is

generic(

N1 : integer := 8

);

port(

DS : in std_logic;

D : in std_logic_vector (N1-1 downto 0);

L_S : in std_logic;

ENA : in std_logic;

CLK : in std_logic;

Q : out std_logic_vector (N1-1 downto 0)

);

END SHIFT_REG;

ARCHITECTURE SHIFT_REG_arch of SHIFT_REG is

signal RG_sh : std_logic_vector (N1-1 downto 0);

BEGIN

Q <= RG_sh;

PROCESS (ENA,CLK)

BEGIN

if (CLK'event) and (CLK = '1') then

if (L_S = '1') then

if (ENA = '0') then RG_sh <= RG_sh;

else RG_sh <= DS & RG_sh(N1-1 downto 1);

end if;

else RG_sh <= D;

end if;

end if;

END PROCESS;

END SHIFT_REG_arch;

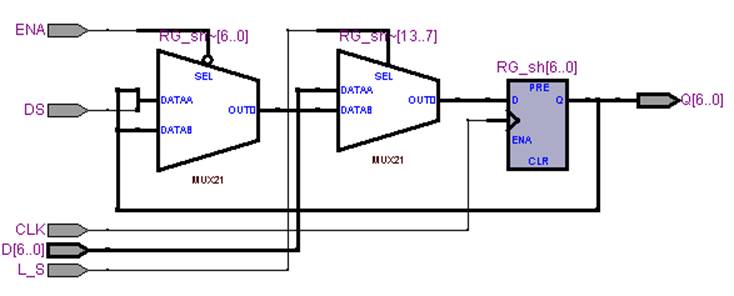

рис 2.6.

Синтезированная схема блока SHIFT_REG в RTL Viewer.

Видно, что блок SHIFT_REG представляет собой регистр c параллельной и последовательной загрузкой. D[] - вход для параллельной загрузки, DS — вход для последовательной загрузки.

Листинг 4. CONTROL.vhd.

ENTITY CONTROL is

generic(

N1 : integer := 8

);

port(

RESET : in std_logic;

CLK : in std_logic;

READY_DATA : in std_logic;

READY : out std_logic;

L_S : out std_logic;

ENA1 : out std_logic;

ENA2 : out std_logic;

CLR1 : out std_logic;

CLR2 : out std_logic

);

END CONTROL;

ARCHITECTURE CONTROL_arch of CONTROL is

signal READYtemp : std_logic;

BEGIN

READY <= READYtemp;

PROCESS (RESET, CLK)

variable i : integer range 0 to N1;

variable j : integer range 0 to 6;

BEGIN

if (RESET = '1') then

CLR1 <= '1';

CLR2 <= '1';

L_S <= '0';

ENA1 <= '0';

ENA2 <= '0';

READYtemp <= '0';

i := 0;

else

L_S <= '1';

if (CLK'event) and (CLK = '1') then

CLR1 <= '0';

CLR2 <= '0';

if (READY_DATA = '1') then

ENA1 <= '1';

ENA2 <= '1';

if (i = N1) then

READYtemp <='1';

L_S <= '1';

ENA1 <= '0';

ENA2 <= '0';

end if;

i := i + 1;

end if;

end if;

end if;

END PROCESS;

END CONTROL_arch;

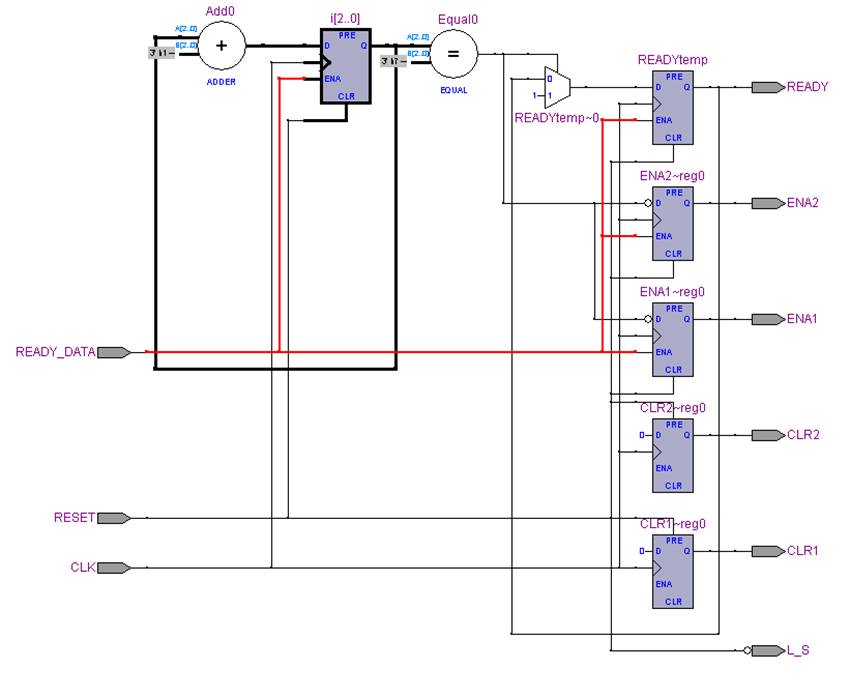

рис 2.7.

Синтезированная схема блока CONTROL в RTL Viewer.

Блок CONTROL выполняет установку начальных условий перед началом умножения, и выдачу управляющих сигналов на остальные блоки устройства. Когда готов результат, то формируется сигнал READY. Для этого в блоке CONTROL есть счетчик который отсчитывает число сдвигов которые необходимо сделать.

Листинг 5. SERIAL_TO_PAR.vhd.

LIBRARY IEEE;

USE IEEE.std_logic_1164.all;

ENTITY SERIAL_TO_PAR is

generic(

N2 : integer := 5

);

port(

SER : in std_logic;

CLK : in std_logic;

RESET : in std_logic;

PAR : out std_logic_vector (N2-1 downto 0);

READY : out std_logic

);

END SERIAL_TO_PAR;

ARCHITECTURE SERIAL_TO_PAR_arch of SERIAL_TO_PAR is

signal count_val : integer range 0 to N2;

signal READYtemp : std_logic;

signal PARtemp : std_logic_vector (N2-1 downto 0);

BEGIN

READY <= READYtemp;

PAR <= PARtemp;

PROCESS (CLK)

BEGIN

if (RESET = '1') then

PARtemp <= (others => '0');

READYtemp <= '0';

elsif (CLK'event) and (CLK = '1') then

if (count_val /= N2) then

count_val <= count_val + 1;

PARtemp <= SER & PARtemp(N2-1 downto 1);

else

READYtemp <= '1';

count_val <= 0;

end if;

if (READYtemp = '1') then

count_val <= count_val;

PARtemp <= PARtemp;

end if;

end if;

END PROCESS;

END SERIAL_TO_PAR_arch;

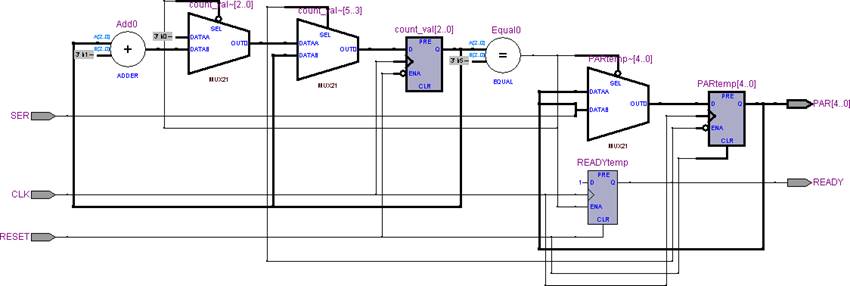

рис 2.8. Синтезированная схема блока

SERIAL_TO_PAR в RTL Viewer.

Листинг 6. COD_CONVERT.vhd.

LIBRARY IEEE;

USE IEEE.std_logic_1164.all;

ENTITY COD_CONVERT is

generic(

N1 : integer := 8;

N2 : integer := 5

);

port(

A : in std_logic_vector(N1-1 downto 0);

B : in std_logic_vector(N2-1 downto 0);

S_abs : in std_logic_vector(2*N1-3 downto 0);

A_abs : out std_logic_vector(N1-2 downto 0);

B_abs : out std_logic_vector(N2-2 downto 0);

S : out std_logic_vector(2*N1-2 downto 0)

);

END COD_CONVERT;

ARCHITECTURE COD_CONVERT_arch of COD_CONVERT is

signal SIGN : std_logic;

BEGIN

A_abs <= A(N1-2 downto 0);

SIGN <= A(N1-1) xor B(N2-1);

S(2*N1-2) <= SIGN;

with B(N2-1) select

B_abs <=

not( B(N2-2 downto 0) ) + '1' when '1',

B(N2-2 downto 0) when '0';

with SIGN select

Уважаемый посетитель!

Чтобы распечатать файл, скачайте его (в формате Word).

Ссылка на скачивание - внизу страницы.