Блок ИУВВ предназначен для ввода в МПС сигналов цифровых и аналоговых датчиков и вывода цифровых и аналогового сигналов управления.

Входными для ИУВВ являются: сигналы цифровых датчиков X1, X2, X3, X4; сигналы аналоговых датчиков X5, X6, X7; цифровой эквивалент, передаваемый на шину данных МПС D0-D7;

Выходными для ИУВВ являются: цифровые управляющие сигналы Y1, Y2, Y3; аналоговый управляющий сигнал Y4; цифровой эквивалент, принимаемый с шины данных МПС D0-D7.

Блок ИУВВ состоит из аналоговой и цифровой частей. Аналоговая часть предназначена для ввода/вывода аналоговых сигналов и представлена на структурной схеме МПС(см. приложение 1) блоком AIOU. Функции цифровой части выполняет часть портов ЦП. Назначение сигналов портам ЦП приведено в таблице 2.6.

Таблица 2.6

|

Порт |

Внешний сигнал |

Тип |

|

P1.3 |

X1 |

Вход |

|

P1.4 |

X2 |

Вход |

|

P1.5 |

X3 |

Вход |

|

P1.6 |

X4 |

Вход |

|

P1.7 |

Y1 |

Выход |

|

P3.0 |

Y2 |

Выход |

|

P3.1 |

Y3 |

Выход |

Аналоговая часть включает в себя АЦП DA1 и ЦАП DA2.

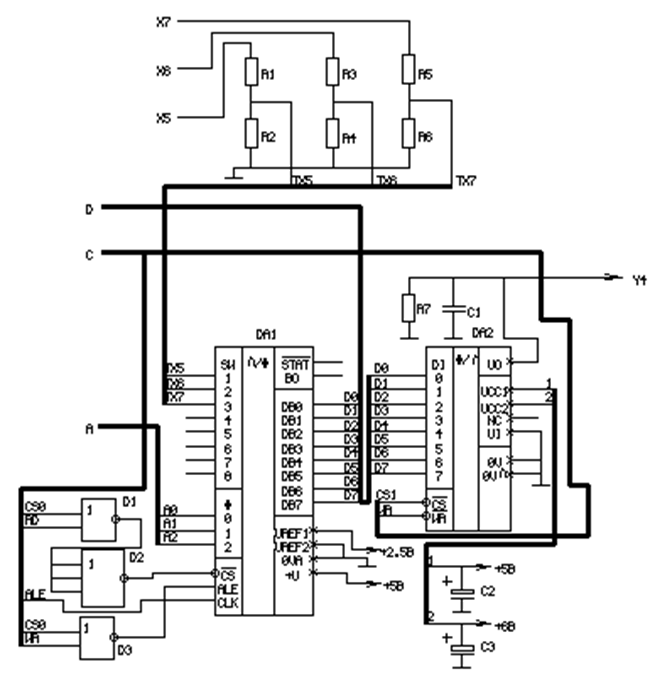

Функциональная схема AIOU приведена

на рис. 2.8 (см. приложение 1).

Рис. 2.8. Функциональная схема AIOU.

Оценим необходимую разрядность АЦП и ЦАП исходя из требований ТЗ к погрешности обработки аналоговых сигналов, составляющей не более 1%. Очевидно, наибольшую погрешность будет иметь сигнал Y4, поскольку для его получения требуется самая длинная цепочка преобразований (см. приложение 1). Таким образом, для выполнения требований ТЗ достаточно обеспечить dY4£1%, где dY4-относительная погрешность формируемого МПС сигнала Y4. По определению [11]:

![]() ,

,

|

(2.1) |

где Y4=A0+A1*X7-идеальное значение сигнала, Y4*-реальное. Тогда можно записать, что

Y4*=f3(A0+f2(A*f1(X7))),

где f1 символизирует аналого-цифровое преобразование, f2-вычисления внутри CPU, f3-цифроаналоговое преобразование. Указанные преобразования и являются основными источниками погрешности Y4. Примем в первом приближении f3=0. Поскольку используемый CPU является 8‑разрядным, будем считать погрешность вычислений равной половине младшего разряда (МР), или 1/512»0.2%. Также будем считать, что погрешность АЦП соответствует 1МР [2]. Тогда будем иметь:

1/2n£0.01-0.002=0.008,

n³6,7.

Отсюда следует, что целесообразно использовать 8-разрядный АЦП. Поскольку используется 8-разрядный CPU, 8-разрядный ЦАП в такой системе теоретически не будет вносить дополнительную погрешность, что соответствует принятому допущению f3=0.

В Выберем в качестве

DA1 выбрана

микросхемау К572ПВ4. Данная

микросхема является 8‑разрядным

АЦП последовательного приближения, выполнена по КМДП‑технологии и представляет

собой БИС аналого-цифровой системы сбора данных, выполнена

по КМДП-технологии, представляет собой

8-разрядный АЦП последовательного приближения. Кроме того, в

состав микросхемы входит 8-канальный мультиплексор и буферное ОЗУ емкостью 64

бит с произвольной выборкой, что позволяет использовать единственный АЦП для

ввода в МПС всех сигналов аналоговых датчиков и избежать аппаратных затрат,

связанных с использованием внешнего мультиплексора. БИС имеет буферные схемы с

тремя состояниями, позволяющие подключить ее непосредственно к шине данных МПС.

Основные

параметры микросхемы приведены в таблице 2.7, Нназначение

выводов

микросхемы приведено в-в таблице 2.78[2].

Таблица 2.7

|

Параметры |

Значения параметров |

|

|

|

мин. |

макс. |

|

Напряжение питания, Ucc1, В |

4.25 |

5.25 |

|

Нелинейность, dL, ед. МР |

- |

|±0.5| |

|

Дифференциальная нелинейность, dLD, ед. МР |

- |

|±0.5| |

|

Абсолютная погрешность, dFS, ед. МР |

- |

1 |

|

Тактовая частота, fT, МГц |

- |

2.5 |

|

Ток потребления, Icc, мА |

- |

3 |

|

Время преобразования, tC, мкс |

- |

25 |

Уважаемый посетитель!

Чтобы распечатать файл, скачайте его (в формате Word).

Ссылка на скачивание - внизу страницы.