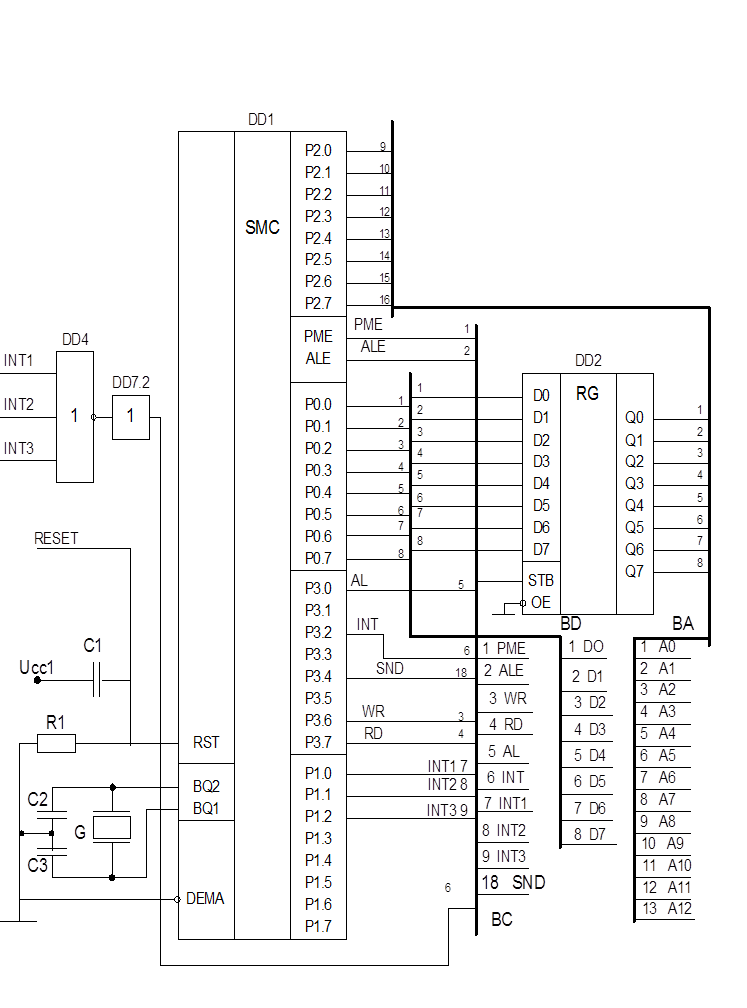

Функциональная схема микропроцессорного блока показана на рис. 2.

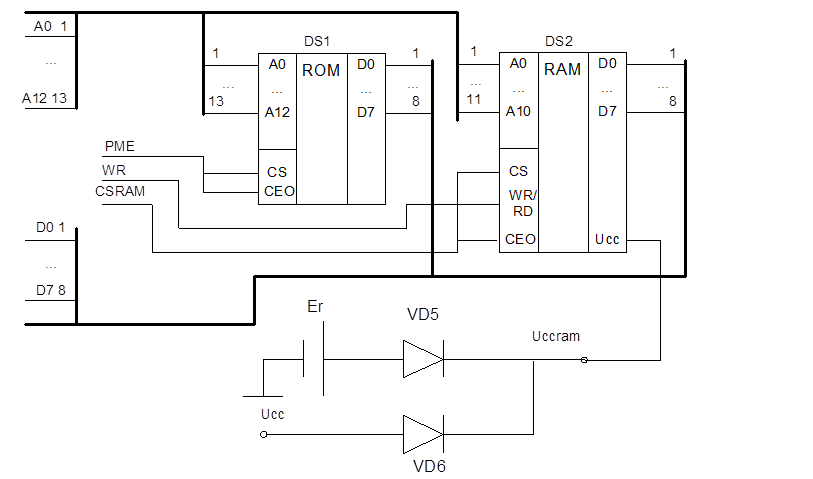

2.4. Разработка блока ЗУ

2.4.1. Разработка блока ОЗУ

Для построения ОЗУ выбранной емкости (4Кбайт) используем микросхемы статического ОЗУ КР537РУ8А. Данная микросхема имеет информационную емкость 16384 бит, организованную в виде 2048 слов * 8 разрядов. Таким образом, для построения ОЗУ потребуется 1 микросхема памяти.

![]() Для адресации внутреннего пространства

используются 11 адресных входов, для управления вход WR/RD и два входа

Для адресации внутреннего пространства

используются 11 адресных входов, для управления вход WR/RD и два входа

разрешения CS1 и CS2. Микросхема имеет двунаправленный 8-разрядный канал данных с третьим состоянием, по входам и выходам совместима со схемами ТТЛ.

|

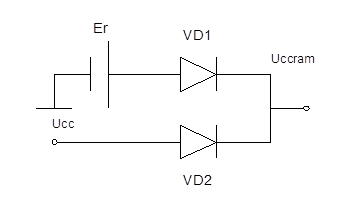

Выбор диодов в схеме осуществляется в соответствии с токами потребления микросхем, поддерживающих работу ОЗУ. В схеме необходимо обеспечить питание одной БИС ЗУ. При переводе микросхемы в режим хранения в случае аварии источника питания, ток

потребления микросхемы памяти составит 1 мкА, при этом можно снижать напряжение питания до 3В. Таким образом, необходимо обеспечить ток 1 мкА. Тогда, в качестве диода можно выбрать элемент D311, обеспечивающий при прямом токе Iпр=10 мА, падение напряжения не более 0,4 В. В качестве батареи питания можно выбрать источник напряжением 4,05В – батарея 3РЦ53.

При питании памяти от основного источника, потребление в режиме обращения составит 30 мА для одной микросхемы. Таким образом, необходимо обеспечить протекание прямого тока 60 мА. Исходя из этого, можем взять диоды КД513А, обеспечивающие при прямом токе Iпр = 100 мА падение напряжения не более 0,8 В.

При отказе источника питания, на входе CS микросхемы энергонезависимого ОЗУ необходимо обеспечить состояние логической 1-цы. Для этого используется внешний сигнал ERR, приходящий от источника питания. При отказе основного источника, сигнал ERR принимает высокий уровень, что приводит к установлению на входе CS микросхемы энергонезависимого ОЗУ 1-цы и обеспечивает сохранность информации.

Так как шина данных BD 8-разрядная, то память не разбивается на банки.

2.4.2. Разработка блока ПЗУ

Будем строить ПЗУ на микросхемах репрограммируемого ЗУ К537РФ5. Микросхема имеет информационную емкость 16384 бит, организованную в виде 2048 слов * 8 разрядов. Таким образом, для построения ПЗУ потребуется 1 микросхема памяти.

Для адресации внутреннего пространства микросхемы используются 11 адресных входов, для управления вход разрешения CS. Микросхема имеет 8-разрядный канал данных с третьим состоянием, по входам и выходам совместимый со схемами ТТЛ.

Как было описано при проектировании ОЗУ, нет необходимости обеспечивать разделение памяти на два банка.

В итоге получим функциональную схему блока ЗУ (запоминающих устройств), приведенную на рис. 4.

![]()

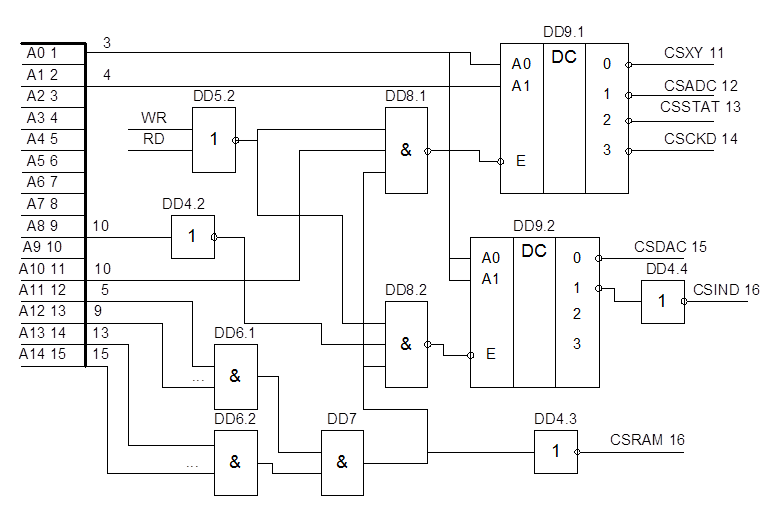

2.5. Разработка формирователя сигналов выбора микросхем

Будем вырабатывать управляющие сигналы CS для интерфейсных микросхем разрядами A2 – A4 шины адреса.

Формирователем производится выдача сигналов выбора микросхем для всех периферийных устройств МПС. Формирователь строится на микросхеме К1554ИД4, функционально представляющей собой дешифратор/де мультиплексор 2 на 4. Микросхема имеет два адресных входа, кодом на которых определяется активный выход. Помимо этого, имеются один стробирующий вход. Так как всего устройств в системе 7, то необходимо два таких дешифратора. Также нужна схема проверки обращения к устройствам и памяти.

Схема формирователя представлена на рис.6.

![]()

2.6. Разработка блока ввода/вывода

Уважаемый посетитель!

Чтобы распечатать файл, скачайте его (в формате Word).

Ссылка на скачивание - внизу страницы.