Контрольные тесты

Тест 1 (раздел 1)

1. Функция импликации х1 к х2 обозначается и определяется формулой

А) ![]() ;

;

Б) ![]() ;

;

В) ![]() ;

;

Г)  .

.

2. Условное обозначение элемента, выполняющего операцию дизъюнкции, представлено на схеме

А) Б) В)

3. Таблица истинности операции дизьюнкции представлена в виде

А) Б)

|

x1 |

x2 |

Y |

x1 |

x2 |

Y |

|

|

0 |

0 |

0 |

0 |

0 |

0 |

|

|

0 |

1 |

1 |

1 |

0 |

0 |

|

|

1 |

0 |

1 |

0 |

1 |

0 |

|

|

1 |

1 |

1 |

1 |

1 |

1 |

В) Г)

|

x1 |

x2 |

Y |

x1 |

x2 |

Y |

|

|

0 |

0 |

0 |

0 |

0 |

0 |

|

|

0 |

1 |

0 |

1 |

0 |

0 |

|

|

1 |

0 |

1 |

0 |

1 |

1 |

|

|

1 |

1 |

1 |

1 |

1 |

1 |

4. Закон склеивания записывается в виде

А) ![]()

Б) ![]()

В) ![]()

Г) ![]()

5. На карте Карно контур «b» отражает склеивание минтермов:

А)![]() ;

;

|

В)

;

;

Г) х1х3∩х2х3=х3(х1∩х2).

Тест 2 (раздел 2)

1. В позиционной системе счисления числа представляются последовательностью цифр разрядов…

А) содержащих группу разрядов целой части числа и группу дробной части;

Б) содержащих коды целых и дробных частей;

В) содержащих группу нулей и группу единиц;

Г) содержащих группу единиц целой части числа.

2. Запись 0,1012 соответствует в десятичной системе счисления числу…

А) 0 , 1 0 1В = (0∙20 , 1∙2-1 + 0∙2-2 + 1∙2-3)D.

↓ ↓ ↓ ↓

Весовые коэффициенты

20 2-1 2-2 2-3

Б) 1 , 1 0 1В = (1∙20 + 1∙2-1 + 0∙2-2 + 1∙2-3)D;

↓ ↓ ↓ ↓

Весовые коэффициенты

20 2-1 2-2 2-3

В) 0 , 1 0 1В = (0 , 1∙2-3 + 0∙2-2 + 1∙2-1 )D;

↓ ↓ ↓ ↓

Весовые коэффициенты

2-3 2-2 2-1

Г) 0 , 1 0 1В = ( 0 , 0∙22 + 1∙21 + 1∙20)D;

↓ ↓ ↓

Весовые коэффициенты

22 21 20

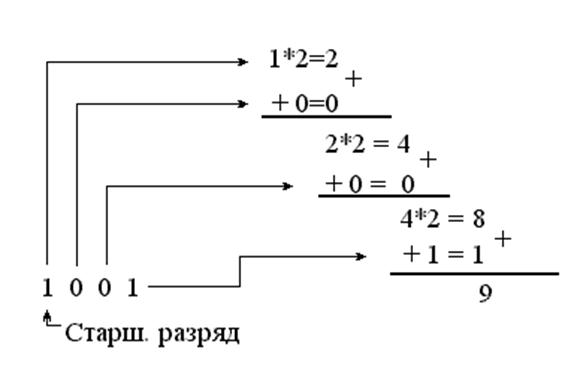

3. На рис. показан метод…

А) перевода двоичного числа в десятичное;

Б) сохранения десятичного числа;

В) пересчета десятичного числа;

Г) кодирования десятичного числа.

4. При пересчете дробной части десятичного числа в 16 – ричное производится операция…

А) умножения на 16;

Б) сложения с 16;

В) вычитания из 16;

Г) деления на 16.

5. Преобразование дробной части числа в другую систему счисления можно выполнить

А) с любой, наперёд заданной точностью;

Б) с ограниченной точностью;

В) с точностью, зависящей от метода расчёта;

Г) с точностью, определяемой «правилом трех сигм».

Тест 3 (раздел 3)

Комбинационные устройства

1. Устройство неравнозначности работает по структурной формуле…

А) ![]()

Б) ![]()

В) ![]()

Г) ![]()

2.Ниже представлена таблица истинности…

|

x2 |

x1 |

Y |

|

0 |

0 |

1 |

|

0 |

1 |

0 |

|

1 |

0 |

0 |

|

1 |

1 |

1 |

А) устройства равнозначности;

Б) устройства отрицания конъюнкции;

В) полного сумматора;

Г) устройства неравнозначности.

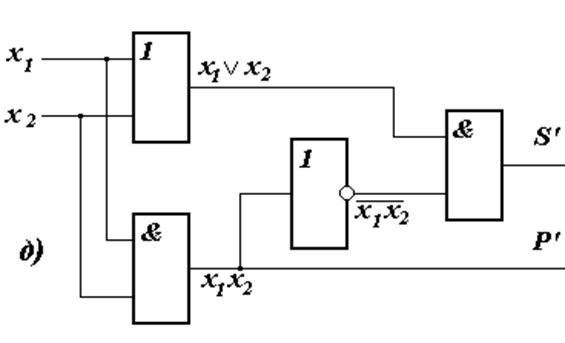

3. На рисунке приведена принципиальная схема…

А) полусумматора;

Б) полного сумматора;

В) устройства равнозначности;

Г) RS-триггера.

4. Полным сумматором называется устройство…

А) для сложения трех одноразрядных двоичных чисел;

Б) для сложения двух одноразрядных двоичных чисел;

В) для сложения двух одноразрядных двоичных чисел и вычитания одного одноразрядного двоичного чисела;

Г) для сложения двух одноразрядных двоичных чисел и вычитания одного двухразрядного двоичного числа.

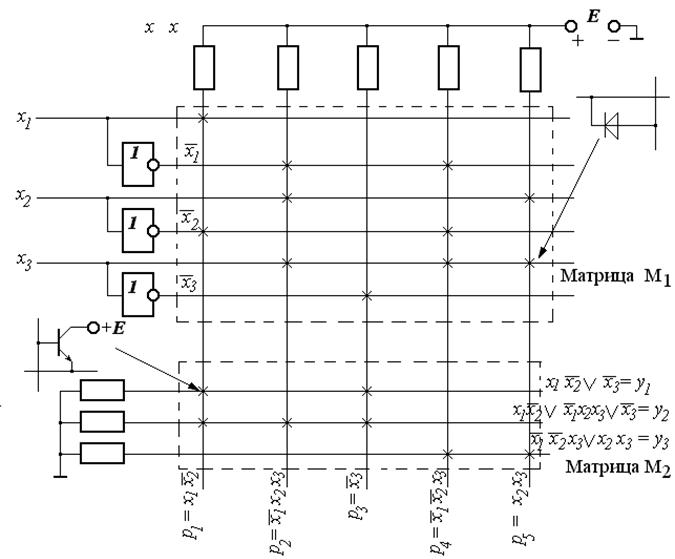

5. На рисунке приведена структура…

А) программируемой логической матрицы;

Б) демультиплексора;

В) дешифратора;

Г) кодопреобразователя.

Тест 4 (раздел 4)

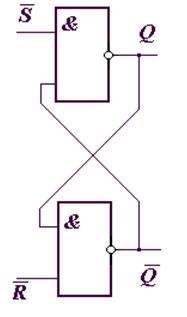

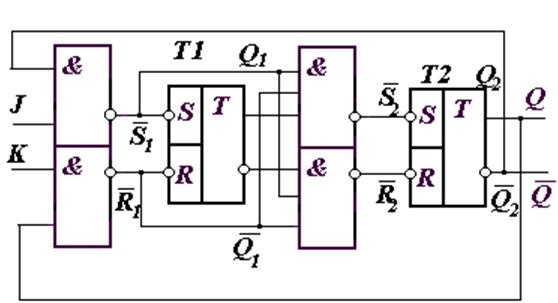

1. Ниже приведена принципиальная схема

А) RS – триггера с инверсными входами;

Б) JK – триггера;

В) D – триггера;

Г) Синхронного RS – триггера.

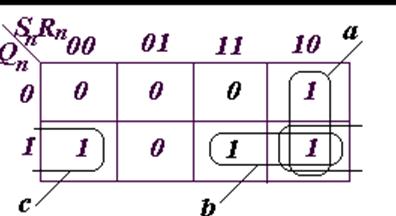

2. На рисунке карты Карно проведена минимизация функции Qn+1 графическим методом, дизьюнктивная форма записи которой будет иметь вид

А)![]()

Б) ![]()

В)![]()

Г)

3. Ниже приведена принципиальная схема

А) JK – триггера;

Б) RS – триггера с инверсными входами;

В) Е – триггера;

Г) Синхронного RS – триггера.

4. Ниже приведена таблица переключений

|

Jn |

Kn |

Qn |

Qn+1 |

|

0 0 0 0 1 1 1 1 |

0 0 1 1 0 0 1 1 |

0 1 0 1 0 1 0 1 |

0 1 0 0 1 1 1 0 |

А) JK – триггера;

Б) D– триггера;

В) Е – триггера;

Г) Синхронного RS – триггера.

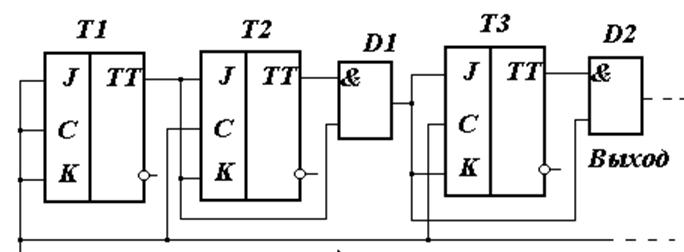

5. На рисунке приведена схема счетчика

Вход ↑

А) с параллельным переносом;

Б) с комбинированным переносом;

В) с последовательным переносом;

Г) с реверсивным переносом.

Тест 5 (раздел 5)

1. В процессе дискретизации из непрерывного во времени сигнала

А) выбираются отдельные его значения в определенные моменты времени;

Б) выбираются максимальные его значения в произвольные моменты времени;

В) выбираются непрерывные его значения в определенные интервалы времени;

Г) выбираются отдельные его значения в экстремальные моменты времени.

2. Дискретизация по времени осуществляется с помощью ключевого устройства, управляемого импульсами, длительность которых:

А) много меньше интервала дискретизации;

Б) равна периоду сигнала;

В) равна интервалу дискретизации;

Г) равна ½ периода сигнала.

3. Преобразование непрерывных сигналов в цифровую форму делается

А) с целью повышения помехоустойчивости процесса передачи информации;

Б) с целью использования более простой аппаратуры для передачи-приема сигналов;

В) с целью повышения скорости передачи.

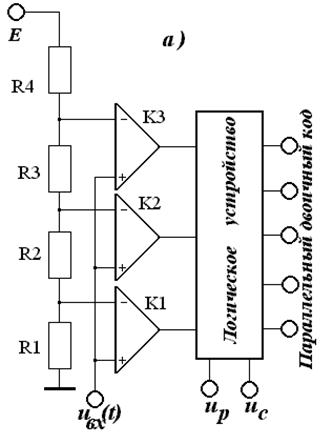

4. На рисунке а) представлена схема АЦП (К1…К3 – компараторы)

А) параллельного типа;

Б) последовательного типа;

В) комбинированного типа;

Г) промежуточного типа.

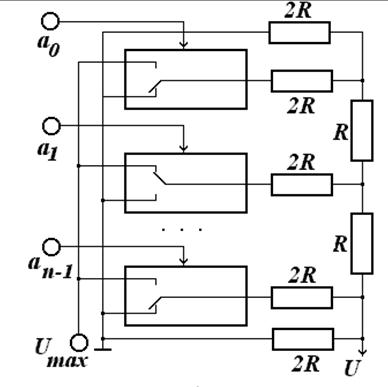

5. Ниже на рисунке ({аn-1an-2…a1a0}- входное двоичное число) изображена

схема преобразователя ЦАП

А) «код – напряжение»;

Б) «код – ток»;

В) «код – сопротивление»;

Г) «код – приращение напряжения»;

Тест 6 (раздел 6)

1. В постоянных запоминающих устройствах предусмотрены режимы

А) хранения и чтения;

Б) записи и перезаписи;

В) хранения и обновления;

Г) чтения и записи.

2. Килобайт равен

А) 1024х8 бит;

Б) 512х8 бит;

В) 1024х16 бит;

Г) 256х10 бит.

3. При числе разрядов двоичного кода m число ячеек в запоминающем устройстве составит

А) N=2m;

Б) N=2*m;

В) N=2m+1;

Г) N=2m-1.

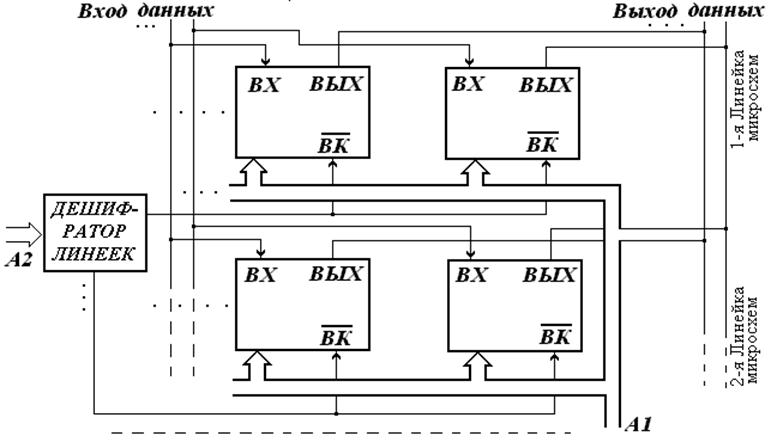

4. Ниже на рисунке изображена схема наращивания емкости оперативного запоминающего устройства за счет

А) наращивания числа ячеек и их разрядности;

Уважаемый посетитель!

Чтобы распечатать файл, скачайте его (в формате Word).

Ссылка на скачивание - внизу страницы.