ВНУТРЕННИЙ БЫСТРЫЙ RC-ГЕНЕРАТОР (FRC)

Внутренний быстрый RC-генератор обеспечивает номинальную частоту 7.37 МГЦ, не требуя внешнего кварцевого или керамического резонатора, Это может быть полезно когда не требуется большой точности к тактовой частоте.

Прикладное программное обеспечение может настроить частоту генератора от-12 % до +11.625 % ( приблизительно с шагом в 30 кГц) от номинального значения частоты, используя FRC Настройку Генератора битами (TUN <5:0>) в регистре настройки генератора FRC (OSCTUN <5:0>) регистр.

Обратите внимание: Обратитесь к даташиту на определённый микроконтроллер для определения точности частоты генератора FRC в зависимости от температуры и питающего напряжения.

Внутренний FRC генератор стартует немедленно. В отличие от кварцевого резонатора, которому может потребоваться несколько миллисекунд, чтобы начать колебание, в то время как внутреннийй FRC начинает колебания немедленно.

Выбор генератора осуществляется битами (FNOSC <2:0>) регистра конфигурации генератора

(FOSCSEL <2:0>). Биты конфигурации программируются во время программирования устройства.

Режимы генератора FRC

|

FNOSC<2:0> Значение |

Режим работы генератора |

|

000 |

FRC генератор (FRC) |

|

001 |

FRC генератор с PLL (FRCPLL) |

|

110 |

FRC генератор с постделителем на 16 (FRCDIV16) |

|

111 |

FRC генератор с постделителем на N (FRCDIVN) |

FRC Режим с постделителем на N (FRCDIVN)

В FRC режиме с постделителем, переменный постделитель делит выходную частоту генератора FRC и позволяет получить более низкую частоту. Постделитель внутреннего быстрого RC-генератора управляется с помощью битов (FRCDIV <2:0>) в регистре делителя частоты (CLKDIV <10:8>), которые позволяют задать 16 разных значений делителя от 1:1 до 1:256.

Ниже приведена таблица соответствия коэффициента деления и бита настройки

|

Значение FRCDIV <2:0> |

Коэффициент деления внутреннего FRC генератора |

|

000 |

FRC делённая на 1 (по умолчанию) |

|

001 |

FRC делённая на 2 |

|

010 |

FRC делённая на 4 |

|

011 |

FRC делённая на 8 |

|

100 |

FRC делённая на 16 |

|

101 |

FRC делённая на 32 |

|

110 |

FRC делённая на 64 |

|

111 |

FRC делённая на 256 |

Для увеличения тактовой частоты вывод FRC после постделителя можно использовать с внутренным PLL. Это позволяет увеличить частоту (FOSC) до 80 МГЦ т.е. 40 MIPS.

Обратите внимание:FRC делитель не должен изменяться динамически при работе в режиме внутренний FRC с PLL.

Для изменения необходимо:

1. Переключить генератор в режим без PLL (например, внутренний FRC).

2. Сделать необходимые изменения.

3. Переключить генератор назад в режим с PLL.

PHASE-LOCKED LOOP (PLL)

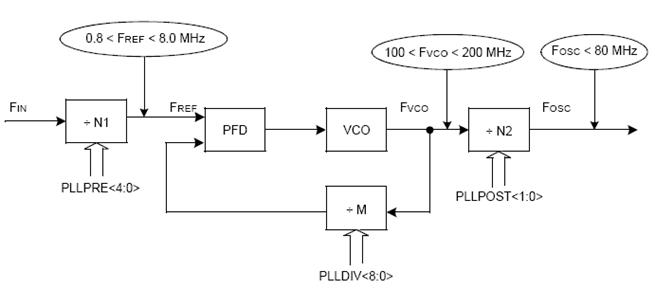

Главный генератор и внутренний FRC генератор могут использовать модуль PLL чтобы получить более высокие частоты. На рисунке 7-8 приведена блок-схема модуля PLL.

Для надлежащей работы PLL, детектор фазы частоты (PFD) вводит частоту и напряжение управляемого генератора (VCO), к выходной частоте должны выполниться следующие требования:

• частота входа PFD (FREF) должен быть в диапазоне от 0.8 до 8.0 МГЦ

• VCO выходная частота (FVCO), должен быть в диапазоне 100 - 200 МГЦ

Биты выбора предделителя PLL (PLLPRE <4:0>) в регистре делителя частоты (CLKDIV <4:0>) определяет входной коэффициент деления (N1), который используется, чтобы уменьшить входную частоту (FIN) до значения частоты 0.8 МГЦ к 8 МГЦ.

Уважаемый посетитель!

Чтобы распечатать файл, скачайте его (в формате Word).

Ссылка на скачивание - внизу страницы.