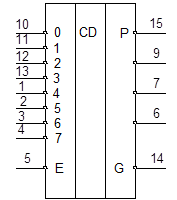

Если на всех

информационных входах микросхемы логическая "1", на выходах 1, 2, 4,

G - логическая "1", на выходе Р - логический "О". При

подаче логического "О" на любой из информационных входов 0-7 на

выходах 1, 2,4 появится инверсный код, соответствующий номеру входа, на который

подан логический "О", на выходе

G - логический

Если на всех

информационных входах микросхемы логическая "1", на выходах 1, 2, 4,

G - логическая "1", на выходе Р - логический "О". При

подаче логического "О" на любой из информационных входов 0-7 на

выходах 1, 2,4 появится инверсный код, соответствующий номеру входа, на который

подан логический "О", на выходе

G - логический

Рис.-13 Условное графическое обозначение R155ИМС ИВ1

"О", что является признаком подачи входного сигнала, на выходе Р - логическая "1", которая запрещает работу других ИМС К155ИВ1 при их каскадном соединении. Если логический "О" будет подан на несколько информационных входов микросхемы, выходной код будет соответствовать входу с большим номером. Так работа микросхемы происходит при подаче на вход Е логического "О". Если же на входе Е логическая "1" (запрет работы), на всех шести выходах микросхемы логические "1".

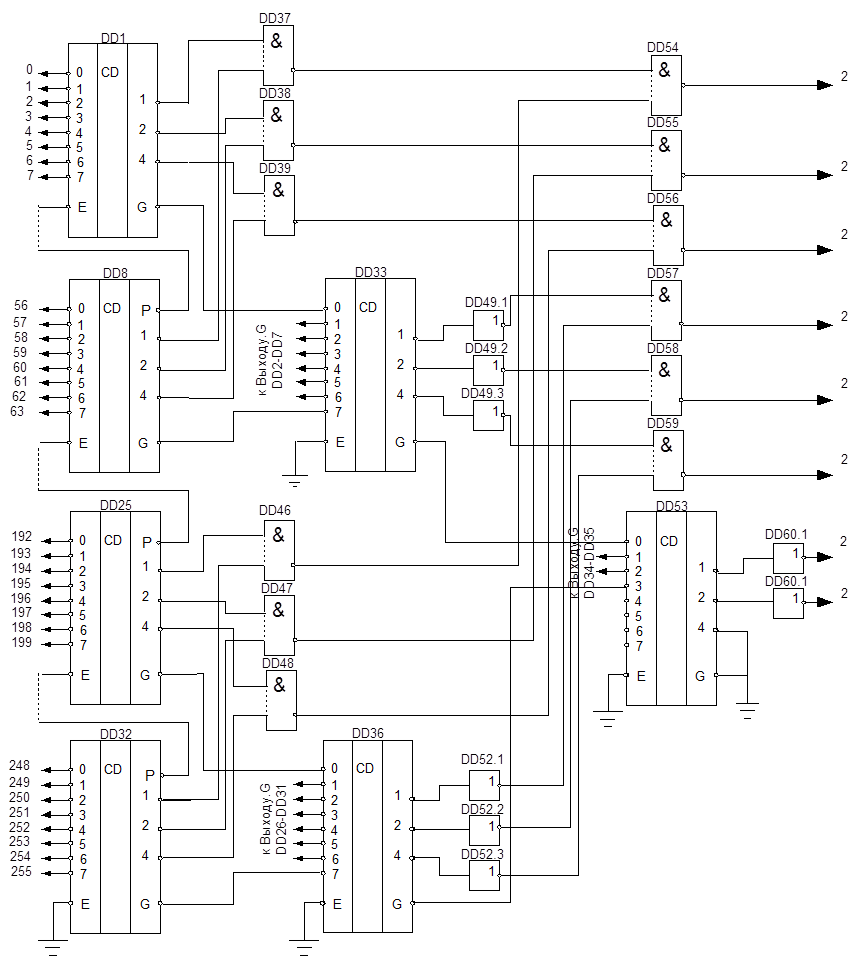

Для наших целей необходимо собрать схему, приведенную на рисунке 5.3. Кроме 37 микросхем К1555ИВ1 в нее входят микросхемы низкой степени интеграции: 18 ИМС К155ЛА2 (элемент И-НЕ) и 5 ИМС (элемент ИЛ И-НЕ).

Полная схема устройства АЦП приведена в составе полной схемы микропроцессорного агрегата (рисунок 7.1).

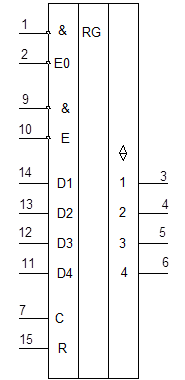

5.3 Буферный регистр

В проектируемом агрегате между шиной данных (ШД) и портами ввода/вывода устанавливаются буферные регистры хранения информации. Выбираем микросхему К155ИР15 - четырехразрядный регистр хранения информации с возможностью перевода выводов в высокоимпедансное состояение. Запись информации с входов D1-D4 в триггеры микросхемы происходит по спаду импульса отрицательной полярности на входе С, обнуление триггеров - по импульсу положительной полярности на входе R.

|

Рис -14 Схема кодирующей логики АЦП

Особенность регистра - два равноправных инверсных входа разрешения записи EL, собранных по И. Наличие логической "1" на одном из этих входов запрещает запись в триггеры, причем изменение сигналов на D1-D4 может происходить как при логическом "О", так и при логической "1" на входе С, важно состояние этих входов непосредственно перед переходом из логического "О" в логическую "1" сигнала на входе С.

Микросхема имеет два равноправных инверсных входа ЕО, собранных по И. Наличие логической "1" на любом из этих входов переводит выходы в высокоимпедансное состояние. Состояние входов ЕО никак не влияет на работу микросхемы по другим входам - запись, обнуление могут происходить при любых сочетаниях сигналов на входах ЕО.

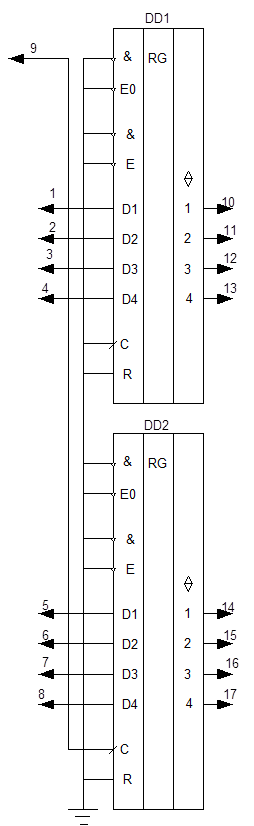

Для наших целей соединим два регистра КР155ИР15, получив восьмиразрядный блок буферных регистров На шины управления (ШУ) выведем только входы С, которые полностью в состоянии удовлетворить наши требования к работе регистров. На остальные входы (кроме входов данных) подадим логический "О".

Рис.-15 Условное графическое обозначение КР155ИР15

Абсолютно аналогичное устройство блока буферных регистров применим и перед ЦАП.

ЦАП.

|

Рис 16 - Схема блока буферных регистров

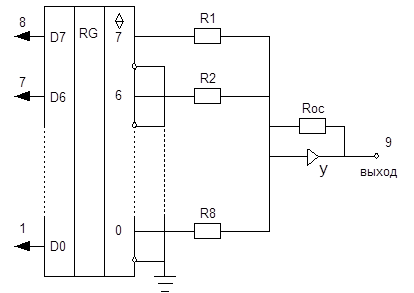

Согласно заданию, для данного микропроцессорного агрегата проектируем ЦАП с суммированием напряжений на оперативном усилители

Напряжение на выходе ЦАП определяется по формуле:

Uвых=SUвхi*(Rос:Ri)

где сопротивление параллельных ветвей:

i-1

Ri=2* R1

Сопротивление Roc возьмем МЛТ-0.125; R = 1 кОм, a Ri - МЛТ-0.125; R = 100 Ом. Тогда номиналы остальных сопротивлений параллельных ветвей МЛТ-0.125; R = 200, 400, 800, 1600, 3200, 6400, 128000 к0м.

|

Полная схема микропроцессорного агрегата.

При компоновке схемы агрегата использовались все элементы и устройства, рассмотренные выше в пунктах 1-6. Добавлены подробно не рассматривавшиеся шины данных (ШД), адреса (ША) и управления (ШУ).

СПИСОК ЛЛИТЕРАТУРЫ:

1.Кулажский В.Д.Применение МПТ для задач электроэнергетики :Учебное пособие.-Хабаровск: ДВГУПС, 1994-78с.

2.Интегральные микросхемы : Справочник /Б.В.Тарабрин,-М: .Радио и связь, 1983-527с.

3. Резисторы, конденсаторы, устройства РЭА.:/справочник Н.Н.Акимов. Беларусь, 1994.-591с.

Уважаемый посетитель!

Чтобы распечатать файл, скачайте его (в формате Word).

Ссылка на скачивание - внизу страницы.