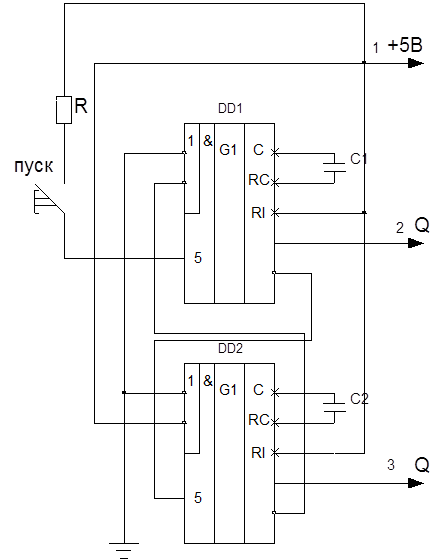

Рис.-10 Схема блока управления

|

Полагая, что за десять постоянных времени тувх переходной процесс в УВХ завершится, считаем длительность импульса выборки:

Ts=10*tувх (1)

Ts=10*0,42=4,2 мкс

Зная, что длительность тактового импульса включает в себя и постоянную времени аналого-цифрового устройства:

TG=Ts+tАЦП (2)

TG=4,2+3,52=7,72 мкс

Для одиночного ждущего мультивибратора К155АГ1 соотношение между параметрами времязадающей цепочки и постоянной времени вы глядит как:

t=0,7R*C (3)

Откуда, зная величину внутреннего сопротивления мультивибратора:

МТЛ-0,125 R=10 ОМ

C=t: (0,7*10)=1103 пФ

Из стандартного ряда Е12 выбираем наиболее близкую по значению емкость – 1,1 нФ. Мы могли бы выбрать номинальную емкость и из других стандартных рядов, обеспечив большую точность, но это вызвало бызначительные затраты на высокоточные элементы. Итак, окончательно принимаем времязадающие элементы Ci и Cz конденсаторами К ID23; С = 1,1 нФ.

Пересчитаем длительность тактового импульса, исходя из реальных параметров схемы:

TG=0,7R*C=0,7*10*1,1=7,7 мкс

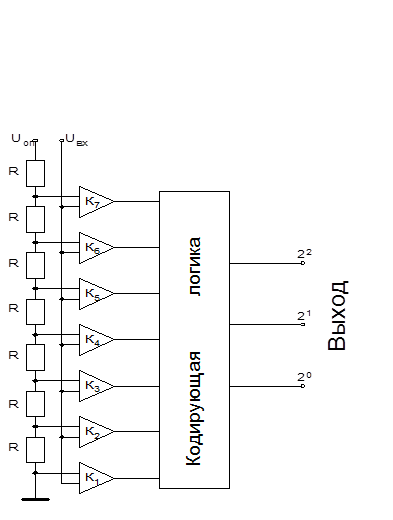

5 АНАЛОГО-ЦИФРОВОЙ ПРЕОБРАЗОВАТЕЛЬ (АЦП)

АЦП параллельного

типа содержит делитель, состоящий из набора последовательно включенных

резисторов с одинаковым сопротивлением R, компараторов К и кодирующей логики.

На один из входов каждого компаратора подается опорное напряжение Uоп,

снимаемое с делителя, причем эти напряжения отличаются друг от друга на

величину DU

(см. рисунок 12). Вторые входы компараторов объединены и на них подано входное

напряжение Uвх. Работу АЦП данного типа можно рассмотреть по

диаграмме, изображенной на рисунке 12.

АЦП параллельного

типа содержит делитель, состоящий из набора последовательно включенных

резисторов с одинаковым сопротивлением R, компараторов К и кодирующей логики.

На один из входов каждого компаратора подается опорное напряжение Uоп,

снимаемое с делителя, причем эти напряжения отличаются друг от друга на

величину DU

(см. рисунок 12). Вторые входы компараторов объединены и на них подано входное

напряжение Uвх. Работу АЦП данного типа можно рассмотреть по

диаграмме, изображенной на рисунке 12.

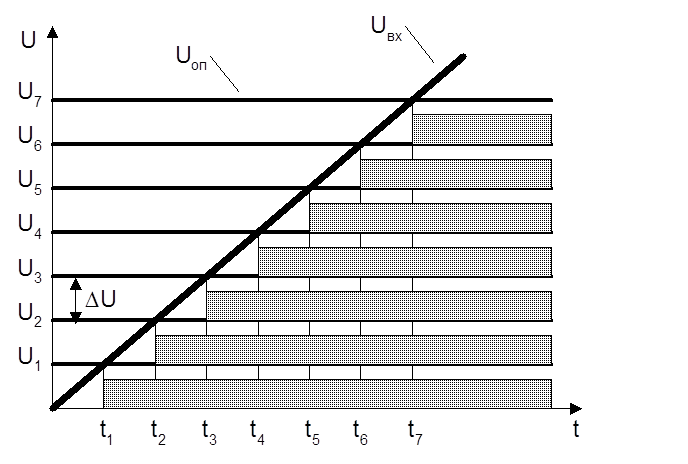

Рис 12 - Диаграмма работы работы АЦП параллельного типа

При достижении входным напряжением значения опорного напряжения первого компаратора U1 (момент времени t1) последний срабатывает и подает сигнал активного уровня со своего выхода на первый вход устройства кодирующей логики, на выходе которого при этом появляется число "1" в двоичном коде. При дальнейшем возрастании входного напряжения в момент времени t2 сработает второй компаратор и на выходе АЦП появится "2" и т.д. В данном случае значение DU представляет собой шаг квантования.

Шаг квантования определяется по формуле, А:

А (4)

А (4)

где L - ширина изменения сигнала, т. е. его амплитуда, из задания на курсовую работу L = 510 А;

d- шум квантования, из задания d = 0.7%.

D=510*0.7:100=3.57 А

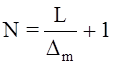

Число уровней квантования определяется:

,

(5)

,

(5)

N=510:3.57+1=143.8

: Искомое количество разрядов для АЦП определяется как ближайшее целое по следующему условию:

![]()

n>log2143.8>7.7

Выбираем разрядность n= 8. Теперь следует пересчитать истинное число уровней квантования, шум и шаг квантования.

Истинное число уровней квантования нетрудно определить

N’ = 2n

N’ = 28 =256

Тогда истинный шаг квантования из. формулы 4.2 равен:

=510:

(256-1)=2 А

=510:

(256-1)=2 А

Истинное значение шум квантования:

d`=D`:L*100=2:510*100=0.392

Кодирующая логика

Устройство кодирующей логики, в рассматриваемом случае представляющее собой шифратор служит для преобразования входного сигнала по 256 уровням квантования непосредственно в 8'и разрядный двоичный код.

В качестве базового элемента кодирующей логики примем микросхему К155ИВ1 - приоритетный шифратор 8-3, приведенную на рисунке 5.2. ИМС К155ИВ1 имеет восемь информационных входов 0-7 и вход разрешения Е. Выходов у этой микросхемы пять - три инверсных выходных кода 1, 2, 4; G - признак подачи входного сигнала и Р - переноса.

Уважаемый посетитель!

Чтобы распечатать файл, скачайте его (в формате Word).

Ссылка на скачивание - внизу страницы.