Выходы YA – YD имеют третье Z-состояние. Если на вывод ЕО — разрешение выходным данным — подается напряжение высокого уровня, выходы мультиплексора разомкнутся. Трансляция данных выходам разрешается при активном напряжении низкого уровня на входе ЕО. У каждого из четырех мультиплексоров имеется по два входа I1 и I2. Для их выбора служит один вход адреса данных S. Если на входе S напряжение низкого уровня, выбираются входы I1 одновременно всех четырех мультиплексоров. Соответственно при напряжении высокого уровня на входе S данные принимаются от входов I2A — I2D. Состояния входов управления, сигнальных, а также выхода для мультиплексора сведены в табл. 2.

Таблица 2. Состояния мультиплексора К555КП11

|

Вход |

Выход |

|||

|

E0 |

S |

I1 |

I2 |

Y |

|

В Н Н Н Н |

х Н Н В В |

х Н В х х |

х х х Н В |

Z Н В Н В |

Описание микросхемы К555КП11 на языке VHDL и эпюры его работы показаны ниже.

library IEEE;

use IEEE.std_logic_1164.all;

entity K555KP11 is

port (

CS: in STD_LOGIC;

T: in STD_LOGIC;

A: in STD_LOGIC_VECTOR (3 downto 0);

B: in STD_LOGIC_VECTOR (3 downto 0);

C: out STD_LOGIC_VECTOR (3 downto 0)

);

end K555KP11;

architecture K555KP11 of K555KP11 is

begin

process(A,B,CS)

begin

if CS='0' then

if T='1' then

C<= transport A ;

else

C<= transport B ;

end if;

else

C<= transport "ZZZZ" ;

end if;

end process;

end K555KP11;

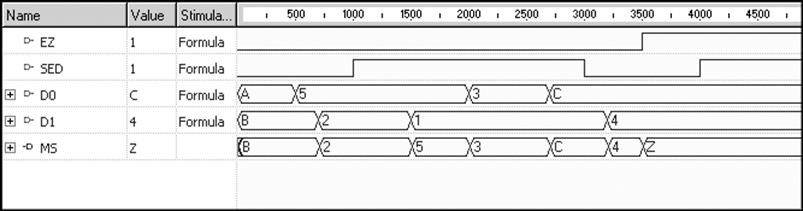

Здесь должна быть моя эпюра

Рис. 10. Эпюры работы мультиплексора К555КП11 в различных режимах.

|

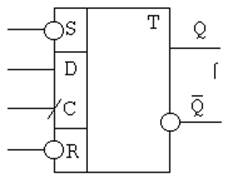

У данного триггера есть выходы D, ‘S и ‘R, а также комплементарные выходы Q и ‘Q. Входы ‘S и ‘R – асинхронные , потому что они работают (сбрасывают состояние триггера) независимо от сигнала на тактовом входе; активный уровень для них – низкий. Сигнал от входа D передаётся на выходы Q и ‘Q по положительному перепаду импульса на тактовом входе С ( от Н к В). Чтобы триггер переключился правильно, уровень на входе D следует зафиксировать заранее, перед приходом тактового перепада. Защитный интервал должен превышать время задержки распространения сигнала в триггере. Если на входы ‘S и ‘R триггера ТМ2 одновременно подаются напряжения низкого уровня, состояние выходов Q и ‘Q окажется неопределённым. Загрузить в триггер входные уровни Н или В можно, если на входы ‘S и ‘R подать напряжения высокого уровня.

Таблица 3. Логика работы триггера

‘S |

‘R |

C |

D |

Q |

‘Q |

|

0 |

1 |

x |

x |

1 |

0 |

|

1 |

0 |

x |

x |

0 |

1 |

|

0 |

0 |

x |

x |

1 |

1 |

|

1 |

1 |

Ý |

1 |

1 |

0 |

|

1 |

1 |

Ý |

0 |

0 |

1 |

Замечание: В программе ‘S = S, ‘R = R., ‘Q=notQ

Описание триггера К555ТМ2 на языке VHDL и эпюры его работы показаны ниже.

ibrary IEEE;

use IEEE.std_logic_1164.all;

entity K555TM2 is

port (

R: in STD_LOGIC;

D: in STD_LOGIC;

C: in STD_LOGIC;

S: in STD_LOGIC;

Q: out STD_LOGIC;

notQ: out STD_LOGIC

);

end K555TM2;

architecture K555TM2 of K555TM2 is

begin

process (S, C, D, R)

begin

if R = '1' then

if S = '1' then

if C = '1' and C'DELAYED = '0' then

-- zagruzka 0 ili 1

Q <= transport D after 25 ns;

notQ <= transport not D after 25 ns;

end if;

else

-- asinhronnaya ustanovka

Q <= transport '1' after 25 ns;

notQ <= transport '0' after 25 ns;

end if;

else

if S = '1' then

-- asinhronniy sbros

Q <= transport '0' after 25 ns;

notQ <= transport '1' after 25 ns;

else

-- neopredelyonnost'

Q <= transport '1' after 25 ns;

notQ <= transport '1' after 25 ns;

end if;

end if;

end process;

end K555TM2;

3.4 Микросхема К555ИД7 (дешифратор).

Уважаемый посетитель!

Чтобы распечатать файл, скачайте его (в формате Word).

Ссылка на скачивание - внизу страницы.