Министерство образования Российской Федерации

Рязанская государственная радиотехническая академия

Кафедра Систем Автоматизированного Проектирования Вычислительных Средств

Пояснительная записка к курсовому проекту по курсу

Выполнил:

студент гр. 045

Проверил:

доцент каф. САПР ВС

1. ВВЕДЕНИЕ

В этой работе предстоит смоделировать цифровую схему устройства сопряжения микропроцессорной системы с дисплеем при помощи языка описания аппаратуры (ЯОА/HDL - Hardware Digital Language) VHDL.

В настоящее время одна ИСможет содержать сотни тысяч логических вентилей, поэтому очень важно правильно выбрать уровень представления подобной сложной системы. Ключом к решению этой проблемы является работа на соответствующем уровне абстракции - уровне представления, который дает всю информацию, необходимую в данный момент времени, избавляя разработчика от необязательных деталей. В этом и заключается удобство и доступность языков HDL, в частности симулятора Active-VHDL компании Aldec.

Концепции языков HDL до сих пор оставались "собственностью" тех небольших коллективов, которые либо непосредственно их создавали, либо использовали их при разработке уникальных электронных систем. С утверждением стандарта на VHDL любая разработка и документирование аппаратуры и алгоритмов функционирования ДС должны сопровождаться описанием на языке VHDL, т. е.VHDL - описание является неотъемлемой частью документации и для разработчика, и для заказчика.

2. Моделирование элементов схемы

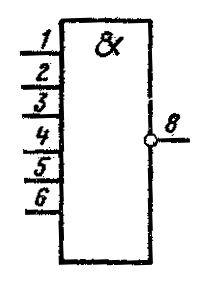

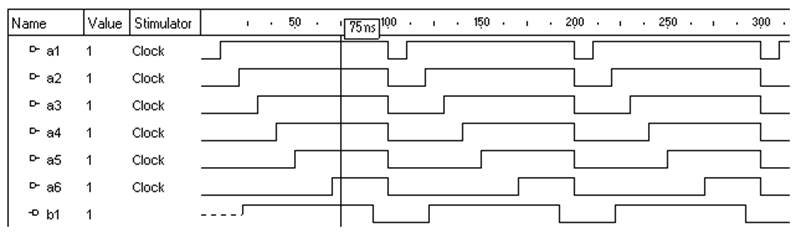

2.1 К155ЛА2 (6-И-НЕ)

Схема выполняет логическую функцию:

b1<=not(a1 and a2 and a3 and a4 and a5 and a6)

где a1-a6 – входы, b1 – выход.

Текст описания К155ЛА2 на VHDL:

library IEEE;

use IEEE.std_logic_1164.all;

entity K155LA2 is

port (

a1: in STD_LOGIC;

a2: in STD_LOGIC;

a3: in STD_LOGIC;

a4: in STD_LOGIC;

a5: in STD_LOGIC;

a6: in STD_LOGIC;

b1: out STD_LOGIC

);

end K155LA2;

architecture K155LA2 of K155LA2 is

begin

process(a1,a2,a3,a4,a5,a6)

begin

b1<=not(a1 and a2 and a3 and a4 and a5 and a6) after 22 ns;

end process;

end K155LA2;

Временные диаграммы

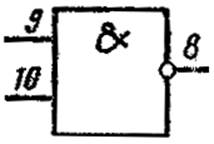

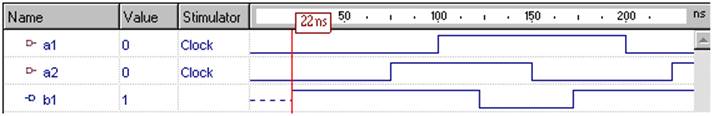

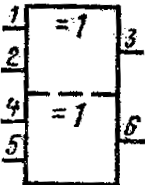

2.2 К155ЛА3 (2-И-НЕ)

Схема выполняет логическую функцию:

b1<=not(a1 and a2)

Таблица истинности:

|

а1 |

а2 |

b1 |

|

0 |

0 |

1 |

|

0 |

1 |

1 |

|

1 |

0 |

1 |

|

1 |

1 |

0 |

Текст описания К155ЛА3 на VHDL:

library IEEE;

use IEEE.std_logic_1164.all;

entity K155LA3 is

port (

a1: in STD_LOGIC;

a2: in STD_LOGIC;

b1: out STD_LOGIC

);

end K155LA3;

architecture K155LA3 of K155LA3 is

begin

process(a1,a2)

begin

b1<=not(a1 and a2) after 22 ns;

end process;

end K155LA3;

Временные диаграммы

2.3

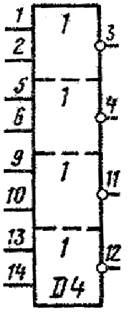

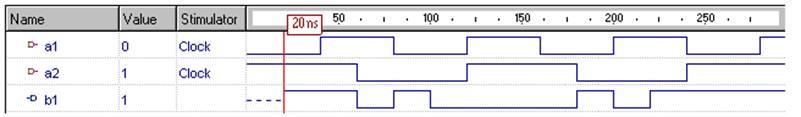

К559ИП2П (магистральный приемник)

К559ИП2П (магистральный приемник)

Функция, описывающая работу схемы:

b1<=not(a1 or a2)

Текст описания К559ИП2П на VHDL:

library IEEE;

use IEEE.std_logic_1164.all;

use IEEE.std_logic_unsigned.all;

entity K559_1 is

port (

a1: in STD_LOGIC;

a2: in STD_LOGIC;

a3: in STD_LOGIC;

a4: in STD_LOGIC;

a5: in STD_LOGIC;

a6: in STD_LOGIC;

a7: in STD_LOGIC;

a8: in STD_LOGIC;

b1: out STD_LOGIC;

b2: out STD_LOGIC;

b3: out STD_LOGIC;

b4: out STD_LOGIC

);

end K559_1;

architecture K559_1 of K559_1 is

begin

process(a1,a2,a3,a4)

begin

b1<=not(a1 or a2) after 30 ns;

b2<=not(a3 or a4) after 30 ns;

b3<=not(a5 or a6) after 30 ns;

b4<=not(a7 or a8) after 30 ns;

end process;

end K559_1;

Временные диаграммы К559ИП2П

2.4

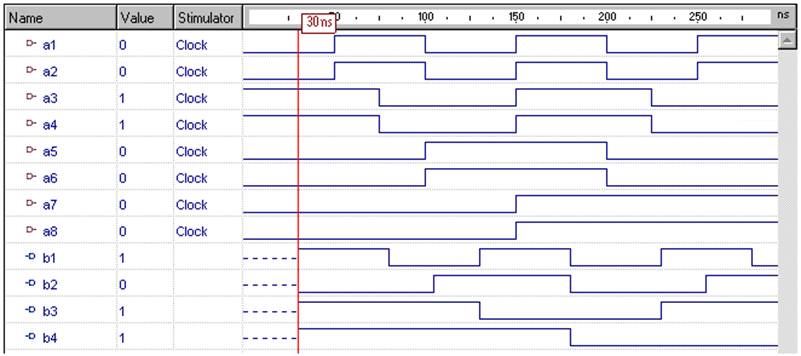

К155КП5 (XOR)

К155КП5 (XOR)

Функция описывающая работу схемы:

b1<=a1 xor a2

Текст описания К155КП5 на VHDL:

library IEEE;

use IEEE.std_logic_1164.all;

entity K155KP5 is

port (

a1: in STD_LOGIC;

a2: in STD_LOGIC;

a3: in STD_LOGIC;

a4: in STD_LOGIC;

b1: out STD_LOGIC;

b2: out STD_LOGIC

);

end K155KP5;

architecture K155KP5 of K155KP5 is

begin

-- <<enter your statements here>>

process(a1,a2)

begin

b1<=a1 xor a2 after 20 ns;

b2<=a3 xor a4 after 20 ns;

|

a1 |

a2 |

b1 |

|

0 |

0 |

0 |

|

0 |

1 |

1 |

|

1 |

0 |

1 |

|

1 |

1 |

0 |

end process;

end K155KP5;

Таблица истинности:

Временные диаграммы К155КП5

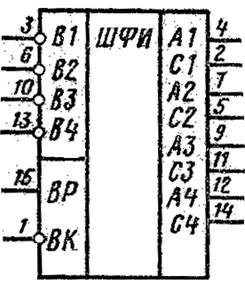

2.5 К589АП26 (шинный формирователь)

Шинный формирователь К589АП26 – параллельный двунаправленный формирователь сигналов для управления магистралями (шинами) в цифровых вычислительных устройствах.

Входы:

Входы:CS(ВК) – выборка схемы

DCE(ВР) – управляющий вход

DI0-DI3(А) – информационные входы

Выходы:

DO0-DO3(С) – информационные выходы

Входы-выходы:

DB0-DB3(В) – информационные входы выходы

|

CS |

DCE |

Направление передачи информации |

Выходы в состоянии «выключено» |

|

0 |

0 |

От входов DI до выходов DB |

DO |

|

0 |

1 |

От входов DB до выходов DO |

DB |

|

1 |

1 |

Передача отсутствует |

DO, DB |

Текст описания К589АП26:

library IEEE;

use IEEE.std_logic_1164.all;

use IEEE.std_logic_unsigned.all;

entity K589AP26 is

port (

CS: in STD_LOGIC;

DCE: in STD_LOGIC;

DI: in STD_LOGIC_VECTOR (3 downto 0);

DO: out STD_LOGIC_VECTOR (3 downto 0);

DB: inout STD_LOGIC_VECTOR (3 downto 0)

);

end K589AP26;

architecture K589AP26 of K589AP26 is

begin

-- <<enter your statements here>>

process (cs,dce,db,di)

variable i:integer;

begin

if (cs='0') and (dce='0') then

for i in 0 to 3 loop

db(i)<= di(i);

do(i)<='Z';

end loop;

end if;

if (cs='0') and (dce='1') then

for i in 0 to 3 loop

do(i)<= db(i);

end loop;

end if;

if (cs='1') then

for i in 0 to 3 loop

db(i)<='Z';

do(i)<='Z';

end loop;

end if;

end process;

end K589AP26;

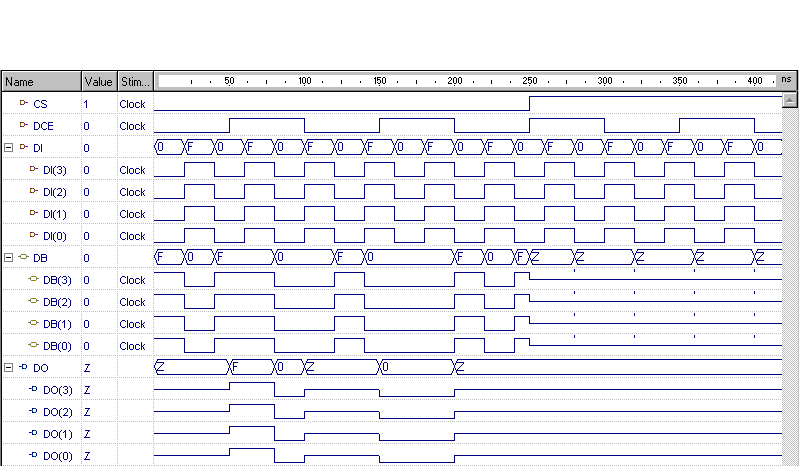

Временные диаграммы К589АП26

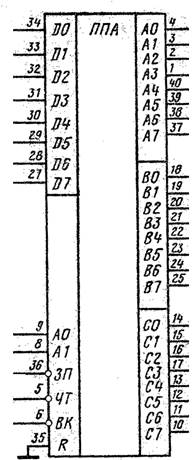

2.6 К580ВВ55 - программируемое устройство ввода/вывода параллельной информации.

Входы:

CS(ВК) – выбор микросхемы

RD(ЧТ) – чтение информации

WR(ЗП) – запись информации

SR(R) – установка в исходное состояние

A1,A0 – адресные входы

Входы/выходы:

ВА7-ВА0 – информационный канал А

ВВ7-ВВ0 – информационный канал В

ВС7-ВС0 – информационный канал С

D7-D0 – канал данных.

Микросхема может работать в трех основных режимах: режим 0 – простой ввод/вывод, режим 1 – стробируемый ввод/вывод, режим 2 – двунаправленный канал.

Предназначение этой микросхемы – выбор информационного канала и соответственно запись в него или чтение с него. Следовательно опишем микросхему в режиме 0.

Описание микросхемы:

library IEEE;

use IEEE.std_logic_1164.all;

entity K580BB55 is

port (

a: in STD_LOGIC_VECTOR (1 downto 0);

cs: in STD_LOGIC;

rd: in STD_LOGIC;

wr: in STD_LOGIC;

d: inout STD_LOGIC_VECTOR (7 downto 0);

ba: inout STD_LOGIC_VECTOR (7 downto 0);

bb: inout STD_LOGIC_VECTOR (7 downto 0);

bc: inout STD_LOGIC_VECTOR (7 downto 0)

);

end K580BB55;

architecture K580BB55 of K580BB55 is

begin

process(cs,a,rd,wr,d,ba,bb,bc)

variable i:integer;

begin

if cs='0' then

-- read operation

if (rd='0') and (wr='1') then

case a is

when "00" => for i in 0 to 7 loop

d(i)<=ba(i);

end loop;

when "01" => for i in 0 to 7 loop

d(i)<=bb(i);

end loop;

when "10" => for i in 0 to 7 loop

d(i)<=bc(i);

end loop;

when others => for i in 0 to 7 loop

d(i)<='Z';

ba(i)<='Z';

bb(i)<='Z';

bc(i)<='Z';

end loop;

end case ;

end if;

if (rd='1') and (wr='0') then

-- record operation

case a is

when "00" => for i in 0 to 7 loop

ba(i)<=d(i);

end loop;

when "01" => for i in 0 to 7 loop

bb(i)<=d(i);

end loop;

when "10" => for i in 0 to 7 loop

bc(i)<=d(i);

end loop;

when others => for i in 0 to 7 loop

d(i)<='Z';

ba(i)<='Z';

bb(i)<='Z';

bc(i)<='Z';

end loop;

end case;

end if;

end if;

if cs='1' then

for i in 0 to 7 loop

ba(i)<='Z';

bb(i)<='Z';

bc(i)<='Z';

end loop;

end if;

end process;

end K580BB55;

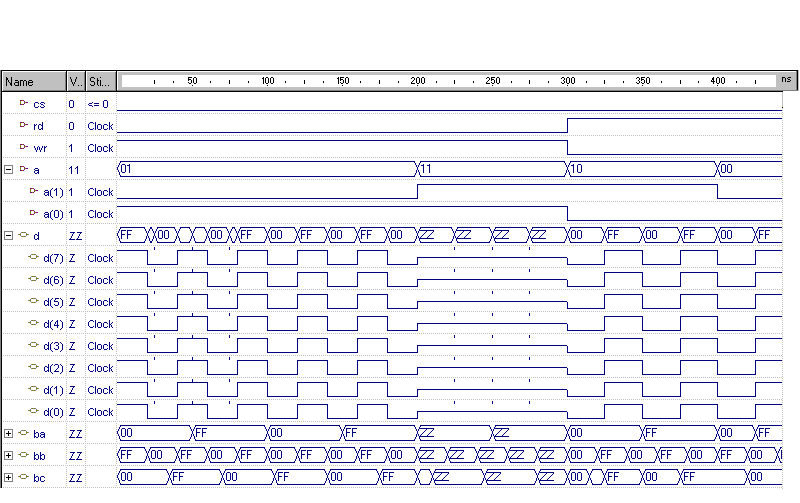

Временные диаграммы К580ВВ55

3. Моделирование схемы

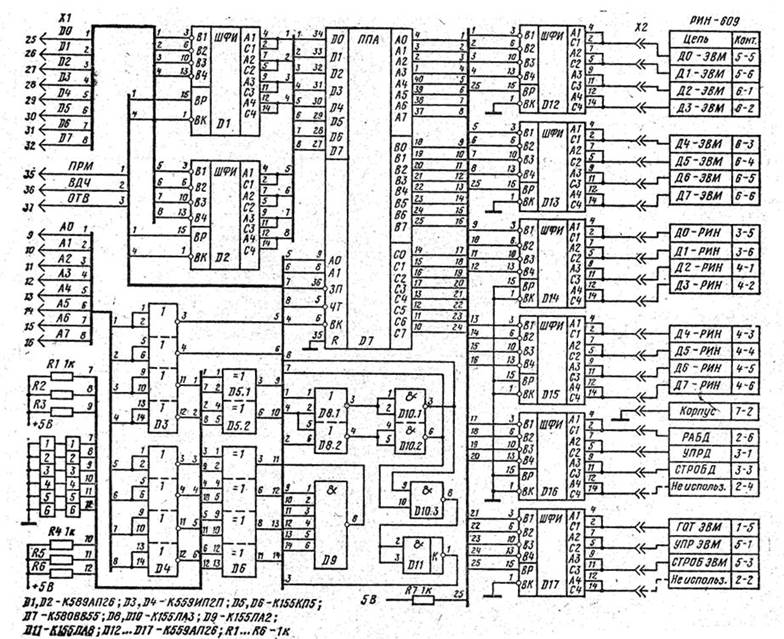

Из описанных выше микросхем необходимо смоделировать схему следующего вида:

Текст файла верхнего уровня (Top-level file).

library IEEE;

use IEEE.std_logic_1164.all;

entity top2 is

port (

d: inout STD_LOGIC_VECTOR (7 downto 0);

a: in STD_LOGIC_VECTOR (7 downto 0);

r: in STD_LOGIC_VECTOR (12 downto 7);

prm: in STD_LOGIC;

vdch: in STD_LOGIC;

otv: out STD_LOGIC;

devm: inout STD_LOGIC_VECTOR (7 downto 0);

rin: inout STD_LOGIC_VECTOR (7 downto 0);

rabd: inout STD_LOGIC;

uprd: inout STD_LOGIC;

strobd: inout STD_LOGIC;

gotevm: inout STD_LOGIC;

uprevm: inout STD_LOGIC;

strobevm: inout STD_LOGIC;

nu1:inout STD_LOGIC;

nu2:inout STD_LOGIC

);

end top2;

architecture structure of top2 is

component K559_1 is

port (

a1: in STD_LOGIC;

a2: in STD_LOGIC;

a3: in STD_LOGIC;

a4: in STD_LOGIC;

a5: in STD_LOGIC;

a6: in STD_LOGIC;

a7: in STD_LOGIC;

a8: in STD_LOGIC;

b1: out STD_LOGIC;

b2: out STD_LOGIC;

b3: out STD_LOGIC;

b4: out STD_LOGIC

);

end component K559_1;

component K155LA3 is

port (

a1: in STD_LOGIC;

a2: in STD_LOGIC;

b1: out STD_LOGIC

);

end component K155LA3;

component K155LA2 is

port (

a1: in STD_LOGIC;

a2: in STD_LOGIC;

a3: in STD_LOGIC;

a4: in STD_LOGIC;

a5: in STD_LOGIC;

a6: in STD_LOGIC;

b1: out STD_LOGIC

);

end component K155LA2;

component K155_2_OR_NOT is

port (

a1: in STD_LOGIC;

a2: in STD_LOGIC;

b1: out STD_LOGIC

);

end component K155_2_OR_NOT;

component K155KP5 is

port (

a1: in STD_LOGIC;

a2: in STD_LOGIC;

a3: in STD_LOGIC;

a4: in STD_LOGIC;

b1: out STD_LOGIC;

b2: out STD_LOGIC

);

end component K155KP5;

component K580BB55 is

port (

a: in STD_LOGIC_VECTOR (1 downto 0);

cs: in STD_LOGIC;

rd: in STD_LOGIC;

wr: in STD_LOGIC;

d: inout STD_LOGIC_VECTOR (7 downto 0);

ba: inout STD_LOGIC_VECTOR (7 downto 0);

bb: inout STD_LOGIC_VECTOR (7 downto 0);

bc: inout STD_LOGIC_VECTOR (7 downto 0)

);

end component K580BB55;

component K589AP26 is

port (

CS: in STD_LOGIC;

DCE: in STD_LOGIC;

DI: in STD_LOGIC_VECTOR (3 downto 0);

DO: out STD_LOGIC_VECTOR (3 downto 0);

DB: inout STD_LOGIC_VECTOR (3 downto 0)

);

end component K589AP26;

signal s,p:std_logic_vector(3 downto 0);

signal sa,sb,sc:std_logic_vector(7 downto 0);

signal b1,b2,b3,b4,

c1,c2,c3,c4,

m1,m2,m3,m4,m5,m6,

D9_out,or1,or2,outD10_1,outD10_2,outD10_3:std_logic;

begin

MAG_PR_D3:K559_1 port map(a(0),a(0),a(1),a(1),a(2),a(2),a(3),a(3),

b1,b2,b3,b4);

MAG_PR_D4:K559_1 port map(a(4),a(4),a(5),a(5),a(6),a(6),a(7),a(7),

c1,c2,c3,c4);

MUX_1:K155KP5 port map(b3,r(7),b4,r(8),m1,m2);

MUX_2:K155KP5 port map(c1,r(9),c2,r(10),m3,m4);

MUX_3:K155KP5 port map(c3,r(11),c4,r(12),m5,m6);

D9:K155LA2 port map(m1,m2,m3,m4,m5,m6,D9_out);

D8_1:K155_2_OR_NOT port map(prm,D9_out,or1);

D8_2:K155_2_OR_NOT port map(vdch,D9_out,or2);

D10_1:K155LA3 port map(or1,or1,outD10_1);

D10_2:K155LA3 port map(or2,or2,outD10_2);

D10_3:K155LA3 port map(outD10_1,outD10_2,outD10_3);

D11:K155LA3 port map(outD10_3,outD10_3,otv);

D1:K589AP26 port map(db(0)=>d(0),db(1)=>d(1),db(2)=>d(2),db(3)=>d(3),

do=>s,

di=>s,

cs=>D9_out,dce=>prm);

D2:K589AP26 port map(db(0)=>d(4),db(1)=>d(5),db(2)=>d(6),db(3)=>d(7),

do=>p,

di=>p,

cs=>D9_out,dce=>prm);

D7:K580BB55 port map(d(0)=>s(0),

d(1)=>s(1),

d(2)=>s(2),

d(3)=>s(3),

d(4)=>p(0),

d(5)=>p(1),

d(6)=>p(2),

d(7)=>p(3),

a(0)=>b1,a(1)=>b2,

cs=>D9_out,rd=>outD10_1,wr=>outD10_2,

ba=>sa,

bb=>sb,

bc=>sc);

SHFI_D12:K589AP26 port map(db(0)=>sa(0),db(1)=>sa(1),db(2)=>sa(2),db(3)=>sa(3),

do(0)=>devm(0),do(1)=>devm(1),do(2)=>devm(2),do(3)=>devm(3),

di(0)=>devm(0),di(1)=>devm(1),di(2)=>devm(2),di(3)=>devm(3),

cs=>'0',dce=>'1');

SHFI_D13:K589AP26 port map(db(0)=>sa(4),db(1)=>sa(5),db(2)=>sa(6),db(3)=>sa(7),

do(0)=>devm(4),do(1)=>devm(5),do(2)=>devm(6),do(3)=>devm(7),

di(0)=>devm(4),di(1)=>devm(5),di(2)=>devm(6),di(3)=>devm(7),

cs=>'0',dce=>'1');

SHFI_D14:K589AP26 port map(db(0)=>sb(0),db(1)=>sb(1),db(2)=>sb(2),db(3)=>sb(3),

do(0)=>rin(0),do(1)=>rin(1),do(2)=>rin(2),do(3)=>rin(3),

di(0)=>rin(0),di(1)=>rin(1),di(2)=>rin(2),di(3)=>rin(3),

cs=>'0',dce=>'0');

SHFI_D15:K589AP26 port map(db(0)=>sb(4),db(1)=>sb(5),db(2)=>sb(6),db(3)=>sb(7),

do(0)=>rin(4),do(1)=>rin(5),do(2)=>rin(6),do(3)=>rin(7),

di(0)=>rin(4),di(1)=>rin(5),di(2)=>rin(6),di(3)=>rin(7),

cs=>'0',dce=>'0');

SHFI_D16:K589AP26 port map(db(0)=>sc(0),db(1)=>sc(1),db(2)=>sc(2),db(3)=>sc(3),

do(0)=>rabd,do(1)=>uprd,do(2)=>strobd,do(3)=>nu1,

di(0)=>rabd,di(1)=>uprd,di(2)=>strobd,di(3)=>nu1,

cs=>'0',dce=>'0');

SHFI_D17:K589AP26 port

Уважаемый посетитель!

Чтобы распечатать файл, скачайте его (в формате Word).

Ссылка на скачивание - внизу страницы.