МИНИСТЕРСТВО ОБРАЗОВАНИЯ РОССИЙСКОЙ ФЕДЕРАЦИИ

РЯЗАНСКАЯ ГОСУДАРСТВЕННАЯ РАДИОТЕХНИЧЕСКАЯ ФКАДЕМИЯ

Пояснительная записка к курсовой работе по курсу

“схемотехника”

«Моделирование цифровых устройств в »

среде проэктирования VHDL

Выполнил: ст. 146гр.

Проверил:

Асс. Каф. САПР ВС

Рязанская государственная радиотехническая академия

Кафедра САПР ВС

Тема: Проектирование цифровых устройств с использованием пакета VHDL

Срок представления к защите: 25 апреля 2004г.

Задание выдано 5 марта 2004г.

Задание принято к исполнению __________ /студент гр.../

Задание выдал __________ /асс. каф. САПР ВС Н.В./

Содержание :

Задание.........................................................................................................................1

Содержание................................................................................................................. 2

2. Описание работы компонентов микросхемы.....................................................4

2.1. Схема логического элемента К155ЛН1................. ......................................5

2.2. Схема логического элемента К555ЛЕ6 ........................................................6

2.3. Схема логического элемента К555ЛА3 .......................................................7

2.4. Схема логического элемента К155ТМ2 ......................................................8

2.5. Схема логического элемента К155ТМ8........................................................9

2.6. Схема логического элемента К589АП16....................................................11

3. Компоновка логических элементов в схему......................................................12

Заключение..................................................................................................................15

Список литературы.....................................................................................................16

Приложение ................................................................................................................17

Традиционный подход к проектированию дискретных вычислительных систем (ДС) состоит в последовательном решении задач анализа и оптимизации некоторого начального варианта проектируемой ДС. Поэтому давней мечтой разработчиков ДС было создание единых средств описания ДС, которые позволяли бы решать задачи верификации и синтеза схем с различной степенью детальности их описания и, таким образом, объединять этапы проектирования в единый процесс нисходящего проектирования "сверху вниз". Появление языка VHDL в определенной степени позволяет автоматизировать задачи проектирования от описания алгоритма функционирования ДС до реализации кристаллов микросхем. При этом понятие синтез следует определить как формализованный процесс построения схемы из некоторого заданного набора компонентов.

Языки описания аппаратуры (ЯОА/HDL - Hardware Digital Language) известны давно. Одним из первых более или менее удачных ЯОА был LOTIS - формальный язык, описывающий логические переменные и последовательностные схемы. Он разработан Шлэппи (IBM) в 1964 г. Затем в течение семидесятых годов в Европе и США было разработано много ЯОА, их насчитывалось более 200 -- отечественных и зарубежных. Самыми известными являются МОДИС, МОДИС-В78, Автокод, МПЛ, ОСС-2, ФОРОС, EPICURE, CDL, DDL, ISPS, CONLAN, HILO, CASCADE, REGLAN и др.

1) К155ЛН1 - логический элемент НЕ

2) К555ЛЕ6 – логический элемент ИЛИ-НЕ

3) К555ЛА3К555ЛП5 – логический элемент 2ИНЕ

4) К155ТМ2 – D-триггер

5) К155ТМ8 – набор из D-триггеров

6) К589АП16 – шинный формирователь

Логический элемент серии ТТЛ К155ЛН1 выполняет логическую функцию

не.

Схема электрическая принципиальная приведена на рис.1.

![]()

Рис.1. Схема электрическая принципиальная К155ЛН1

Данная схема реализует логическую функцию:

___

Y = X

Табл.1. Таблица истинности элемента не

|

X |

Y |

|

0 |

1 |

|

1 |

0 |

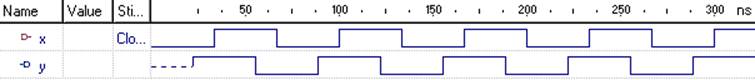

Временная диаграмма работы логического элемента К155ЛН1 с временем задержки tз=22 нс. Приведена на рис. 2.

Рис.2

![]() Логический

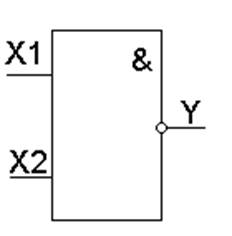

элемент ИЛИ-НЕ серии ТТЛ К555ЛЕ6 выполняет логическую функцию ИЛИ.

Логический

элемент ИЛИ-НЕ серии ТТЛ К555ЛЕ6 выполняет логическую функцию ИЛИ.

Схема электрически принципиальная приведена на рисунке 3.

Рис.3

Логическая функция элемента: Y=X1 V X2.

![]() Таблица истинности имеет вид:

Таблица истинности имеет вид:

|

Х1 |

Х2 |

Y |

|

H |

H |

B |

|

H |

B |

H |

|

B |

H |

H |

|

B |

B |

H |

Временная диаграмма работы логического элемента К555ЛЕ6 с временем задержки 24 нс на передний фронт и 24 нс на задний фронт приведена на рисунке 4.

Рис 4

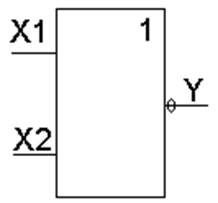

Логический элемент 2ИНЕ серии ТТЛ К555ЛА3 выполняет логическую функцию ИНЕ.

Схема электрически принципиальная приведена на рисунке 5.

Рис.5

![]() Логическая функция элемента: Y=X1 & X2.

Логическая функция элемента: Y=X1 & X2.

Таблица истинности имеет вид:

X1 |

X2 |

Y |

|

0 |

0 |

1 |

|

0 |

1 |

1 |

|

1 |

0 |

1 |

|

1 |

1 |

0 |

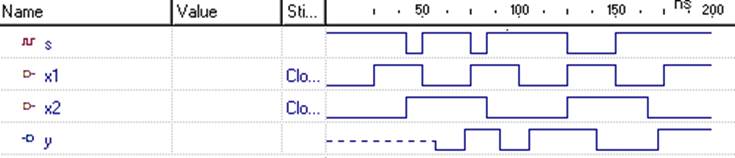

Временная диаграмма работы логического элемента К555ЛА3 с временем задержки 10нс приведена на рисунке 6.

Рис.6

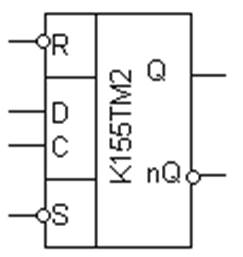

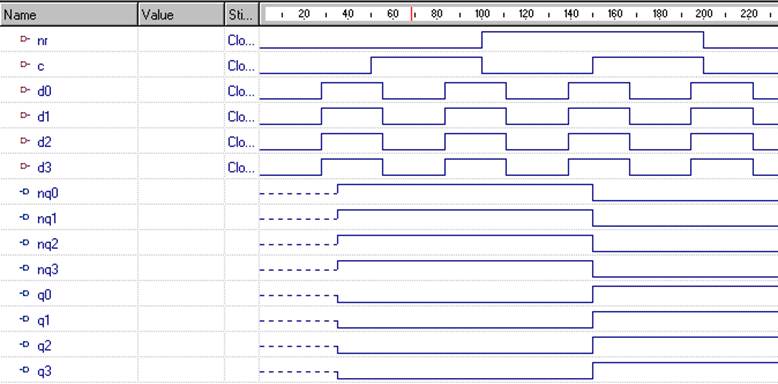

ТМ2 представляет собой D-триггер, имеет 4 входа: С синхроимпульс,D- сигнал синхронного управления, S,R- сигналы асинхронного управления.

Схема приведена на рисунке 7.

Рис7

Логика работы триггера К155ТМ2 приведена в таблице:

|

Режим работы |

Вход |

Выход |

||||

|

nS |

nR |

C |

D |

Q |

nQ |

|

|

Асинхронная установка |

H |

B |

X |

X |

B |

H |

|

Асинхронный сброс |

B |

H |

X |

X |

H |

B |

|

Неопределённость |

H |

H |

X |

X |

B |

B |

|

Загрузка 1 (установка) |

B |

B |

|

B |

B |

H |

|

Загрузка 0 (сброс) |

B |

B |

|

H |

H |

B |

![]()

- переход сигнала с 0 на 1.

Временные диаграммы триггера представлены на рисунке 8.

Рис.8

Рис.8

![]()

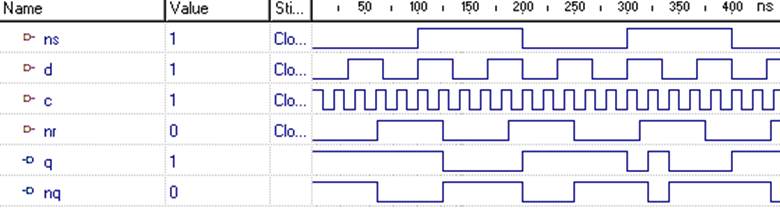

![]() ТМ8 представляет

собой набор из D-триггеров, имеющие общие входы

синхронного сброса R и тактового запуска С. В

микросхемах ТМ8 число триггеров 4 , у каждого есть выходы Q и Q.

ТМ8 представляет

собой набор из D-триггеров, имеющие общие входы

синхронного сброса R и тактового запуска С. В

микросхемах ТМ8 число триггеров 4 , у каждого есть выходы Q и Q.

Схема приведена на рисунке 9.

Рис9

|

Режим работы |

Вход |

Выход |

||||||

|

С |

Dn |

Qn |

|

||||

|

сброс |

Н |

Х |

Х |

Н |

B |

|||

|

Загрузка 1 |

В |

|

B |

B |

H |

|||

|

Загрузка 0 |

B |

|

H |

H |

B |

|||

![]() - переход сигнала с 0 на 1.

- переход сигнала с 0 на 1.

Временные диаграммы триггера представлены на рисунке 10.

Рис10

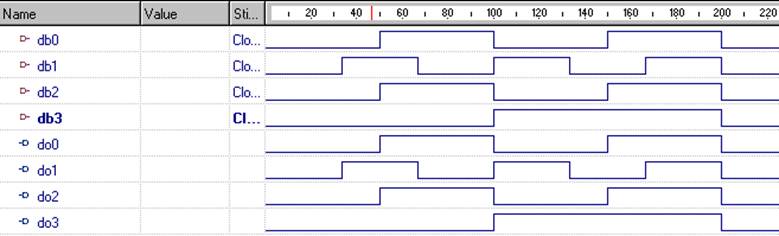

2.6 Шинный формирователь К589АП16

Микросхема К589АП16 – шинный формирователь , являющийся параллельным двунаправленным формирователем сигналов для управления магистралями (шинами) в цифровых вычислительных устройствах и представляют собой ;-канальные коммутаторы, имеющие в каждом канале одну шину только для приема информации, одну шину для только для выдачи информации и одну двунаправленную шину для приема и выдачи информации. Рис13

Рис13

|

Состояние входов |

Направление передачи информации |

Выходы в состояние «выключено» |

|

|

CS |

DCE |

||

|

0 |

0 |

От входов DI0-DI3 до выходов DB0-DB3 |

DO0-DO3 |

|

0 |

1 |

От входов DB0-DB3 до выходов DO0-DO3 |

DB0-DB3 |

|

1 |

1 |

Передача отсутствует |

DO0-DO3, DB0-DB3 |

В моей схеме имеем 2-ой случай.

Временные диаграммы представлены на рисунке 14.

Рис14

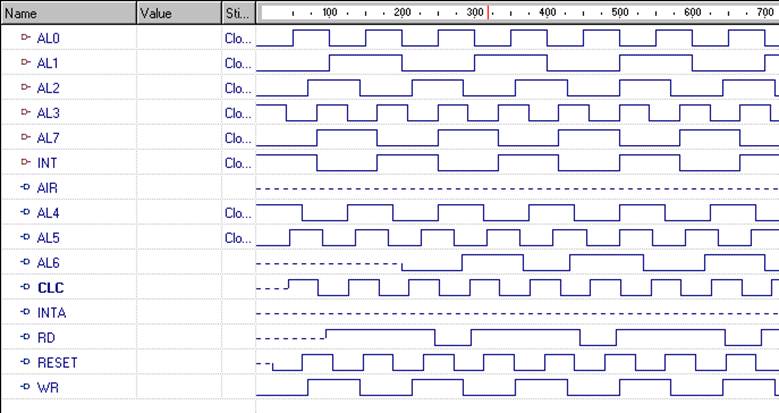

Компоненты схемы контроллера прерываний соединяются, как показано на рис.15.

В результате выполнения курсовой работы мы изучили метолы проектирования и разработки цифровых устройств. А также нами было изучено практическое применение ЭВМ для проектирования цифровых устройств на язык описания Active-VHDL.

В итоге мы получили программу которая позволяет моделировать работу схемы контроллера прерываний. Результаты моделирования можно смотреть в файлах отчёта и на временных диаграммах, что дает право редактировать схему в процессе проектирования, тем самым добиваясь верного схемного решения .

Приложение :

Описание логического элемента К555ЛЕ6 на языке VHDL:

library IEEE;

use IEEE.std_logic_1164.all;

entity k555le6 is

port (

x1: in STD_LOGIC;

x2: in STD_LOGIC;

y: out STD_LOGIC

);

end k555le6;

architecture k555le6 of k555le6 is

signal s:std_logic;

begin

process(x1,x2,s)

begin

s<=x1 or x2;

if s='1'and s'last_value='0' then

y<=not s after 24 ns;

end if;

if s='0'and s'last_value='1' then

y<=not s after 24 ns;

end if;

end process;

end k555le6;

Описание триггера К555ТМ2 на языке VHDL:

library IEEE;

use IEEE.std_logic_1164.all;

entity k555tm2 is

port (

ns: in STD_LOGIC;

d: in STD_LOGIC;

c: in STD_LOGIC;

nr: in STD_LOGIC;

q: out STD_LOGIC;

nq: out STD_LOGIC

);

end k555tm2;

architecture k555tm2 of k555tm2 is

begin

process(c,nr,ns,d)

begin

if ns='0' and nr='1'then

q<='1';

nq<='0';

end if;

if ns='1' and nr='0'then

q<='0';

nq<='1';

end if;

if ns='0' and nr='0'then

q<='1';

nq<='1';

end if;

if ns='1' and nr='1' and c'event and c='1' then

if d='1'then

q<='1';

nq<='0';

end if;

if d='0' then

q<='0';

nq<='1';

end if;

end if;

end process;

end k555tm2;

Описание логического элемента К589АП16 на языке VHDL:

library IEEE;

use IEEE.std_logic_1164.all;

entity k589ap16 is

port (

db0: in STD_LOGIC;

db1: in STD_LOGIC;

db2: in STD_LOGIC;

db3: in STD_LOGIC;

do0: out STD_LOGIC;

do1: out STD_LOGIC;

do2: out STD_LOGIC;

do3: out STD_LOGIC;

);

end k589ap16;

architecture k589ap16 of k589ap16 is

begin

process(db0,db1,db2,db3)

begin

do0<=db0;

do1<=db1;

do2<=db2;

do3<=db3;

end process;

end k589ap16;

Описание триггера К155ТМ8 на языке VHDL:

library IEEE;

use IEEE.std_logic_1164.all;

entity k155tm8 is

port (

d0: in STD_LOGIC;

d1: in STD_LOGIC;

d2: in STD_LOGIC;

d3: in STD_LOGIC;

c: in STD_LOGIC;

nr: in STD_LOGIC;

q0: out STD_LOGIC;

q1: out STD_LOGIC;

q2: out STD_LOGIC;

q3: out STD_LOGIC;

nq0: out STD_LOGIC;

nq1: out STD_LOGIC;

nq3: out STD_LOGIC

);

end k155tm8;

architecture k155tm8 of k155tm8 is

begin

process(c,nr,d0,d1,d2,d3)

begin

if nr='0'then

q0<='0'after 35 ns;

q1<='0'after 35 ns;

q2<='0'after 35 ns;

q3<='0'after 35 ns;

nq0<='1'after 35 ns;

nq1<='1'after 35 ns;

nq3<='1'after 35 ns;

end if;

if nr='1' and c'event and c='1' then

if d0='1'and d1='1'and d2='1'and d3='1' then

q0<='1';

q1<='1';

q2<='1';

q3<='1';

nq0<='0';

nq1<='0';

nq3<='0';

end if;

if d0='0'and d1='0'and d2='0'and d3='0' then

q0<='0';

q1<='0';

q2<='0';

q3<='0';

nq0<='1';

nq1<='1';

nq3<='1';

end if;

end if;

end process;

end k155tm8;

Описание логического элемента К155ЛН1 на языке VHDL:

library IEEE;

use IEEE.std_logic_1164.all;

entity k155ln1 is

port (

x: in STD_LOGIC;

y: out STD_LOGIC

);

end k155ln1;

architecture k155ln1 of k155ln1 is

begin

process(x)

begin

y<=not x after 22 ns;

end process;

end k155ln1;

Описание логического элемента К555ЛА3 на языке VHDL:

library IEEE;

use IEEE.std_logic_1164.all;

entity k555la3 is

port (

x1: in STD_LOGIC;

x2: in STD_LOGIC;

y: out STD_LOGIC

);

end k555la3;

architecture k555la3 of k555la3 is

signal s: std_logic;

begin

process(x1,x2,s)

begin

s<= x1 nand x2;

if s='1' and s'last_value='0' then

y<=s after 10 ns;

end if;

if s='0' and s'last_value='1' then

y<=s after 10 ns;

end if;

end process;

end k555la3;

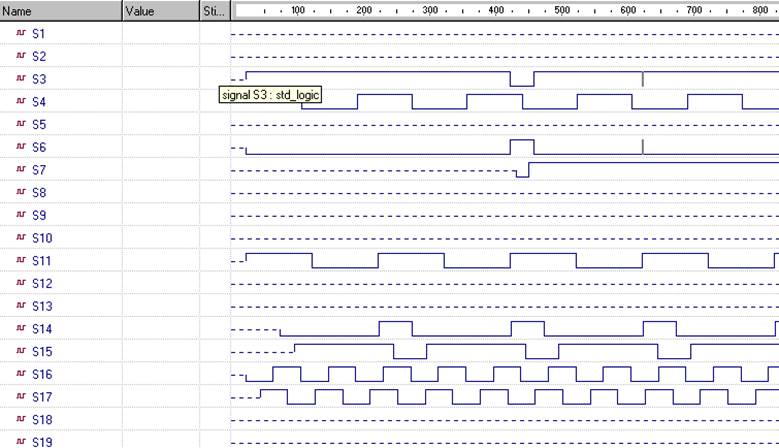

Описание структуры схемы контроллера прерываний на языке VHDL:

library IEEE;

use IEEE.std_logic_1164.all;

use IEEE.std_logic_unsigned.all;

entity Top is

port (

AL0: in std_logic;

AL1: in std_logic;

AL2: in std_logic;

AL3: in std_logic;

INT: in std_logic;

AL7: in std_logic;

WR: out std_logic;

RD: out std_logic;

RESET: out std_logic;

CLC: out std_logic;

OU: out std_logic;

INTA: out std_logic;

AL6: out std_logic;

AL5: out std_logic;

AL4: out std_logic;

AIR: out std_logic

);

end Top;

architecture Structure of Top is

component k555le6 is

port (

x1: in STD_LOGIC;

x2: in STD_LOGIC;

y: out STD_LOGIC

);

end component;

component k555tm2 is

port (

ns: in STD_LOGIC;

d: in STD_LOGIC;

c: in STD_LOGIC;

nr: in STD_LOGIC;

q: out STD_LOGIC;

nq: out STD_LOGIC

);

end component;

component k589ap16 is

port (

db0: in STD_LOGIC;

db1: in STD_LOGIC;

db2: in STD_LOGIC;

db3: in STD_LOGIC;

do0: out STD_LOGIC;

do1: out STD_LOGIC;

do2: out STD_LOGIC;

do3: out STD_LOGIC

);

end component;

component k155tm8 is

port (

d0: in STD_LOGIC;

d1: in STD_LOGIC;

d2: in STD_LOGIC;

d3: in STD_LOGIC;

c: in STD_LOGIC;

nr: in STD_LOGIC;

q0: out STD_LOGIC;

q1: out STD_LOGIC;

q2: out STD_LOGIC;

q3: out STD_LOGIC;

nq0: out STD_LOGIC;

nq1: out STD_LOGIC;

nq3: out STD_LOGIC

);

end component;

component k155ln1 is

port (

x: in STD_LOGIC;

y: out STD_LOGIC

);

end component;

component k555la3 is

port (

x1: in STD_LOGIC;

x2: in STD_LOGIC;

y: out STD_LOGIC

);

end component;

signal S1,S2,S3,S4,S5,S6,S7,S8,S9,S10,S11,S12,S13,S14,S15,S16,S17,

S18,S19,S20,S21,S22,SQ3,SQ2,SQ1,SQ0,SP1,SP2,SP3,SP4,SP5,SP6,SP7,SP8: std_logic;

begin

D6: k589ap16

port

Уважаемый посетитель!

Чтобы распечатать файл, скачайте его (в формате Word).

Ссылка на скачивание - внизу страницы.