Рязанская государственная радиотехническая академия

Кафедра САПР ВС

Тема: Проектирование цифровых устройств с использованием пакета VHDL

Срок представления к защите: 20 мая 2002г.

Задание принято к исполнению __________ /студент гр.045 /

Задание выдал __________ /асс. каф. САПР ВС Н.В./

СОДЕРЖАНИЕ

1.1. Схема К155ЛА3 (2-И-НЕ)

1.2. Схема К155ЛЕ1 (2-ИЛИ-НЕ)

1.3. Схема К155ЛН1 (инвертор)

1.4. Схема К555ТМ2 (D-триггер)

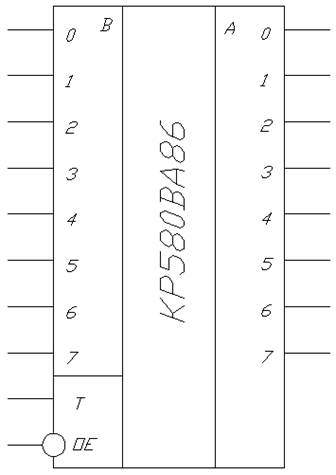

1.5. Схема К580ВА86 (шинный формирователь)

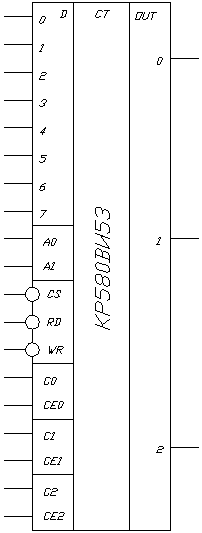

1.6. Схема К580ВИ53 (программируемый таймер)

ЗАКЛЮЧЕНИЕ

ПРИЛОЖЕНИЯ

Приложение 1: Текст программы, моделирующей работу схемы

Приложение 2: Результаты моделирования схемы

Широкое распространение цифровой техники, ее доступность обывателю и дешевизна обусловлены появлением интегральных микросхем. Цифровые устройства, собранные на базе дискретных транзисторов и диодов, имели значительные габаритные размеры и массу; обладали невысокой надежностью в связи с наличием большого числа элементов и паяных связей между ними. Интегральные микросхемы, содержащие в своем составе десятки и сотни тысяч компонентов, позволили по-новому подойти к проектированию и изготовлению цифровых устройств. Надежность одной микросхемы практически не зависит от количества включенных в нее элементов и близка к надежности одиночного транзистора, а потребляемая мощность в пересчете на отдельный компонент уменьшается с ростом степени интеграции.

В процессе усовершенствования интегральных технологий стало возможным создание сложнейших устройств, надежных и обладающих малыми габаритами и высоким быстродействием.

1. МОДЕЛИРОВАНИЕ ЭЛЕМЕНТОВ

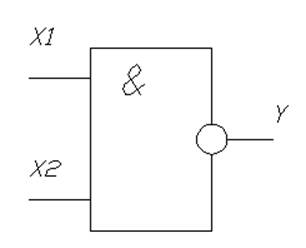

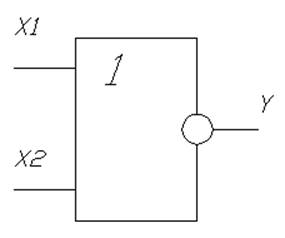

1.1. Схема К155ЛА3( 2-И-НЕ)

Данная схема реализует логическую функцию

Y = not ( X1 and X2 )

Таблица истинности выглядит следующим образом:

|

X1 |

X2 |

Y |

|

0 |

0 |

0 |

|

0 |

1 |

1 |

|

1 |

0 |

1 |

|

1 |

1 |

1 |

library IEEE;

use IEEE.std_logic_1164.all;

entity K155LA3 is

port (

x1: in STD_LOGIC;

x2: in STD_LOGIC;

y: out STD_LOGIC

);

end K155LA3;

architecture K155LA3 of K155LA3 is

begin

-- <<enter your statements here>>

process (x1,x2)

begin

y <= not(x1 and x2)after 22 ns;

end process;

end K155LA3;

Временные диаграммы

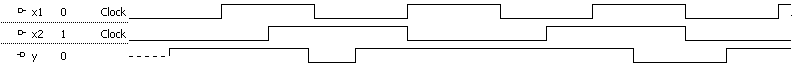

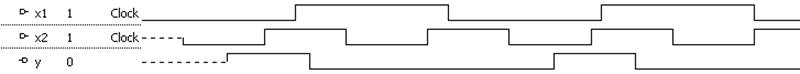

1.2. Схема К155ЛЕ1 ( 2-ИЛИ-НЕ)

Данная схема реализует логическую функцию

Y = not ( X1 or X2 )

Таблица истинности выглядит следующим образом:

|

X1 |

X2 |

Y |

|

0 |

0 |

1 |

|

0 |

1 |

0 |

|

1 |

0 |

0 |

|

1 |

1 |

0 |

library IEEE;

use IEEE.std_logic_1164.all;

entity K155LE1 is

port (

x1: in STD_LOGIC;

x2: in STD_LOGIC;

y: out STD_LOGIC

);

end K155LE1;

architecture K155LE1 of K155LE1 is

begin

-- <<enter your statements here>>

Process(x1,x2)

begin

Y<=not(X1 or X2) after 22ns;

end process;

end K155LE1;

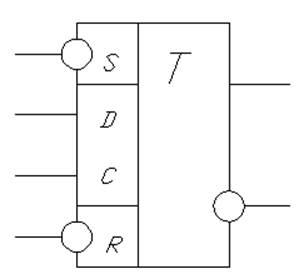

Временные диаграммы

1.2.

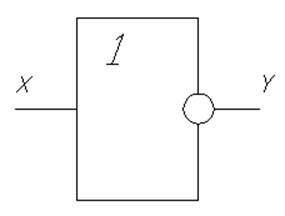

Схема К155ЛН1

Схема К155ЛН1

Данная схема реализует логическую функцию

Y = not ( X )

Таблица истинности выглядит следующим образом:

|

X |

Y |

|

0 |

1 |

|

1 |

0 |

library IEEE;

use IEEE.std_logic_1164.all;

entity K155LN1 is

port (

x: in STD_LOGIC;

y: out STD_LOGIC

);

end K155LN1;

architecture K155LN1 of K155LN1 is

begin

-- <<enter your statements here>>

process (x)

begin

y <= not(x)after 22 ns;

end process;

end K155LN1;

Временные диаграммы

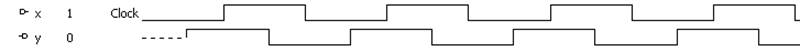

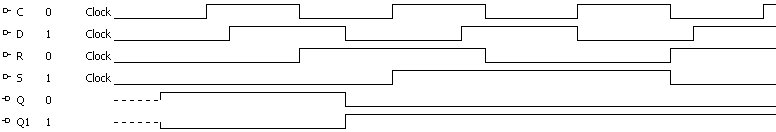

1.3.  Схема К555ТМ2 (D-триггер)

Схема К555ТМ2 (D-триггер)

- С – вход тактовых импульсов.

- D – вход установки триггера в состояние, в котором находится сигнал, поступающий на этот вход по спадам тактовых импульсов.

- R,S – управляющие входы (сигнал R устанавливает триггер в ‘1’, сигнал S – в ‘0’, если и R, и S равны ‘1’, то триггер устанавливается в ‘1’).

library IEEE;

use IEEE.std_logic_1164.all;

entity k155tm2 is

port (

R: in STD_LOGIC;

D: in STD_LOGIC;

C: in STD_LOGIC;

S: in STD_LOGIC;

Q: out STD_LOGIC;

Q1: out STD_LOGIC

);

end k155tm2;

architecture k155tm2 of k155tm2 is

begin

-- <<enter your statements here>>

process (s,r,c,d)

variable q0,a: std_logic;

begin

a:='1';

if R='1'and S='0' and (C='1' or C='0')and (D='1' or D='0')then q0:='0';

else

if R='0' and S='1' and (C='1' or C='0')and (D='1' or D='0') then q0:='0';

else

If R='1' and S='1' then

if C'event and C='1' and D='1' then q0:='1';

else

if C'event and C='1' and D='0' then q0:='0';

end if;

end if;

else

if R='0' and S='0'and(C='1' or C='0')and (D='1' or D='0') then q0:=a;

end if;

end if;

end if;

end if;

q <= q0 after 25ns;

a := q0;

q1<=not(q0) after 25ns;

end process;

end k155tm2;

Временные диаграммы

1.4. Схема КР580ВА86 ( шинный формирователь)

Это микросхема представляет собой двунаправленный восьмиразрядный шинный формирователь, предназначенный для обмена данными между процессором и системной шиной.

В зависимости от управляющих сигналов ОЕ и Т микросхемы могут работать в режиме передачи А®В, В®А или в режиме «выключено»:

- при ОЕ = 0, Т = 1 – направление передачи А®В

- при ОЕ = 0, Т = 0 – направление передачи В®А

- при ОЕ = 1, Т =Х – на выводах А и В третье состояние (Z)

library IEEE;

use IEEE.std_logic_1164.all;

entity K580VA86 is

port (

t: in STD_LOGIC;

de: in STD_LOGIC;

x: inout STD_LOGIC_vector(7 downto 0);

y: inout STD_LOGIC_VECTOR(7 downto 0)

);

end K580VA86;

architecture K580VA86 of K580VA86 is

begin

-- <<enter your statements here>>

process (t,de,x,y)

variable i:integer;

begin

-- signal x -> y

if (de' event)and (de='0') and (t='1') then

for i in 0 to 7 loop

y(i)<= x(i) after 30 ns;

end loop;

else

if (t' event)and (t='1')and(de='0') then

for i in 0 to 7 loop

y(i)<= x(i) after 22 ns;

end loop;

end if;

for i in 0 to 7 loop

if (x(i)' event)and(t='1')and(de='0')then

y(i)<= x(i) after 22 ns;

end if;

end loop;

end if;

-- signal y -> x

if (de' event)and (de='0') and (t='0') then

for i in 0 to 7 loop

x(i)<= y(i) after 30 ns;

end loop;

else

if (t' event)and (t='0')and(de='0') then

for i in 0 to 7 loop

x(i)<= y(i) after 22 ns;

end loop;

end if;

for i in 0 to 7 loop

if (y(i)' event)and(t='0')and(de='0')then

x(i)<= y(i) after 22 ns;

end if;

end loop;

end if;

-- Z sostoyanie

if de' event and de='1' then

if t='0' then

for i in 0 to 7 loop

x(i)<='Z'after 18 ns;

end loop;

end if;

if t='1' then

for i in 0 to 7 loop

y(i)<='Z' after 18 ns;

end loop;

end if;

end if;

end process;

end K580VA86;

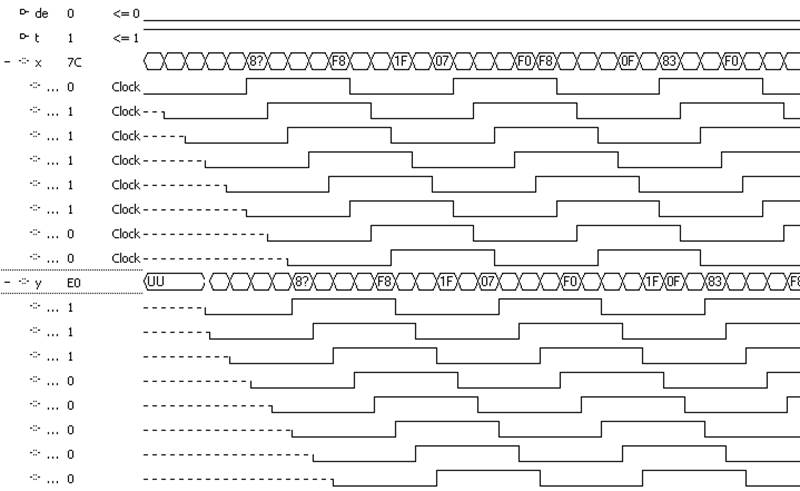

Временные диаграммы

1.6. Схема КР580ВИ53 (программируемый таймер)

Данная

схема представляет собой таймер с тремя независимо-программируемыми ка налами и может работать в шести различных режимах.:

налами и может работать в шести различных режимах.:

Режим 0: Прерывание терминального счета.

Режим 1:Ждущий мультивибратор.

Режим 2: Генератор импульсный.

Режим 3: Генератор меандра.

Режим 4: Одиночный программно-формируемый стробирующий сигнал.

Режим 5: Одиночный аппаратно стробирующий сигнал.

Из этих режимов нас интересует только один – ждущий мультивибратор.

Входы микросхемы КР580ВИ53:

- С0, С1, С2 – входы синхронизации каналов.

- СЕ0, СЕ1, СЕ2 – входы каналов, по переднему фронту сигналов которых осуществляется загрузка счетчика.

- А1, А0 – сигналы выбора канала.

- OUT0, OUT1, OUT2 – выходы каналов.

- D(0..7) – входы, на которые подается управляющее слово. В момент прихода положительного фронта сигнала СЕ(i) после предварительного выбора канала с них считывается начальное значение счетчика.

Текст программы

-- File: KR580vi83.1

-- created by Design Wizard: 05/14/02 19:11:17

-library IEEE;

use IEEE.std_logic_1164.all;

entity KR580vi83 is

port (

D: in STD_LOGIC_VECTOR (7 downto 0);

C: in STD_LOGIC_VECTOR (2 downto 0);

CE: in STD_LOGIC_VECTOR (2 downto 0);

A: in STD_LOGIC_VECTOR (4 downto 0);

Q: out STD_LOGIC_VECTOR (2 downto 0)

);

end KR580vi83;

architecture KR580vi83 of KR580vi83 is

begin

process (D,C,CE,A)

type Tmode is array (0 to 2) of integer;

variable counter : Tmode;

variable i,n,c1: integer;

function st (X : STD_LOGIC) return integer is

begin

if X = '1' then return 1; end if;

if X = '0' then return 0; end if;

end st;

Function stop(D: std_logic_vector(7 downto 0))return integer is

begin

return 128*st(d(7))+64*st(d(6))+32*st(d(5))+16*st(d(4))+8*st(d(3))+4*st(d(2))+2*st(d(1))+1*st(d(0));

end stop;

procedure quit (i: integer)is

begin

if CE(i)'event and CE(i)='0' then counter(i):=0; end if;

if CE(i)'event and CE(i)='1' then counter(i):=stop(D); end if;

if counter(i)>0 and C(i)'event and C(i)='0' then

Q(i)<='0';

counter(i):=counter(i)-1;

end if;

if counter(i)=0 and C(i)'event and C(i)='0' then Q(i)<='1'; end if;

end quit;

begin

if a(4)'event or a(3)'event then

if a(4)='0' and a(3)='0' then i:=0; end if;

if a(4)='0' and a(3)='1' then i:=1; end if;

if a(4)='1' and a(3)='0' then i:=2; end if;

end if;

for n in 0 to 2 loop

if n=i then quit(n);end if;

end loop;

end process;

end KR580vi83;

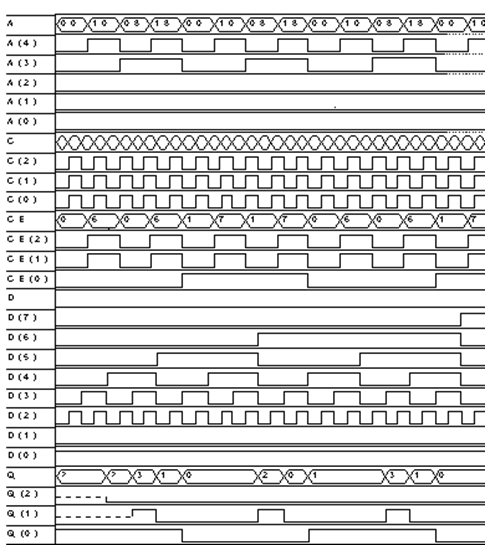

Временные диаграммы.

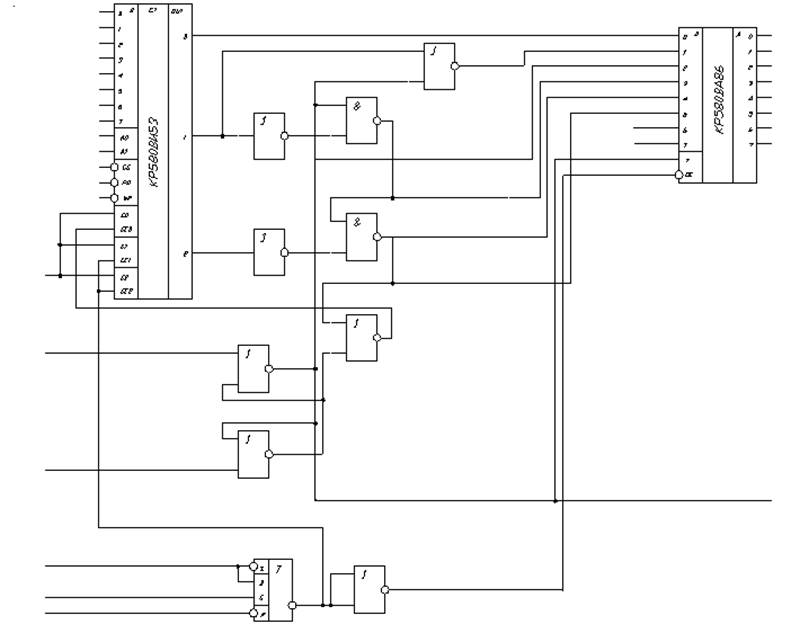

2. МОДЕЛИРОВАНИЕ СХЕМЫ

Из описанных ранее на языке VHDL элементов моделируется схема следующего вида:

Программа, моделирующая работу схемы, и временные диаграммы представлены в приложениях.

БИБЛИОГРАФИЧЕСКИЙ СПИСОК

1. Шило В. Л. Популярные цифровые микросхемы. Челябинск: Металлургия, 1989. 352 с.

2. Микропроцессоры и микропроцессорные комплекты интегральных микросхем: В 2 томах. Том 1. / Под ред. В.А. Шахнова. М.: Радио и связь, 1988. 368 с.

3. Схемотехника ЭВМ / Под ред. Г.Н. Соловьева. М.: Высшая школа, 1985. 391 с.

ЗАКЛЮЧЕНИЕ

В процессе выполнения данной курсовой работы были изучены методы проектирования и разработки цифровых устройств в соответствии с данными технического задания. Практическая сторона задания (проектирование кристалла БИС) выполнялась с использованием пакета описания цифровых схем Activ-VHDL. Важным достоинством этого пакета является возможность дополнения его библиотек собственными элементами, что дает проектировщику большую свободу действий.

Использование ЭВМ делает проектирование более простым и эффективным.

ПРИЛОЖЕНИЕ 1: Текст программы, моделирующей схему.

-- File: Shema.vhd

-- created by Design Wizard: 05/16/02 00:41:37

-library IEEE;

use IEEE.std_logic_1164.all;

entity Shema is

port (

D: in STD_LOGIC_VECTOR (7 downto 0);

A: in STD_LOGIC_VECTOR (4 downto 0);

b: out STD_LOGIC_VECTOR (7 downto 0);

F2TTL: in STD_LOGIC;

x1: in STD_LOGIC;

x2: in STD_LOGIC;

s: in STD_LOGIC;

c: in STD_LOGIC;

r: in STD_LOGIC;

from1: out STD_LOGIC;

from2: out STD_LOGIC

);

end Shema;

architecture sructure of Shema is

component K155LA3 is

port (

x1: in STD_LOGIC;

x2: in STD_LOGIC;

y: out STD_LOGIC

);

end component K155LA3;

component K155LE1 is

port (

x1: in STD_LOGIC;

x2: in STD_LOGIC;

y: out STD_LOGIC

);

end component K155LE1;

component K155LN1 is

port (

x: in STD_LOGIC;

y: out STD_LOGIC

);

end component K155LN1;

component K155TM2 is

port (

R: in STD_LOGIC;

D: in STD_LOGIC;

C: in STD_LOGIC;

S: in STD_LOGIC;

Q: out STD_LOGIC;

Q1: out STD_LOGIC

);

end component k155tm2;

component K580VA86 is

port (

t: in STD_LOGIC;

de: in STD_LOGIC;

x: in STD_LOGIC_vector(7 downto 0);

y: out STD_LOGIC_VECTOR(7 downto 0)

);

end component K580VA86;

component KR580VI53 is

port (

D: in STD_LOGIC_VECTOR (7 downto 0);

C: in STD_LOGIC_VECTOR (2 downto 0);

CE: in STD_LOGIC_VECTOR (2 downto 0);

A: in STD_LOGIC_VECTOR (4 downto 0);

Q: out STD_LOGIC_VECTOR (2 downto 0)

);

end component KR580vi53;

signal p1,p2,p3,p4,p5,p6,p7,p8,p9,p10,p11,p12,p13:STD_LOGIC

Уважаемый посетитель!

Чтобы распечатать файл, скачайте его (в формате Word).

Ссылка на скачивание - внизу страницы.