4.04.2003.

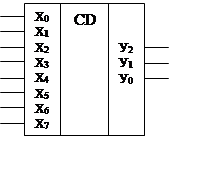

Шифраторы.

Шифраторы выполняются в виде отдельных микросхем (МС) или встраиваются в состав ?

Принцип построения рассмотрим на примере двоичного шифратора:

Принцип построения рассмотрим на примере двоичного шифратора:

xi – входы шифратора. На один из входов нужно подавать 1, на остальные 0.

yi – выходы шифратора.

y2y1y0 – двоичное число равное номеру входа, на который подали 1.

Такой шифратор не работает, если 1 подана на два или более входов (неприоритетный шифратор). Пример: 155ИВ1

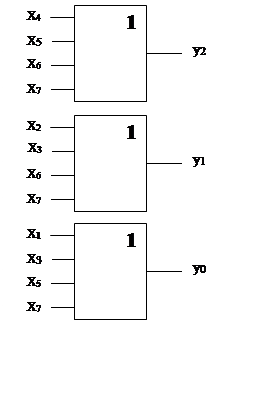

У0 = 1 , если X1 = 1, Хi ≠ 0 = 0

У0 = 1 , если число имеет вид: ХХ1

Х1=1, Х3=1, Х5=1, Х7=1 (т.е. нечетные входы = 1)

У1 = 1 , если число имеет вид: Х1Х

Х2, Х3, Х6, Х7

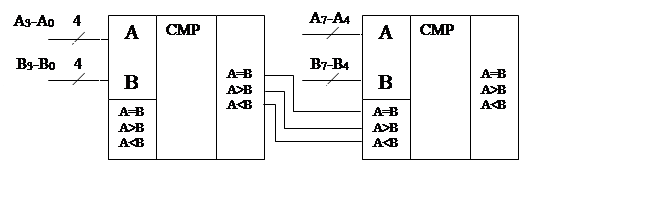

Компараторы кодов (Схемы сравнения кодов).

Существуют компараторы для сравнения 2-х байтов с выработкой одного флага (равенство), 4-разрядные компараторы с выработкой трех флагов (=, >, <). Из 4-разрядных можно строить многоразрядные компараторы.

Рассмотрим 4-разрядные компараторы. Пример: 555СП1

|

Применяется для аппаратной реализации алгоритма, содержащего условные вершины (переходы).

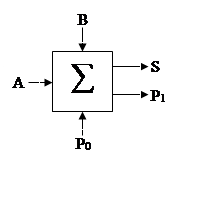

Сумматоры.

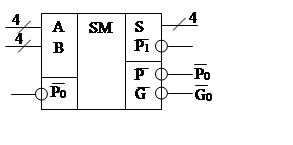

Сумматоры бывают 1-разрядными, 2-разрядными либо 4-разрядные. Выполняют арифметическое сложение.

|

A, B – слагаемые

P0 – входной перенос

P1 – выходной перенос

S – сумма

2-разрядные сумматоры отличаются разрядностью А и В. Они представляют собой 2-разрядные шины. Аналогично 4-разрядные.

|

P, G нужны при построении многоразрядных сумматоров, когда требуется организовать перенос между микросхемами.

При последовательном переносе общее время сложения:

t∑ = n∙t∑1

Выходной перенос организуется так: выход Р1 подключается к входу P0 следующей схемы.

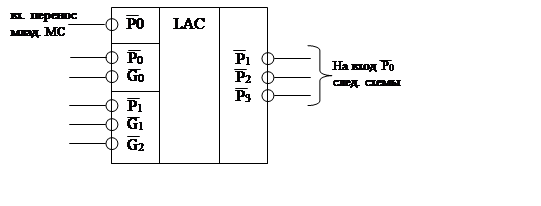

Ускоренный перенос:

|

P0G0, P1G1, P2G2 подключаются к выходам предыдущей схемы.

Формирует входные переносы для старших схем сумматора.

В состав сумматора входят две логические схемы: схема распространения переноса, схема генерации переноса. Эти две схемы выдают информацию: возможен перенос или нет.

Одна схема ускоренного переноса предназначена для обслуживания 4-х микросхем сумматора с возможностью каскадирования.

t∑ = t∑1 + tсуп

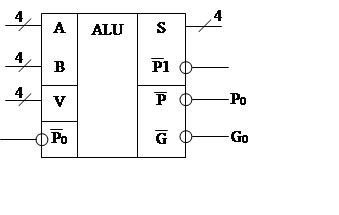

Арифметико-Логическое Устройство (АЛУ).

A, B – операнды

P0 – входной перенос

V – код микрооперации

S – результат

P1 – выходной перенос

Количество операций : 25.

ИП3 выполняет 16 арифметических и 16 логических операций.

МС АЛУ используется только при аппаратной реализации алгоритма. АЛУ входит в состав любой БИС.

Мультиплексоры.

Уважаемый посетитель!

Чтобы распечатать файл, скачайте его (в формате Word).

Ссылка на скачивание - внизу страницы.