МИНИСТЕРСТВО ОБРАЗОВАНИЯ РОССИЙСКОЙ ФЕДЕРАЦИИ

РЯЗАНСКАЯ ГОСУДАРСТВЕННАЯ РАДИОТЕХНИЧЕСКАЯ АКАДЕМИЯ

Пояснительная записка к курсовой работе по курсу

“схемотехника”

«Моделирование цифровых устройств в »

среде проэктирования VHDL

Выполнил: ст. 146гр.

Проверил:

Асс. Каф. САПР ВС

Рязанская государственная радиотехническая академия

Кафедра САПР ВС

Тема: Проектирование цифровых устройств с использованием пакета VHDL

Срок представления к защите: 25 апреля 2004г.

Задание выдано 5 марта 2004г.

Задание принято к исполнению __________ /студент гр.../

Задание выдал __________ /асс. каф. САПР ВС Н.В./

Содержание :

Задание.........................................................................................................................2

Содержание................................................................................................................. 3

2. Описание работы компонентов микросхемы.....................................................5 2.1. Схема логического элемента К155ЛА2................. ......................................5

2.2. Схема логического элемента К155ЛЕ1 ........................................................6

2.3. Схема логического элемента К155ЛА6 .......................................................8

2.4. Схема логического элемента К155ЛА3 ......................................................9

2.5. Схема логического элемента К155ТМ2......................................................10

2.6. Схема логического элемента К155РУ2.......................................................12

2.7. Схема логического элемента К155ТМ8......................................................14

2.8. Схема логического элемента К589АП26....................................................16

2.9. Схема логического элемента К559ИП2......................................................18

2.10. Схема логического элемента К599ИП1....................................................19

3. Моделирование схемы.........................................................................................20

Заключение..................................................................................................................26

Список литературы......................................................................................................27

Приложение .................................................................................................................28

C начала 70-х годов стала актуальной проблема создания стандартного средства документации схем и алгоритмов цифровой аппаратуры

(ЦА), одинаково пригодного как для восприятия человеком, так и для обработки в ЭВМ. Этим средством явился язык VHDL. Это один из немногих языков программирования, созданных в результате целенаправленной работы коллектива специалистов в теории алгоритмических языков. Новые версии языка закреплены в стандартах. Поэтому VHDL предоставляет пользователю широкие возможности для воплощения его идей в проектах дискретных систем любой сложности и на всех уровнях абстракции. Грамматика, стили языка, способы его реализации обеспечивают программирование с минимумом ошибок в результирующих проектах. Можно утверждать, что VHDL не устареет в течение десятилетий.

К основным достоинствам языка VHDL следует отнести следующие.

1. СТАНДАРТНОСТЬ. Лучше иметь плохой стандарт, чем никакого. Это подтверждает библейский опыт создания вавилонской башни, разноязычие строителей которой привело к печальному результату.

VHDL официально признан как стандарт для описания цифровой аппаратуры, который поддерживается военно-промышленным комплексом и радиоэлектронной промышленностью Западных стран. Это облегчает обмен документацией между отдельными группами разработчиков и эксплуатационников аппаратуры, различными системами автоматизации проектирования

(САПР).

2. МНОГОАСПЕКТНОСТЬ И МНОГОУРОВНЕВОСТЬ. Универсальное средство заменяет несколько специализированных. Язык VHDL пригоден для описания как алгоритмов функционирования, так и схем аппаратуры. Он покрывает широкий диапазон уровней структурной детализации ее описаний: от описаний архитектуры ЭВМ на уровне устройств типа процессор-память до описаний на уровне вентилей, от описаний алгоритмов ЭВМ на уровне команд до описаний на уровне межрегистровых передач и булевых функций. На высших уровнях абстракции VHDL можно рассматривать как средство спецификации требований к проекту, на низших - как спецификации на изготовление изделия.

3. ЧЕЛОВЕКО-МАШИННОСТЬ. Документация пишется один раз, а читается многократно. Создатели VHDL нашли довольно удачный компромисс между требованиями к языку, как к средству документирования, удобному для восприятия человеком, так и формальному средству, удобному для ввода и обработки описаний систем в ЭВМ. VHDL-описания аппаратуры пригодны для обработки такими компонентами САПР, как подсистемы моделирования, подсистемы синтеза и анализа контрольных тестов, временные анализаторы, кремниевые компиляторы, подсистемы конструкторского проектирования.

К155ЛА2 - логический элемент И-НЕ

К155ЛЕ1 - логический элемент ИЛИ-НЕ

К155ЛА6 - логический элемент И-НЕ

К155ЛА3 - логический элемент И-НЕ

К155ТМ2 - набор из D-триггеров

К155РУ2 - высокоскоростное ОЗУ с емкостью 64 бит

К155ТМ8 - набор из D-триггеров

К589АП26 - шинный формирователь с инверсией

К559ИП2 – логический элемент или

К599ИП1 – логический элемент И-НЕ

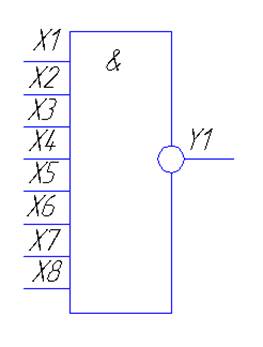

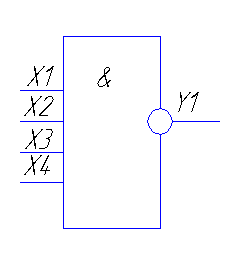

2.1 Схема К155ЛА2 (8И-НЕ)

Логический элемент серии ТТЛ К155ЛА2 выполняет логическую функцию 8И-НЕ

Схема электрическая принципиальная К155ЛА2

Логическая функция элемента:

![]() Y1=X1& X2& X3& X4& X5& X6& X7& X8

Y1=X1& X2& X3& X4& X5& X6& X7& X8

Таблица истинности элемента 8и-не

|

X1 |

X2 |

X3 |

X4 |

X5 |

X6 |

X7 |

X8 |

Y1 |

|

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

1 |

|

0 |

0 |

0 |

0 |

0 |

0 |

0 |

1 |

1 |

|

0 |

0 |

0 |

0 |

0 |

0 |

1 |

0 |

1 |

|

… |

… |

… |

… |

… |

… |

… |

… |

1 |

|

1 |

1 |

1 |

1 |

1 |

1 |

1 |

0 |

1 |

|

1 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

0 |

Рисунок:

Текст программы:

library IEEE;

use IEEE.std_logic_1164.all;

entity k155La2 is

port (

x1: inout STD_LOGIC;

x2: inout STD_LOGIC;

x3: inout STD_LOGIC;

x4: inout STD_LOGIC;

x5: inout STD_LOGIC;

x6: inout STD_LOGIC;

x7: inout STD_LOGIC;

x8: inout STD_LOGIC;

y1: out STD_LOGIC

);

end k155La2;

architecture k155La2 of k155La2 is

begin

Process (x1,x2,x3,x4,x5,x6,x7,x8) begin

y1<=not (x1 and x2 and x3 and x4 and x5 and x6 and x7 and x8) after 22 ns;

end process;

end k155La2;

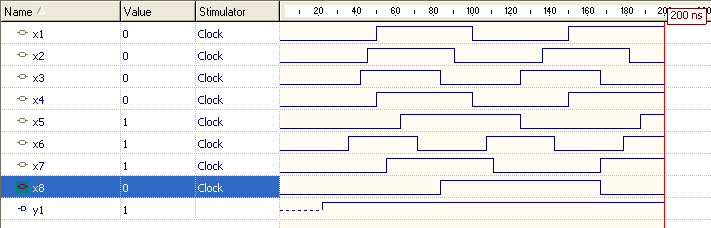

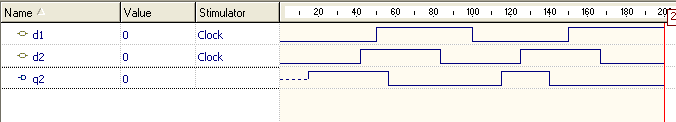

2.2 Схема К155ЛЕ1 (ИЛИ-НЕ)

Логический элемент 2ИЛИ-НЕ серии ТТЛ К155ЛЕ1 выполняет логическую функцию ИЛИ-НЕ.

Схема электрическая принципиальная К155ЛЕ1

Логическая функция элемента:

_________

Y1=(X1 or X2)

Таблица истинности элемента 8и-не:

|

X1 |

X2 |

Y1 |

|

0 |

0 |

1 |

|

0 |

1 |

0 |

|

1 |

0 |

0 |

|

1 |

1 |

0 |

Рисунок:

Текст программы:

library IEEE;

use IEEE.std_logic_1164.all;

entity K155Le1 is

port (

d1: inout STD_LOGIC;

d2: inout STD_LOGIC;

q2: out STD_LOGIC

);

end K155Le1;

architecture K155Le1 of K155Le1 is

begin

Process (d1,d2)

Begin

q2<=not (d1 or d2)after 15 ns;

End process;

end K155Le1;

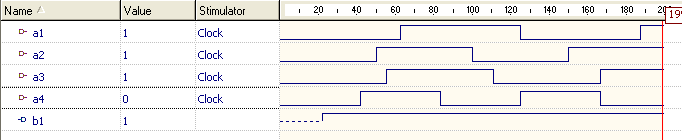

2.3 Схема логического элемента К155ЛА6 (4И-НЕ)

Логический элемент 4и-не серии ТТЛ К155ЛА6 выполняет логическую функцию 4И-НЕ.

![]() Рис. Схема электрическая принципиальная К155ЛА6

Рис. Схема электрическая принципиальная К155ЛА6

Логическая функция элемента: Y1=X1&X2&X3&X4

Таблица 4. Таблица истинности элемента 4И-НЕ

|

Х1 |

Х2 |

Х3 |

Х4 |

Y1 |

|

0 |

0 |

0 |

0 |

1 |

|

0 |

0 |

0 |

1 |

1 |

|

0 |

0 |

1 |

0 |

1 |

|

… |

… |

… |

… |

1 |

|

1 |

1 |

1 |

0 |

1 |

|

1 |

1 |

1 |

1 |

0 |

Рисунок:

Текст программы:

library IEEE;

use IEEE.std_logic_1164.all;

entity K155La6 is

port (

a1: in STD_LOGIC;

a2: in STD_LOGIC;

a3: in STD_LOGIC;

a4: in STD_LOGIC;

b1: out STD_LOGIC

);

end K155La6;

architecture K155La6 of K155La6 is

begin

Process (a1,a2,a3,a4)

Begin

b1<= not(a1 and a2 and a3 and a4)after 22 ns;

End process;

end K155La6;

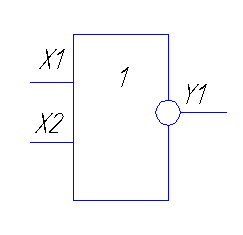

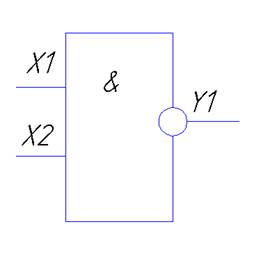

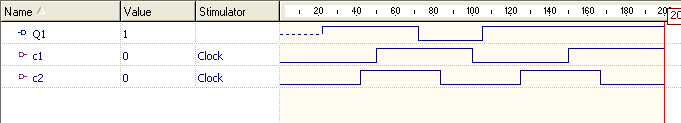

2.4 Схема логического элемента К155ЛА3 (2И-НЕ)

Логический элемент 2И-НЕ серии ТТЛ К155ЛА3 выполняет логическую функцию И-НЕ.

Рис. Схема электрическая принципиальная К155ЛА3

![]()

Логическая функция элемента: Y1=X1&X2.

Таблица . Таблица истинности элемента 2и-не.

|

Х1 |

Х2 |

Y1 |

|

0 |

0 |

1 |

|

0 |

1 |

1 |

|

1 |

0 |

1 |

|

1 |

1 |

0 |

Рисунок:

Текст программы:

library IEEE;

use IEEE.std_logic_1164.all;

entity K155La3 is

port (

c1: in STD_LOGIC;

c2: in STD_LOGIC;

Q1: out STD_LOGIC

);

end K155La3;

architecture K155La3 of K155La3 is

begin

process (c1,c2)

begin

Q1<=c1 nand c2 after 22 ns;

end process;

end K155La3;

ТМ2 представляет собой D-триггер, имеет 4 входа: С синхроимпульс

Уважаемый посетитель!

Чтобы распечатать файл, скачайте его (в формате Word).

Ссылка на скачивание - внизу страницы.