Необходимо, зная параметры обрабатываемых сигналов, выбрать интерфейс для обмена информацией с ПЭВМ и, руководствуясь им, формировать функциональную схему устройства.

Поскольку стоит задача обеспечить возможность обмена информацией с ЭВМ разных типов, то необходимо выбирать из наиболее распространенных типов интерфейсов. В настоящее время это следующие три интерфейса: RS-232C, Centronics, ISA [5].

Последовательный интерфейс RS-232C обладает следующими достоинствами: простота протокола обмена (побитный последовательный обмен), большая длина соединительных проводников (до 15 метров), возможность оформления устройства как внешнего отсоединяемого блока. Недостатки интерфейса — чрезвычайно низкая скорость обмена (до 115200 бод), необходимость разработки внешнего блока питания для устройства.

Параллельный интерфейс Centronics дает такие преимущества: существенно более высокая по сравнению RS-232C скорость обмена (порядка 150 Кб/сек за счет параллельного 8-битного обмена), возможность полнодуплексного обмена при использовании нескольких имеющихся линий управления. Недостатки — малая предельная длина соединительных проводников (до 1 метра), потребность во внешнем источнике питания для устройства. Кроме того, обычно разъем параллельного порта на ПК занят принтером.

Внутренняя шина ISA (Industrial Standard Architecture), являющаяся стандартной шиной большинства ПК, обеспечивает скорость передачи до 8 Мб/сек, возможность 8- и 16-битного обмена, напряжения питания четырех номиналов. К недостаткам интерфейса можно отнести жесткую привязанность к конкретному компьютеру.

Поскольку по техническому заданию верхняя частота сигнала

составляет 1 МГц, то скорость поступления входных данных составит, в

соответствии с теоремой Котельникова, не менее ![]() , то

есть скоростей интерфейсов RS-232C и Centronics

не хватит для передачи сигналов в реальном времени. Скорость передачи

шины ISA много выше скоростей других интерфейсов,

поэтому с целью обеспечения минимальной длительности интервала между

«затребованием» и «предоставлением» информации в качестве интерфейса обмена

информацией выбрана шина ISA. Кроме того, шина ISA обеспечивает упрощение разработки схемы по сравнению с

другими типами интерфейса за счет исключения необходимости разработки источника

питания.

, то

есть скоростей интерфейсов RS-232C и Centronics

не хватит для передачи сигналов в реальном времени. Скорость передачи

шины ISA много выше скоростей других интерфейсов,

поэтому с целью обеспечения минимальной длительности интервала между

«затребованием» и «предоставлением» информации в качестве интерфейса обмена

информацией выбрана шина ISA. Кроме того, шина ISA обеспечивает упрощение разработки схемы по сравнению с

другими типами интерфейса за счет исключения необходимости разработки источника

питания.

Дополнительным преимуществом этой шины является простота сопряжения устройства ввода с ПЭВМ, обусловленная общей нацеленностью архитектуры шины на работу с быстродействующими цифровыми внешними устройствами.

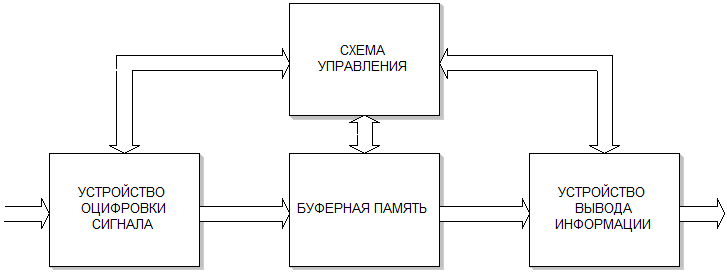

Разработка функциональной схемы будет вестись методом «сверху вниз», то есть с постепенным повышением детализации.

Ввод информации в ПК может осуществляться непосредственно с выхода схемы преобразования аналогового сигнала, либо в два этапа: на первом этапе информация сохраняется в буферной памяти, на втором — передается из буферной памяти в основную [8]. Первый способ технически проще реализуется, но у него есть ряд недостатков.

Во-первых, это занятость процессора на весь период ввода сигнала, который может быть довольно длительным. Эта занятость объясняется тем, что при вводе сигнала необходимы равные промежутки времени между взятием отсчетов, и в решении этого вопроса нельзя ориентироваться на частоту шины ISA, поскольку в разных реализациях частота синхросигналов на ней колеблется от 6 до 10 МГц. Вследствие этого потребуется программное формирование циклов задержки между обращениями.

Во-вторых, даже если решиться на описанный выше шаг, длительность собственно цикла обмена на шине может меняться от обращения к обращению из-за необходимости циклов регенерации основной памяти и работы других устройств на той же шине.

Наконец, в-третьих, минимальная длительность цикла обмена по шине ISA составляет порядка 1 мкс, то есть частота обращения процессора за очередной порцией информации не может превышать 1 МГц, что в данном проекте совершенно неприемлемо. Поэтому выберем схему двухэтапного обмена с использованием буферной памяти.

В свете всего сказанного наиболее общий вид структурной схемы представляется следующим:

Рис. 4.1. Обобщенная структурная схема

Уважаемый посетитель!

Чтобы распечатать файл, скачайте его (в формате Word).

Ссылка на скачивание - внизу страницы.