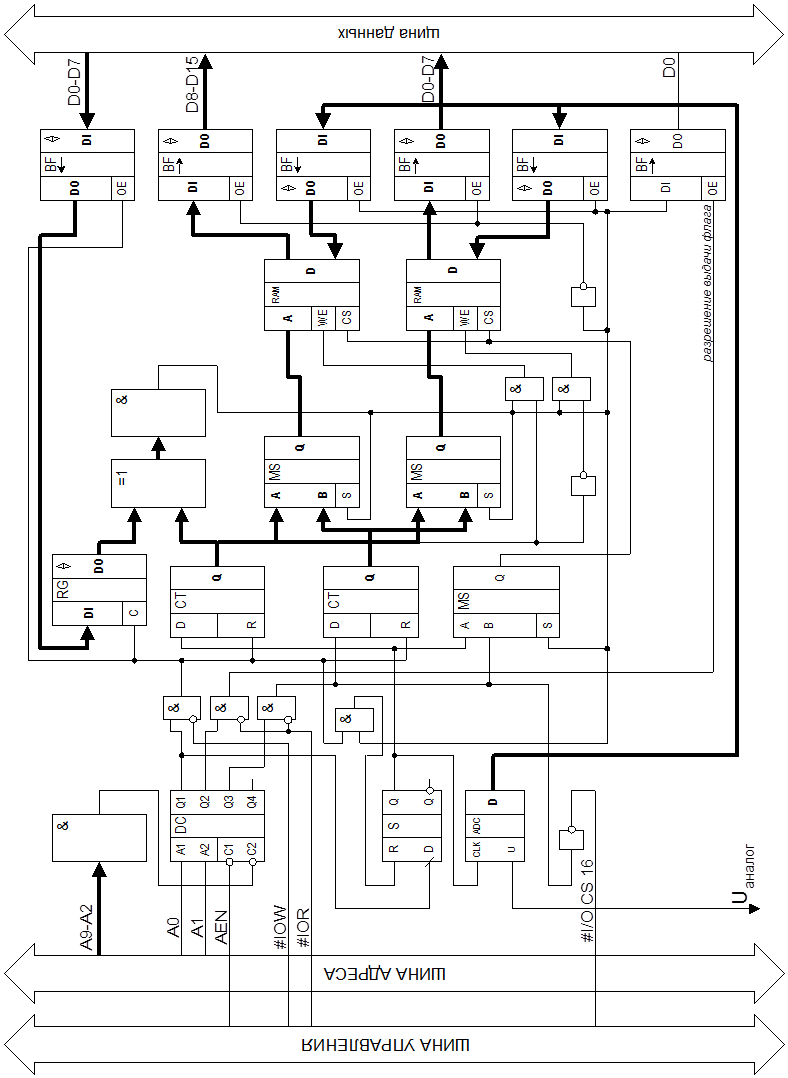

При передаче информации в основную память применяется другой принцип. Передача будет идти через третий порт. Поскольку за один цикл шины по ней можно передать максимум 16 бит, то есть за одно обращение всех данных не передать, и потребуется несколько обращений, то для увеличения счетчика адреса памяти будет использован не внутренний тактовый генератор, а сигнал обращения к этому порту. Это существенно упрощает схему формирования текущего адреса. Следить за числом полученных отсчетов и определять необходимое число обращений надо будет программным путем, на уровне драйвера устройства.

Потребуется полная дешифрация адреса. Для адресации ко

внешним устройствам на шине ISA обычно применяются 10

адресных линий из 16 [8]. Поскольку для работы схемы

потребуется 3 адреса, то из 10 адресных линий сигналы 8 будут для всех трех

случаев постоянными, и лишь сигналы 2 младших адресных разрядов будут меняться.

В таком случае полную дешифрацию адреса можно произвести на элементе 8И и

дешифраторе 2х4. В качестве отключающего дешифратор сигнала должен

использоваться сигнал AEN начала прямого обмена

с памятью, поскольку среди условий, накладываемых на ISA-платы

расширения, есть требование, чтобы при начале прямого доступа к памяти платы

отключались от шин адреса и данных. При управлении также должны учитываться

сигналы ![]() и

и ![]() .

.

Поскольку шина ISA поддерживает

16-битный режим передачи, то для пересылки данных в основную память будет

использован именно он, как более быстрый. Это позволит сократить время, в

течение которого невозможен очередной прием и оцифровка сигнала, но потребует

использования пары микросхем памяти вместо одной. Недостатком такого режима

будет передача лишнего байта в случае, если исходное число отсчетов было

нечетным. Это также необходимо корректировать программным путем. Для работы

шины в 16-битном режиме необходимо выставлять специальный сигнал ![]() , низкий уровень которого указывает

системе, что передача данных ведется 16-битными словами. Следовательно, нужна

схема формирования такого сигнала.

, низкий уровень которого указывает

системе, что передача данных ведется 16-битными словами. Следовательно, нужна

схема формирования такого сигнала.

Для работы требуется схема получения и хранения длины сигнала (количества отсчетов). Ее можно реализовать на регистре.

Также требуются схемы вычисления текущего количества отсчетов и сравнения текущего и заданного их количества, чтобы по достижении равенства закончить оцифровку и снять флаг занятости. Для счета подойдет двоичный счетчик, для операции сравнения — схема Исключающее ИЛИ в совокупности со схемами НЕ и И.

Для устройства оцифровки (АЦП) требуется схема управления, задающая тактовые сигналы и способная запустить АЦП по внешнему сигналу и остановить работу по достижении заданного количества отсчетов. Для этого будет использован мультивибратор.

Для формирования адреса при выводе информации нужен еще один счетчик. Необходима схема выбора задатчика адреса во избежание конфликтов между счетчиками. Эта схема выполняется на мультиплексорах.

Для развязки схемы и шины данных нужны буферные микросхемы — шинные формирователи.

Для формирования сигнала ![]() будет

использован сигнал с дешифратора адреса при обращении к третьему порту.

будет

использован сигнал с дешифратора адреса при обращении к третьему порту.

Для управления выдачей флага занятости используем шинный формирователь с тремя состояниями на выходе. В качестве флага занятости будет выдаваться сигнал совпадения/несовпадения числа требуемых и принятых отсчетов, а управляться буферная микросхема будет сигналом с дешифратора адреса, то есть информация будет выдаваться на шину данных только при обращении в заданный порт.

В качестве буферной памяти будут использованы микросхемы статического ОЗУ. Управление их работой будет вестись через мультиплексор и логические элементы сигналами с мультивибратора при получении отсчетов и с дешифратора при передаче отсчетов в основную память. Необходимо учесть, что при записи в микросхемы они будут чередоваться, а при чтении будут являться одним 16-битным блоком. Это можно обеспечить, если на этапе накопления отсчетов на вход разрешения записи микросхем памяти подавать значение младшего разряда первого счетчика — он даст необходимое чередование микросхем, — и использовать для адресации старшие 7 разрядов счетчика, а на этапе пересылки отсчетов пользоваться всеми 8 адресными линиями, подсоединив их ко второму счетчику.

Окончательно функциональная схема принимает следующий вид:

Рис. 4.3. Полная функциональная схема устройства

Уважаемый посетитель!

Чтобы распечатать файл, скачайте его (в формате Word).

Ссылка на скачивание - внизу страницы.