Содержание.

1. Введение……………………………………………………………………………………….

2. Анализ задачи и ее формализация

3. Разработка и обоснование общего алгоритма функционирования устройства

и его описание………………………………………………………………………………..

4. Выбор и обоснование аппаратной части устройства………………………………………

5. Разработка и отладка программы……………………………………………………………

6. Составление принципиальной (функциональной) схемы устройства и ее описание……

7. Оценка быстродействия устройства………………………………………………………...

8. Заключение……………………………………………………………………………………

9. Список использованных источников………………………………………………………..

10. Приложение…………………………………………………………………………………...

Введение.

Развитие микроэлектроники привело к широкому применению ее изделий в промышленном производстве, в устройствах и системах управления самыми разнообразными объектами и процессами. Использование микроэлектронных средств в изделиях приводит к повышению их технико-экономических показателей (стоимость, надежность, потребляемая мощность, габаритные размеры). В данном курсовом проекте будет разработано устройство управления синтезатором частоты телевизионного приемника МВ на микросхеме КР1051ХА2А, которое выполнено на микропроцессоре КР1816ВЕ51

Анализ задачи и ее формализация.

В данном курсовом проекте необходимо сделать программу управления синтезатором частоты для телевизионного приемника MB. Клавиатура выполнена из 12 клавиш при нажатии которых выводится звук и после выводятся данные на синтезатор частоты. При нажатии клавиши необходимо через прорт P3 выдать последовательный сигнал для унифицированной последовательной двупроводной шины I2C. Данную задачу можно решить, изменяя значение битов порта Р 3.0 сигнал SDA и Р 3.1 сигнал SCL. Сигнал SDA нужно передорвать в последовательности одной из форм команд шины I2C имеющий вид

СТАРТ-АДР-TV1-TV2-СТОП

Где СТАРТ-стартовое условие; АДР-адресный байт; TV1-первый байт програмирования коэффициента деления; TV2-второй байт програмирования коэффициента деления.

|

Разработка и обоснование общего алгоритма функционирования устройства и его описание.

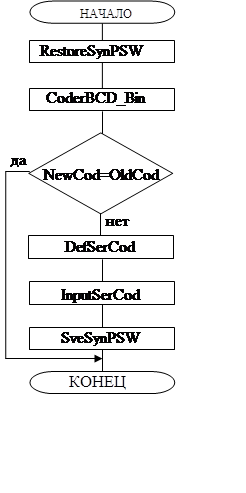

При старте в первом блоке RestoreSoundPSW, происходит восстановление PSW

для синтезатора. В следующем блоке происходит перевод BCD кода

номера канала в двоичный код, а потом сравнивается со старым значением канала и

если они равны то выход из программы в противном случае продолжение выполнения

программы. В блоке DefSesCod происходит преобразование

кода канала в последовательный код частоты канала для синтезатора. В блоке InputSerCod формируется полный выходной сигнал.

При старте в первом блоке RestoreSoundPSW, происходит восстановление PSW

для синтезатора. В следующем блоке происходит перевод BCD кода

номера канала в двоичный код, а потом сравнивается со старым значением канала и

если они равны то выход из программы в противном случае продолжение выполнения

программы. В блоке DefSesCod происходит преобразование

кода канала в последовательный код частоты канала для синтезатора. В блоке InputSerCod формируется полный выходной сигнал.

Выбор и обоснование аппаратной части устройства.

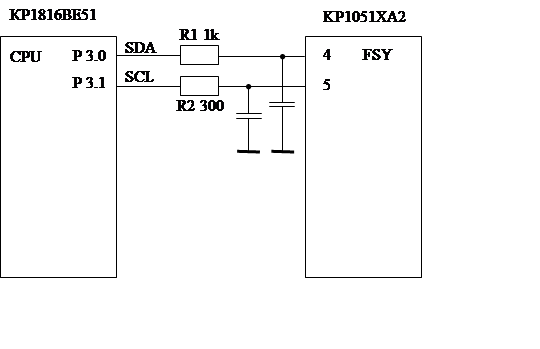

Вывод информации происходит через порт Р 3.0 (сигнал SDA) и Р 3.1 (сигнал SCL) . Для выполнения временных характеристик при необходимости подключается RC цепочки к выводам SDA и SCL.

|

Разработка и отладка программы.

В соответствии с алгоритмом и аппаратной частью устройства разработана программа (см. приложение), которая написана на языке «Ассемблер». Для удобства разбили программу на макросы, поэтому основная программа содержит только их имена. Рассмотрим макросы.

В макросе RestoreSynPSW происходит запись текущего PSW в регистр VarPSW и васстановление PSW для «синтезатора» (из регистра SynPSW). В макросе SaveSynPSW наоборот. В макросе RestoreSynPSW текущее PSW записывается в регистр VarPSW и восстрановление PSW для «синтезатора». Этот макрос используется при прерывании таймера Т1, для исключения потери PSW основной программы (потеря может произойти при прерывании таймера Т1 в момент выполнения данной программы). В SaveSynPSW наоборот. В макросе InitRegSyn происходи запись адреса с которого начинается область под стек, запись «банка 0» в SynPSW и установка SDA и SCL в высокое состояние. В макросе CoderBCD_Bin происходит перевод двухразрядного кода BCD в двоичный для чтения кода частоты канала. В макросе Test происходит проверка старого и нового канала. В макросе DefSerCod происходит определение последовательного кода частоты из таблици. В макросе StartBit происходит формирование стартового условия для передачи команды в синтезатор частоты. В макросе StopBit формирует STOP условие, тем самым конец команды. В макросе AddrBit происходит передача адресного бита. В макросе MakeSerCod происходит передача последовательного кода. В макросе InputSerCod происходит формирование полного выходного сигнала. Вышеперечисленные макросы в основной программе выполняются в соответствии с алгоритмом.

Отладка программы производилась в программе emu51.exe. Перед этим текст программы был оттранслирован и она была размещена в памяти следующим образом:

CODE: 100h

Data: 200h

Rsect: 30h

InitSeg: 0h

При такой трансляции BufKey0 является 34 регистром; BufKey1 является 35-м регистром; . Все вышеперечисленные регистры расположены в Dseg.

При установке 35 регистра в 1h и выполнении программы выяснили, что из таблици частот считался код 0Fh и 54h , что соответствует установке 10 канала. При выполнении первого цикла работы программы выяснили, что в порту Р3 сначало выставилось значение соответствующее стартовому условию потом побитно выстовилось адресный бит и последовательный код частоты 10 канала и потом условие конца команды(STOP). При повторном цикле работы программы она перепрыгнула на выход программы т.е не менялся код частоты канала. Исходя из вышеперечисленных фактов можно заключить что программа работает верно.

Составление принципиальной (функциональной) схемы устройства и ее описание.

В соответствии с алгоритмом, программой и выбором аппаратной части была составлена принципиальная схема устройства. Порт Р 3.0 через RC цепочку подключен к выводу 4 микросхемы КР1051ХА2, а Порт Р3.1 через RC цепочку подключен к выводу 5 микросхемы.

Оценка быстродействия устройства.

При самом неблагоприятном моменте выполняется n команд, что соответствует 246 машинным циклам, то есть k мкс.

Заключение.

В данном курсовом проекте была разработана программа, принципиальная схема устройства управления синтезатором частоты телевизионного приемника. Результаты отладки показали, что программа работает верно. В программе реализована защита от потери PSW при прерывании таймера Т1 при выполнении программы на любом шаге.

Список использованных источников.

1. Сташин В.В. Проектирование цифровых устройств на однокристальных микроконтроллерах.-М.: Энергоатомиздат, 1990.

2. Цифровые интегральные микросхемы: Справочник/ П.П. Мальцев и др.-М.: Радио и связь, 1994.

3. Интегральные схемы для бытовой радиоаппаратуры: Справочник/ Новаченко И.В. и др. М: Радио и Связь, 1995.

Уважаемый посетитель!

Чтобы распечатать файл, скачайте его (в формате Word).

Ссылка на скачивание - внизу страницы.