Схемы этих рисунков могут служить основой для разработки схем квазиоптимальных дискриминаторов, если под операцией суммирования понимать алгебраическое суммирование знакопеременных чисел, т. к. в данном случае коэффициенты bi-j могут быть и положительными, и отрицательными.

|

Результатом дискриминирования будет являться знакопеременное

|

,накапливаемое реверсивным счётчиком за время поступления n выборочных значений сигнала {Ji, i=[1,n]}.

Знак dj будет показывать направление смещения строба, а значение – величину смещения.

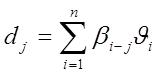

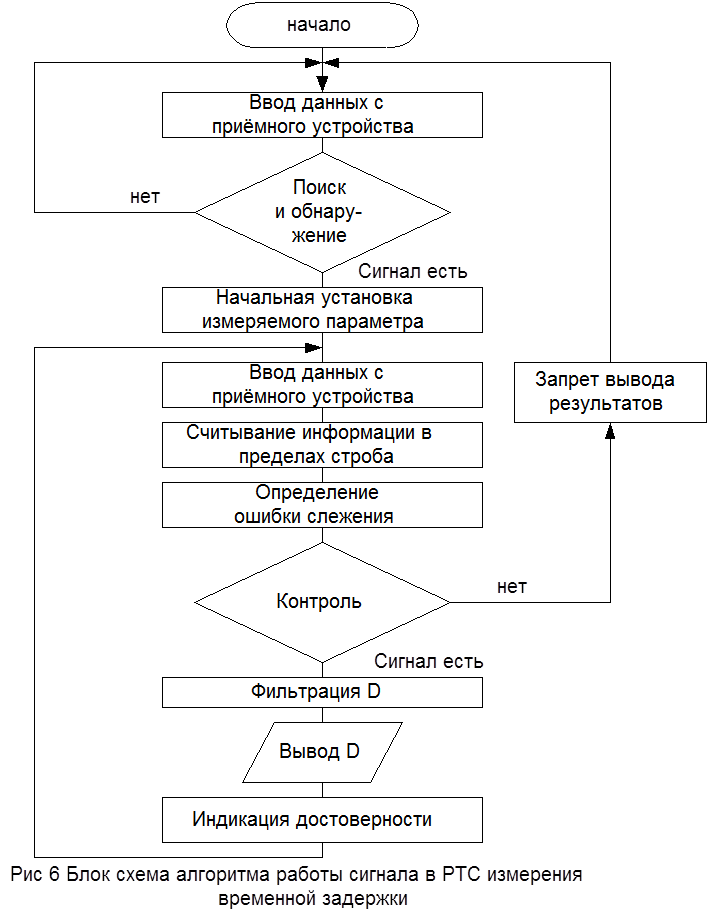

В режиме поиска достаточно определить дальность относительно грубо, а затем в процессе слежения измерять ёё с требуемой точностью. В этом режиме система должна выполнять следующие функции:

1) производить измерения временного интервала Dt (рис. 3.1, д) от начала строба до момента времени, соответствующего точке фиксации принятого сигнала с точностью, определяемой периодом тактовой последовательности.

2) вводить измеренные значения в МП

3) изменять состояние ячейки-накопителя

4) осуществлять фильтрацию приращений значений Dt

5) вычислять полное значение дальности (рис 3.1,б,д,е)

6) выводить полное значение дальности в преобразователь “код-время” для генерирования измерительного строба длительностью tстр.

D^ - оценка дальности на данном шаге, соответствующая временной задержке tс.

|

|

|

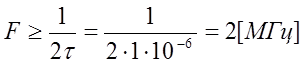

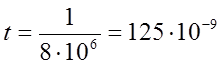

Т.е. не более 125 нс.

|

|

|

Вид структурной схемы зависит от типа выбранного нами микропроцессора. Выбирать процессор будем по следующим критериям:

ü требуемое быстродействие (частота дискретизации 8 МГц)

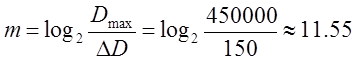

ü требуемая разрядность (>15)

Всем этим требованиям удовлетворяет микропроцессор ADSP-2172. Его основные параметры:

Ø Память программ (RAM), слов.................................................................2к

Ø Память программ (ROM), слов.................................................................8к

Ø Память данных (RAM), слов.....................................................................2к

Ø Максимальная тактовая частота, МГц...................................................16.67

Ø Длина цикла, нсек......................................................................................30

Ø Напряжение питания, В..............................................................................5

Ø Разрядность шины данных........................................................................24

Ø Разрядность шины адреса..........................................................................15

Ø Корпус...........................................................................PQFR128 или TQFR128

За один цикл процессор может:

· Генерировать адрес следующей программной инструкции.

· Загрузить из памяти следующую инструкцию.

· Произвести одну или 2 пересылки данных.

· Обновить один или 2 указателя на данные.

· Произвести вычисление.

Этот процессор будет основным элементом дискриминатора. Подключение внешней памяти не требуется. С учётом того, что данный МП не имеет встроенных портов ввода/вывода, потребуется некоторое усложнение схемы. Для обмена данными между процессором и внешними устройствами потребуется логическая схема селектора адреса и коммутатора сигналов. Для совместимости логических уровней сигналов процессора с внешними устройствами будем использовать преобразователи уровней сигналов (ПУ) (рис 5)

Работа схемы

Каждое внешнее устройство должно иметь свой адрес. Этот адрес должен находиться за пределами адресов встроенной памяти процессора. Если в процессе выполнения программы происходит обращение к одному из внешних устройств, то этот адрес в виде нулей и единиц (бинарный код) появится на шине адреса, к которой подключен селектор адреса. По результатам анализа адреса в селекторе коммутатор подключит нужное внешнее устройство к шине данных. Сигналы управления процессором включают в себя RESET, синхроимпульсы, входы и выходы флагов, и сигналы запроса прерывания. В схеме используется кварцевый резонатор, подсоединённый между входами CLKIN и XTAL. RESET останавливает выполнение инструкций и осуществляет аппаратный сброс. Сигнал RESET устанавливается при включении питания процессора для осуществления правильной инициализации. Хотя начальная загрузка может инициализироваться не только сигналом RESET, но и программно. Сигнал RD (низкого уровня) – чтение данных процессором из памяти. Сигнал WR (низкого уровня) – процесс записи в память. Если DMS (низкого уровня) есть, то на шину адреса поступает адрес памяти данных. Установка бита BFORCE в регистре управления процессором приводит к программной инициализации начальной загрузки. Программная начальная загрузка очищает контекст процессора и инициализирует некоторые регистры. Необходимо также учесть, что после приведения процессора в готовность к работе, незамедлительно должна быть выполнена проверочная программа, которая оценит правильность вычислений микропроцессора. Выходные данные – двоичный код по стандарту RS-232.

|

вычислительным устройством. Полностью программная реализация, соответствующая структурной схеме на рис 6 возможна только в том случае, если эти операции обмена, а также необходимые вычислительные операции могут быть выполнены в процессе поступления полезных сигналов с приёмного устройства, т. е. в реальном масштабе времени.

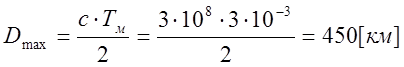

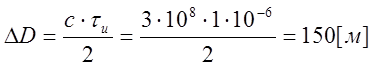

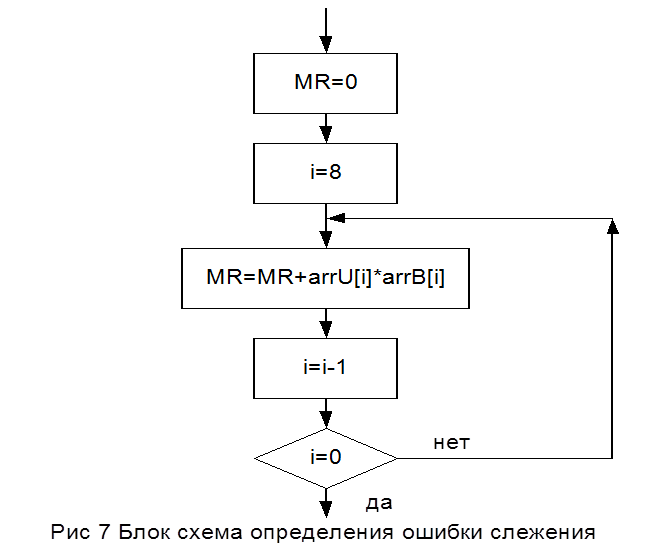

Основной операцией в блок схеме является определение ошибки слежения по дальности. До операции определения ошибки слежения 8 отсчётов входного сигнала, считая их начиная с момента tз через каждые 125 нс уже хранятся в памяти.

|

Для правильной и корректной работы микропроцессора, а также для увеличения скорости работы, необходимо программу написать на Ассемблере данного семейства цифровых сигнальных процессоров. Текст программы имеет вид:

L0=0;

L1=0;

l0=^arrU;

l1=^arrB;

CNTR=8;

M0=1;

MR=0;

DO lab Until CE

MX0=DM(lo,M0);

MY0=DM(i1,M0);

lab: MR=MR+MX0*MY0(SS);

DM(0x3A00)=MR;

Величина ошибки будет хранится в ячейке 0х3А00.

В данной курсовой работе была рассмотрена реализация импульсного радиодальномера на микропроцессоре с параметрами и характеристиками технического задания. Были рассчитаны все неизвестные параметры, составлены блок-схема алгоритма импульсной РЛС, и программа (её основная часть) режима слежения на языке Ассемблер.

Уважаемый посетитель!

Чтобы распечатать файл, скачайте его (в формате Word).

Ссылка на скачивание - внизу страницы.