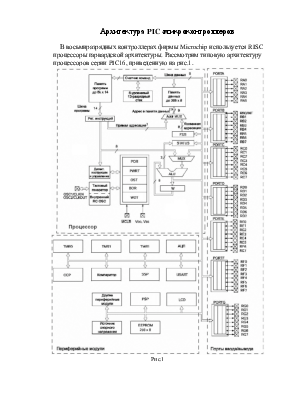

Архитектура PIC -микроконтроллеров

В восьмиразрядных контроллерах фирмы Microchip используется RISC процессоры гарвардской архитектуры. Рассмотрим типовую архитектуру процессоров серии PIC16, приведенную на рис.1.

Рис.1

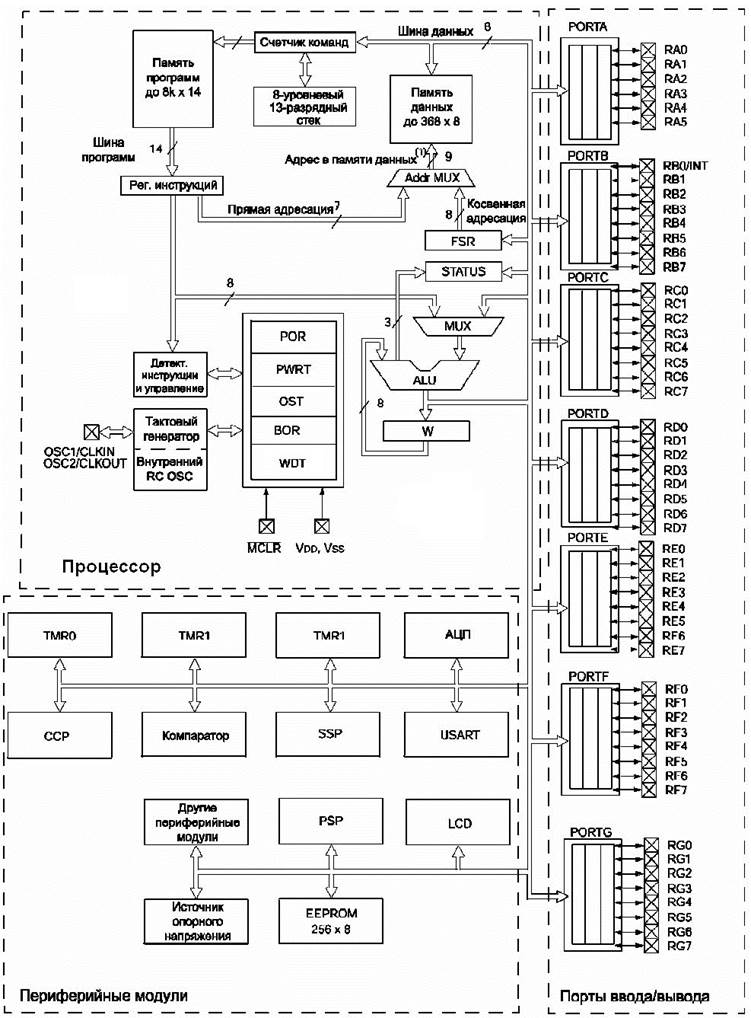

Шина данных – показана на рисунке двойной линией. Она подходит почти ко всем основным узлам микроконтроллера. По ней реализуется двусторонний обмен однобайтными данными между всеми узлами микроконтроллера.

ALU –арифметико-логическое устройство выполняет операции типовые арифметические и логические операции. Операнды могут приниматься по двум входам из шины данных, из команды, из регистра-аккумулятора и регистра состояний. Результат операции записывается в регистр-аккумулятор или через шину данных в любое устройство, подключенное к ней.

W – регистр-аккумулятор служит для оперативной записи промежуточных результатов операции. В MPLAB доступен как специальный регистр под именем WREG. В общем поле памяти данных адреса не имеет.

Память данных – реализована на статических триггерах в виде регистрового файла. Каждый регистр считается ячейкой памяти и имеет свой адрес, по которому он выбирается из общего файла. Адресация сквозная, т.е. адрес равен порядковому номеру регистра в памяти независимо от его назначения. Основная часть регистров относится к регистрам общего назначения, в которых любые данные в виде восьмиразрядных двоичных чисел могут записываться, храниться и считываться по мере необходимости. Часть поля адресов в начале памяти отведена для специальных регистров, которые используются для управления периферийным оборудованием и элементами микропроцессорного ядра.

С целью экономии числа разрядов в поле адресов машинных команд все адреса памяти разбиты на несколько групп. Каждая группа содержит адреса части смежных ячеек памяти. Группа называется банком. Число ячеек в банке кратно степени 2, поэтому полный адрес ячейки состоит из номера банка и адреса ячейки в банке. Чтобы обратиться к конкретной ячейке надо предварительно установить номер банка, записав его в соответствующие разряды специального регистра STATUS, и в исполняемой команде указать её адрес.

Счетчик команд – является обычным двоичным счетчиком, код которого увеличивается на единицу после выполнения очередной команды. Значение кода в счетчике используется как адрес для памяти программ, обеспечивая выбор следующей команды после выполнения текущей. Для выполнения команд переходов счетчик команд имеет развитые входы и выходы, по которым можно записывать произвольный код и читать содержимое счетчика. В программной среде микроконтроллера счетчик команд выглядит как специальный регистр с именем PCL и располагается в памяти данных по адресу 02.

Шина программ – расположена между памятью программ и регистром инструкций. Так как требуется соединение только двух узлов с передачей кодов только в одном направлении, эта шина вырождается просто в 14 соединительных проводников, и в явном виде отсутствует.

Память программ – запоминающее электрически перепрограммируемое устройство (Flesh – соответствует символу F в имени модификации микроконтроллера). В нём хранится управляющая программа микроконтроллера в виде 14-разрядных двоичных кодов команд. Применение увеличенной разрядности памяти программ (14 разрядов в восьмиразрядном микроконтроллере) позволяет в одной ячейке записать сразу всю команду.

Входом памяти является адрес команды, поступающий от счетчика команд. С выхода памяти программ очередная команда записывается в буферный регистр инструкций.

С целью экономии числа разрядов в поле адресов машинных команд все адреса программной памяти, как и памяти данных разбиты группы, называемые страницами. Счетчик команд PCL последовательно выбирает команды из заданной страницы. Чтобы перейти к команде на другой странице надо предварительно установить номер новой страницы, записав его в соответствующие разряды специального регистра PCLATCH, и в счетчик PCL записать адрес исполняемой команды в пределах страницы.

Регистр инструкций – хранит исполняемую команду до вызова следующей. Из этого регистра код команды поступает в детектор инструкций.

Если часть разрядов команды является адресом операнда, они поступают на адресный вход памяти данных для чтения самого операнда. Делается это через мультиплексор AddrMUX. Мультиплексором называется цифровое логическое устройство, имеющее два или более входов и один выход. По управляющим сигналам от синхронизатора и детектора команд мультиплексор выбирает нужный вход и передает его в нужный момент на свой единственный выход.

Уважаемый посетитель!

Чтобы распечатать файл, скачайте его (в формате Word).

Ссылка на скачивание - внизу страницы.