Если часть разрядов команды является константой (она называется литерой в переводах описаний микроконтроллеров Microchip) и является операндом, они поступают на вход арифметико-логического устройства (ALU) через мультиплексор MUX.

Тактовый генератор – вырабатывает первичные синхроимпульсы с постоянной частотой. Эти синхроимпульсы являются внутренним временем процессора, потому что от них срабатывают все узлы. Для этого тактовые импульсы поступают в синхронизатор (на структурной схеме показан прямоугольником с набором схем сброса POR PWRT и т.д.), где преобразуются в тактовые последовательности, которые поступают в детектор команд.

Детектор инструкций – определяет по коду команды, какие действия необходимо выполнить, и организует выполнение команды всеми узлами микроконтроллера. Для этого он вырабатывает управляющие коды и передает их на узлы микроконтроллера. Так как команды в PIC-контроллерах выполняются минимум за четыре такта, в детекторе инструкций ведется их счет и в каждом такте выдается свой набор управляющих кодов. Фактически детектор инструкций является микропрограммным устройством.

Стек – специальная быстродействующая память для хранения адресов команд возврата из подпрограмм и прерываний. Эта память строится по принципу “первым пришел - последним вышел”. Данные записываются все время в одну ячейку, из которой потом и читаются. Эта ячейка называется вершиной стека. При записи очередных данных в стек они помещаются в вершину, но перед этим ранее записанные данные перемещаются на один адрес вглубь стека. При чтении операция выполняется в обратном порядке. Практически перезаписывать все данные стека каждый раз очень неудобно и долго, поэтому для реализации стековой памяти перемещают не содержимое всех ячеек, а просто меняют адрес вершины стека, который хранят в специальном регистре, называемом указателем стека.

FSR - регистр косвенной адресации. В командах с косвенной адресацией производится обращение по адресу указанному в этом регистре, а не по адресу указанному в команде.

STATUS – регистр состояния процессора. В нем хранятся признаки переполнения и нулевого результата выполнения операции, номер банка памяти, к которому обращается процессор, и т.п. данные.

POR – схема вырабатывает импульс сброса после включения питания, который приводит МК в исходное состояние.

PWRT – таймер задержки разрешения тактовых импульсов после включения питания, пока это напряжение не стабилизируется.

OST - таймер задержки разрешения тактовых импульсов после включения пока не установится режим работы генератора.

BOR – схема сброса МК при снижении напряжения питания. Процессор удерживается в исходном состоянии, если напряжение питания меньше допустимого.

WDT – сторожевой таймер, состоит из встроенного RC-генератора и счетчика. Если происходит переполнение счетчика WDT, МК выполняет сброс и начинает выполнять программу с самого начала. Чтобы программа выполнялась правильно, необходимо предусмотреть достаточно частую очистку WDT командой CLRWDT. При сбое работы программы своевременная очистка не произойдет и процессор перезапустится заново.

Цикл выполнения команды

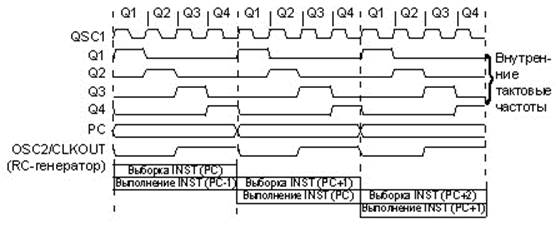

Цикл выполнения команды реализуется детектором инструкций и синхронизатором. Входная тактовая частота, поступающая от тактового генератора, в синхронизаторе делится на четыре, и из нее формируются четыре циклические не перекрывающиеся тактовые последовательности Q1, Q2, Q3 и Q4. Счетчик команд увеличивается в такте Q1, команда считывается из памяти программы и защелкивается в регистре команд в такте Q4. Команда декодируется и выполняется в течение последующего цикла в тактах Q1...Q4. Схема тактирования и выполнения команды изображена на рис.5.2.

Рис. 2. Схема тактирования и выполнения команды.

Цикл выполнения команды состоит из четырех тактов: Q1...Q4. Выборка команды и ее выполнение совмещены по времени таким образом, что выборка команды занимает один цикл, а выполнение – следующий цикл.

Цикл выборки начинается с увеличения счетчика команд в такте Q1. В цикле выполнения команды выбранная команда записывается в регистр команд в такте Q1. В течение тактов Q2, Q3 и Q4 происходит декодирование и выполнение команды. Одновременно с выборкой следующей команды выполняется текущая команда. При этом в такте Q2 считывается память данных (чтение операнда), а запись происходит в такте Q4. Эффективное время выполнения команды составляет один цикл.

Если команда изменяет счетчик команд (например, команда GOTO), то для ее выполнения потребуется два цикла, как показано на рис.3.

Рис. 3. Выборка команд.

Уважаемый посетитель!

Чтобы распечатать файл, скачайте его (в формате Word).

Ссылка на скачивание - внизу страницы.