Карта памяти процессора определяет одинаковый диапазон изменения адресов для PM и DM: от 0х0000 до 0х3FFF. В зависимости от настройки режима использования памяти указанный диапазон изменения адресов распределяется между внутренней и внешней памятью. Если внешний вывод MMAP процессора соединён с землёй и внутренние регистры выбора внутренней или внешней памяти (PMOVLAY и DMOVLAY) после сброса или перезапуска остаются обнулёнными, то используется внутренняя память PM и DM. Весь диапазон изменения адресов 0х0000 - 0х3FFF относится к внутренней памяти PM или DM.

Последовательные порты SPORT0 и SPORT1 обеспечивают синхронный обмен, поддерживают несколько стандартных протоколов обмена данными и могут обеспечить прямое соединение процессоров в вычислительной системе, состоящей из нескольких процессоров. Описание выводов последовательных портов приведено в таблице 1.

Последовательный порт принимает последовательно передаваемые данные с вывода DR и последовательно передаёт данные через вывод DT. Он может работать в дуплексном режиме, то есть одновременно принимать и передавать данные. Принимаемые (передаваемые) последовательные биты данных синхронны с тактовыми синхроимпульсами генератора SCLK передатчика. Для синхронизации потока последовательных бит по кадрам могут быть использованы сигналы RFS и TFS.

Основные свойства последовательных портов

· Двунаправленность. Принимающая и передающие части независимы друг от друга.

· Двойная буферизация. Наличие входных и выходных буферных регистров данных. Двойная буферизация сокращает время управления последовательным портом.

· Порт может использовать внешние тактовые синхроимпульсы или генерировать свои собственные в широком диапазоне частот.

· Порт поддерживает длину слова последовательно передаваемых данных от 3 до 16 бит.

· Принимающая или передающая часть последовательного порта может функционировать с использованием сигналов кадровой синхронизации для каждого слова данных или без них.

· Компандирование. Порт может выполнять аппаратное компандирование – преобразование исходного цифрового сигнала в сжатую цифровую форму и обратно согласно рекомендациям Международного консультативного комитета по телеграфии и телефонии (МККТТ).

· Автобуферизация. Используя генераторы адреса данных, последовательный порт может автоматически принимать и/или передавать целый циклический буфер данных с затратами в один цикл на слово данных. Передачи между последовательным портом и циклическим буфером не требуют дополнительного программирования.

· Прерывания. Приёмник или передатчик последовательного порта генерирует прерывание по завершении передачи слова данных или по завершении передачи целого буфера при использовании автобуферизации.

· Многоканальность. SPORT0 может мультиплексировать последовательные данные при приёме или передаче на 24 или 32 канала путём разделения цифрового потока во времени.

SPORT1 может быть сконфигурирован для приёма сигналов прерываний IRQ0, IRQ1 и передачи флагов FO и FI.

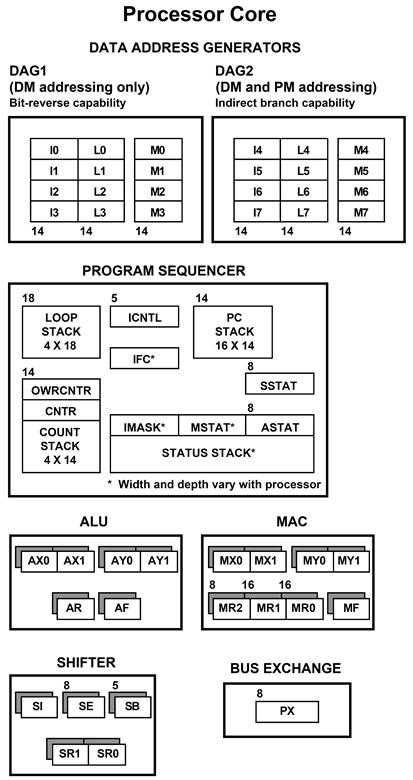

При программировании типовых алгоритмов ЦОС используется программная (регистровая) модель процессора. На рис. 3 приведена регистровая модель ядра (Processor Core) процессора ADSP-2181, одинаковая для процессоров семейства ADSP-21хх, которая более детально, на уровне программно-доступных регистров раскрывает структуру ядра, представленную на рис. 2. Данная модель используется при разработке программ в лабораторных работах 1, 2, 3.

1.3. Регистровая модель арифметико-логического

устройства, АЛУ(ALU)

АЛУ обеспечивает выполнение стандартного набора арифметических и логических операций: сложение, вычитание, изменение знака, инкремент, декремент, нахождение модуля числа, деление, логическое И (AND), ИЛИ (OR), исключающее ИЛИ (XOR), НЕ (NOT).

Разрешённые операнды-источники данных по входу Х ALU:

АХ0, АХ1 – входные регистры;

AR – регистр результатов;

MR0, MR1, MR2 – регистры результатов MAC;

SR0, SR1 – регистры результатов устройства сдвига.

Разрешённые операнды-источники данных по входу Х ALU:

АY0, АY1 – входные регистры;

AF – регистр обратной связи.

|

|

Рис. 2 |

Рис. 3

Разрешённые операнды-приёмники данных с выхода ALU:

AR – регистр результатов;

AF – регистр обратной связи.

Признаки результата, получаемого с выхода АЛУ, хранятся в арифметическом регистре состояний ASTAT.

Биты-признаки, входящие в состав регистра состояний

ASTAT:

AZ – признак нулевого результата (AZ=1);

AN – знаковый бит результата;

AV – признак переполнения разрядной сетки (AV=1);

AC – перенос из старшего разряда;

AS – знаковый бит операнда по входу Х;

AQ – знаковый бит частного при делении.

1.4. Регистровая модель умножителя-накопителя (МАС)

МАС выполняет умножение, умножение и сложение с накопленной суммой, умножение и вычитание из накопленной разности, выполняет функции насыщения и сброса в ноль.

Возможно любое сочетание знаковых (S) и беззнаковых (U) перемножаемых операндов: (SS), (US), (SU), (UU).

Разрешёнными операндами- источниками данных для MAC по входу Х могут быть:

МХ0, МХ1 – входные регистры;

AR – регистр результатов ALU;

MR0, MR1, MR2 – регистры результатов;

SR0, SR1 – регистры результатов устройства сдвига.

Разрешёнными операндами- источниками данных для MAC по входу Y могут быть:

MY0, MY1 – входные регистры MAC;

MF – регистр обратной связи.

Разрешённые операнды-приёмники данных с выхода MAC:

MR (MR2, MR1, MR0) – регистр результатов;

MF – регистр обратной связи.

Признаки результата, получаемого с выхода МАС, хранятся в арифметическом регистре состояний ASTAT:

Уважаемый посетитель!

Чтобы распечатать файл, скачайте его (в формате Word).

Ссылка на скачивание - внизу страницы.