Общая характеристика и функциональный состав микроконтроллера АТМеgа 128

АТМеgа 128 – 8-разрядная однокристальная МикроЭВМ, выполненная на базе AVR RISC – архитектуры, с электрически программируемой флэш-памятью программ.

Общие характеристики:

Разрядность ЦПУ (АЛУ и регистров процессора) – 8р;

Количество регистров процессора – 32;

Максимальное быстродействие – до 16 млн. операций/сек;

Объем (износостойкость) флэш-памяти программ – 128 Кбайт (64К*16) (10 000 циклов);

Объем (износостойкость) встроенного ПЗУ – 4К (100 000 циклов);

Объем встроенного ОЗУ – 4К;

Тактовая частота – 0 .. 16 МГц.

Состав периферийных устройств:

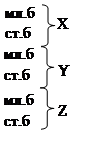

Параллельных портов ввода/вывода: 8 разрядных – 6 шт, 5 разрядных – 1 шт;

Последовательных портов (USART) – 2 шт;

Каналов 10 разрядного АЦП – 8 шт;

8-разр. таймер счетчиков – 2 шт;

16-разр. таймер счетчиков – 2 шт;

Сторожевой таймер – 1 шт;

Счетчик реального времени (RTC) – 1шт.

Интерфейсы:

SPI (внутрисистемное программирование);

JTAG (доступ к встроенной системе отладки и внутрисистемное программирование);

TWI (двухпроводный последовательный интерфейс).

Функциональный состав микроконтроллера АТМеgа 128

Архитектура микроконтроллера

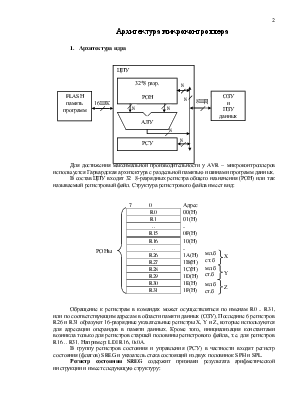

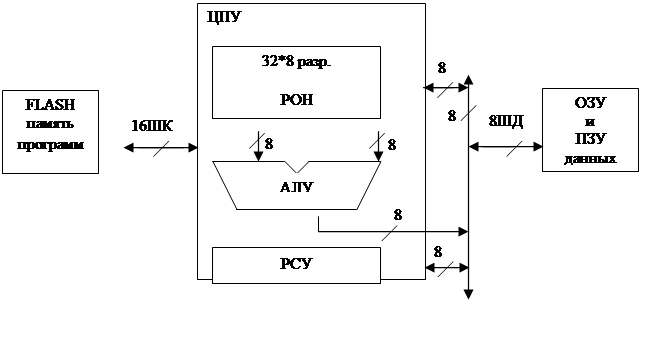

1. Архитектура ядра

|

Для достижения максимальной производительности у AVR – микроконтроллеров используется Гарвардская архитектура с раздельной памятью и шинами программ данных.

В состав ЦПУ входят 32 8-разрядных регистра общего назначения (РОН) или так называемый регистровый файл. Структура регистрового файла имеет вид:

|

7 0 |

Адрес |

|

R0 |

00(Н) |

|

R1 |

01(Н) |

|

.. |

.. |

|

R15 |

0F(Н) |

|

R16 |

10(Н) |

|

.. |

.. |

|

R26 |

1A(Н) |

|

R27 |

1B(Н) |

|

R28 |

1C(Н) |

|

R29 |

1D(Н) |

|

R30 |

1E(Н) |

|

R31 |

1F(Н) |

|

|||||

|

|||||

Обращение к регистрам в командах может осуществляться по именам R0 .. R31, или по соответствующим адресам в области памяти данных (ОЗУ). Последние 6 регистров R26 и R31 образуют 16-разрядные указательные регистры X, Y и Z, которые используются для адресации операндов в памяти данных. Кроме того, инициализация константами возникла только для регистров старшей половины регистрового файла, т.е. для регистров R16 .. R31. Например: LDI R16, 0x0A.

В группу регистров состояния и управления (РСУ) в частности входят регистр состояния (флагов) SREG и указатель стека состоящий из двух половинок SPH и SPL.

Регистр состояния SREG содержит признаки результата арифметической инструкции и имеет следующую структуру:

|

Адрес |

7 |

6 |

5 |

4 |

3 |

2 |

1 |

0 |

|

|

3F(5F) |

I |

T |

H |

S |

V |

N |

Z |

C |

SREG |

|

I/O (RAM) |

I – общее разрешение прерываний. Активизирует работу системы прерываний. Разрешение отдельных прерываний осуществляется в соответствующих управляющих регистрах. Если бит I=0, то ни одно из прерываний не будет активным, независимо от их индивидуальной конфигурации. Бит I сбрасывается в 0 аппаратно после генерации запроса на прерывание, а после выполнения инструкции возврата из прерывания RET I снова устанавливается в 1. Бит I может также сбрасываться и устанавливаться при помощи команд CLI и SEI, соответственно.

T – хранение копируемого бита.

H - флаг полупереноса.

S – бит знака (S=N xor V).

V – флаг переполнения двоичного дополнения.

N – отрицательный результат.

Z – флаг нулевого результата.

C – флаг переноса.

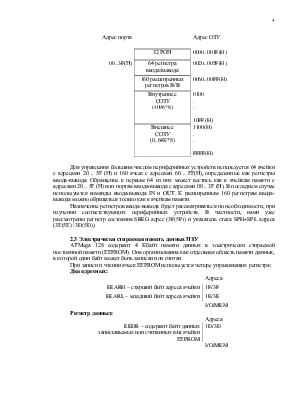

Указатель стека (SPH+SPL)

Стек обычно используется для хранения содержимого РОН и адресов возврата при уходе на прерывание или подпрограмму. Регистр указателя стека указывает на вершину стека. Стек растет в сторону меньших адресов и располагается в ОЗУ. Значение указателя стека должно изменяться в диапазоне адресации внутреннего ОЗУ, т.е. от 10FF(Н) до 0100(Н). Указатель стека уменьшается на 1 при выполнении команды PUSH и уменьшается на 2 при вызове подпрограммы или прерывания (т.к. адрес возврата 16-разрядный). Указатель стека увеличивается на 1 при выполнении команды POР и увеличивается на 2 при выполнении команд RET и RETI.

Указатель стека реализован как два 8-разрядных регистра в области ввода и вывода, и имеет вид:

Уважаемый посетитель!

Чтобы распечатать файл, скачайте его (в формате Word).

Ссылка на скачивание - внизу страницы.