Цель работы: Изучить порядок работы со встроенным аналого-цифровым преобразователем микроконтроллера ATmega 128.

1. Теоретические сведения

В состав ATmega 128 входит 8-канальный, 10-разрядный встроенный АЦП.

Работой АЦП управляют два регистра: регистр состояния и управления ADCSRA и регистр управления мультиплексором ADMUX

Результат преобразования может быть считан из регистров данных АЦП ADCH и ADCL (старший и младший байты соответственно).

1.1. Регистр состояния и управления

7 0

|

ADEN |

ADSC |

ADFR |

ADIF |

ADIE |

ADPS2 |

ADPS1 |

ADPS0 |

ADCSRA |

ADEN – разрешение работы АЦП. Если ADEN=1 – работа АЦП разрешена, если ADEN=0 – АЦП выключен.

ADFR – режим работы АЦП. Если он установлен в 1, АЦП работает в режиме непрерывного преобразования. В этом режиме запуск каждого следующего преобразования осуществляется автоматически после окончания текущего. Если же ADFR=0, АЦП работает в режиме одиночного преобразования и запуск каждого преобразования осуществляется записью 1 в бит ADSC.

ADSC – запуск преобразования. Запуск каждого преобразования в режиме одиночного преобразования, а также запуск первого преобразования в режиме непрерывного преобразования осуществляется установкой в 1 разряда ADSC. По завершении преобразования бит ADSC аппаратно сбрасывается в 0.

ADIF – завершение преобразования. Устанавливается в 1 по завершении преобразования и генерируется запрос на прерывание по адресу 002А(H). Сбрасывается аппаратно при запуске подпрограммы обработки прерывания от АЦП, или программно, записью в него логической 1.

Единица в бите ADIF означает, что результат преобразования находится в регистрах данных АЦП ADCH и ADCL.

ADIE – разрешение прерывания от АЦП. Разрешение прерывания осуществляется установкой в 1 разряда ADIE регистра ADCSRA при установленном флаге I регистра SREG.

ADPS2 .. ADPS0 – длительность преобразования. Для формирования тактовой частоты АЦП в нем имеется отдельный предделитель. Коэффициент деления определяется разрядами ADPS2 .. ADPS0:

|

ADPS2 |

ADPS1 |

ADPS0 |

Коэффициент деления |

|

0 |

0 |

0 |

без деления |

|

0 |

0 |

1 |

2 |

|

0 |

1 |

0 |

4 |

|

0 |

1 |

1 |

8 |

|

1 |

0 |

0 |

16 |

|

1 |

0 |

1 |

32 |

|

1 |

1 |

0 |

64 |

|

1 |

1 |

1 |

128 |

Десятиразрядная точность преобразования достигается, если тактовая частота АЦП находиться в диапазоне 50..200 кГц. На вход делителя поступает тактовая частота процессора.

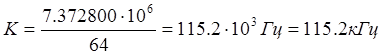

Пример: Выбрать коэффициент предделителя, если тактовая частота процессора 7,372800 МГц

То есть биты ADPS2 .. ADPS1 устанавливаем равными единице, а бит ADPS0 равным нулю.

1.2. Регистр управления мультиплексором

|

REFS1 |

REFS0 |

ADLAR |

MUX4 |

MUX3 |

MUX2 |

MUX1 |

MUX0 |

ADMUX |

REFS1 .. REFS0 – выбор источника опорного напряжения.

|

REFS1 |

REFS0 |

ИОН |

|

0 |

0 |

Внешний ИОН, подключенный к выводу AREF |

|

0 |

1 |

Напряжение питания АЦП AVcc |

|

1 |

1 |

Внутренний ИОН напряжением 2,56 В |

Замечание:

Уважаемый посетитель!

Чтобы распечатать файл, скачайте его (в формате Word).

Ссылка на скачивание - внизу страницы.