БАЛТИЙСКИЙ ГОСУДАРСТВЕННЫЙ ТЕХНИЧЕСКИЙ УНИВЕРСИТЕТ "ВОЕНМЕХ"

им. Д. Ф. УСТИНОВА

Кафедра И4

КУРСОВОЙ ПРОЕКТ

по учебной дисциплине « Цифровые устройства »

![]() на тему « Проектирование

четырехразрядного преобразователя кода »

на тему « Проектирование

четырехразрядного преобразователя кода »

![]() студента

Попикова

Михаила

студента

Попикова

Михаила

Группа И432

ПРЕПОДАВАТЕЛЬ

Астанин Л.Ю. / __________ /___________

Фамилия И.О. Подпись " __"_____________ 2006 г.

Санкт-Петербург 2006г.

Содержание

стр.

Техническое задание.................................................................................................................................................... ..3

Пояснительная записка

1.Анализ технического задания…………………………………………………….4

2.Составление логических уравнений устройства и их минимизация.................................................................................................................................................... ..4

3.Обоснование выбора элементной базы.................................................................................................................................................... ..6

4. Разработка принципиальной схемы синтезируемого устройства………..6

5. Расчёт технических показателей устройства………………………………6

6. Моделирование работы устройства, анализ правильности функционирования и состязаний в схеме........................................................................................................... .7

7. Разработка конструкции печатной платы………………………………….7

8. Оценка степени выполнения задания........................................................................................................... .7

ТЕХНИЧЕСКОЕ ЗАДАНИЕ

Тема проекта: «Проектирование четырехразрядного преобразователя кода».

Исходные данные

Спроектировать преобразователь простого 4-х разрядного кода букв десятичного алфавита в код по индивидуальному заданию с формированием бита паритета.

Код на выходе устройства: 5 11 4 8 3 7 12 15 0 6.

Бит паритета: Нечетный.

Требования:

-

напряжение питания 5В![]() 5%;

5%;

- потребляемая мощность: не более 250 мВт;

- время формирования выходного сигнала не более 25 нс;

- время наработки на отказ не менее 85000 час.

Условия эксплуатации:

- диапазон рабочих температур от минус 30°С до плюс 40°С;

- перегрузки до 5g;

- одиночные удары с ускорением не более 10g длительностью 0,1-1 мкс;

- вибрация с частотой 10 — 500 Гц и ускорением не более 10g.

Срок эксплуатации 15 лет, наработка за время эксплуатации до 85 тыс. часов.

Содержание пояснительной записки:

1. Анализ технического задания.

2. Составление логических уравнений устройства и их минимизация.

3. Обоснование выбора элементной базы.

4. Разработка принципиальной схемы синтезируемого устройства.

5. Расчет технических показателей устройства.

6. Моделирование работы устройства, анализ правильности функционирования и состязаний в схеме.

7. Разработка конструкции печатной платы.

8. Оценка степени выполнения задания.

Проектная документация:

1. Пояснительная записка.

2. Принципиальная схема устройства.

3. Сборочный чертеж печатной платы.

4. Спецификация.

Пояснительная записка

1. Анализ технического задания

Составим таблицу истинности для входного и выходного кода

|

Буква десят. алфавита |

Входной код |

Выходной код |

Бит паритета |

|||||||

|

N |

X3 |

X2 |

X1 |

X0 |

Y3 |

Y2 |

Y1 |

Y0 |

P |

|

|

0 |

0 |

0 |

0 |

0 |

0 |

1 |

0 |

1 |

0 |

|

|

1 |

0 |

0 |

0 |

1 |

1 |

0 |

1 |

1 |

1 |

|

|

2 |

0 |

0 |

1 |

0 |

0 |

1 |

0 |

0 |

1 |

|

|

3 |

0 |

0 |

1 |

1 |

1 |

0 |

0 |

0 |

1 |

|

|

4 |

0 |

1 |

0 |

0 |

0 |

0 |

1 |

1 |

0 |

|

|

5 |

0 |

1 |

0 |

1 |

0 |

1 |

1 |

1 |

1 |

|

|

6 |

0 |

1 |

1 |

0 |

1 |

1 |

0 |

0 |

0 |

|

|

7 |

0 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

0 |

|

|

8 |

1 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

|

|

9 |

1 |

0 |

0 |

1 |

0 |

1 |

1 |

0 |

0 |

|

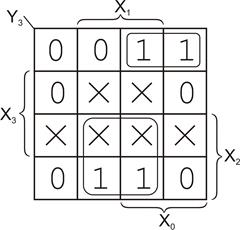

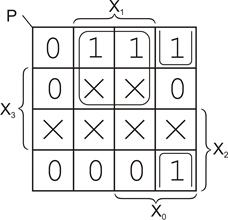

2. Составление логических уравнений устройства и их минимизация

![]()

![]() Минимизированное логическое уравнение с переходом от элементов

ИЛИ-НЕ к элементам И-НЕ по закону де Моргана:

Минимизированное логическое уравнение с переходом от элементов

ИЛИ-НЕ к элементам И-НЕ по закону де Моргана:

![]() .

.

|

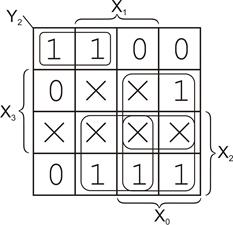

![]() Минимизированное логическое уравнение с переходом от элементов

ИЛИ-НЕ к элементам И-НЕ по закону де Моргана:

Минимизированное логическое уравнение с переходом от элементов

ИЛИ-НЕ к элементам И-НЕ по закону де Моргана:

![]() .

.

|

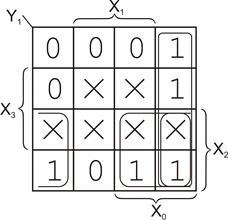

![]()

![]() Минимизированное логическое уравнение с переходом от элементов

ИЛИ-НЕ к элементам И-НЕ по закону де Моргана:

Минимизированное логическое уравнение с переходом от элементов

ИЛИ-НЕ к элементам И-НЕ по закону де Моргана:

![]() .

.

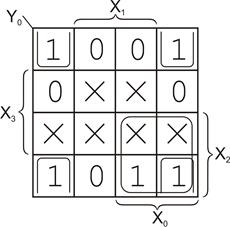

![]()

![]() Минимизированное логическое уравнение с переходом от элементов

ИЛИ-НЕ к элементам И-НЕ по закону де Моргана:

Минимизированное логическое уравнение с переходом от элементов

ИЛИ-НЕ к элементам И-НЕ по закону де Моргана:

![]() .

.

![]()

![]() Минимизированное логическое уравнение с переходом от элементов

ИЛИ-НЕ к элементам И-НЕ по закону де Моргана:

Минимизированное логическое уравнение с переходом от элементов

ИЛИ-НЕ к элементам И-НЕ по закону де Моргана:

![]() .

.

3. Обоснование выбора элементной базы

В качестве элементной базы выбираем серию КР1533 - ТТЛШ маломощные быстродействующие усовершенствованные интегральные микросхемы, т. к. их динамические параметры, допустимые значения внешних воздействующих факторов и надёжность соответствуют требованиям технического задания:

Pпот = 1 мВт; tзд. тип. = 4 нс; tзд. макс. = 8 нс; Эпот = 4 пДж; напряжение питания 5В±5%

Синусоидальная вибрация: диапазон частот 1 - 2000 Гц, амплитуда ускорения 200 м/с2

Механический удар одиночного действия:

пиковое ударное ускорение 1500 м/с2; длительность действия ударного ускорения 0.1 - 2 мс

Механический удар многократного действия:

пиковое ударное ускорение 1500 м/с2; длительность действия ударного ускорения 1 - 5 мс.

Линейное ускорение 5000 м/с2

Пониженная температура среды: рабочая -100С; предельная -600С.

Повышенная температура среды: рабочая 700С; предельная 850С.

Изменения температуры среды -650С - 850С.

4. Разработка принципиальной схемы синтезируемого устройства

Принципиальная схема синтезируемого устройства разработана на основе минимизированных логических уравнений и выбранной серии микросхем. Схема выполнена в программе КОМПАС V7.0 и представлена на чертеже 1 (Обозначение БГТУ.036.010.001Э3).

5. Расчёт технических показателей устройства

- Напряжение питания 5В ±5%

-

Потребляемая утройством мощность расчитывается по формуле ![]() , где

, где ![]() -

мощность, потребляемая одним логическим элементом (см. п.3),

-

мощность, потребляемая одним логическим элементом (см. п.3), ![]() - количество логических элементов. Итак,

- количество логических элементов. Итак, ![]() мВт.

мВт.

-

Время формирования выходного сигнала ![]() , где

, где ![]() - максимальное время задержки для одного

логического элемента,

- максимальное время задержки для одного

логического элемента, ![]() мкс для серии КР1533 (см. п.3), а

мкс для серии КР1533 (см. п.3), а

![]() - максимальное число последовательно

включенных логических элементов, для данной схемы (см. чертеж 1)

- максимальное число последовательно

включенных логических элементов, для данной схемы (см. чертеж 1) ![]() .Время формирования выходного сигнала

.Время формирования выходного сигнала ![]() нс.

нс.

-

Время наработки на отказ  , где

, где ![]() - количество используемых в схеме

логических элементов (для данной схемы

- количество используемых в схеме

логических элементов (для данной схемы ![]() , см.

чертеж 1);

, см.

чертеж 1); ![]() - количество отказов одного логического

элемента в час (для схем средней степени интеграции

- количество отказов одного логического

элемента в час (для схем средней степени интеграции ![]() отказов

в час). Время наработки

отказов

в час). Время наработки  часов.

часов.

- Диапазон рабочих температур от -100С до +700С

- Перегрузки до 500g

- Одиночные удары одиночного действия с ускорением не более

Уважаемый посетитель!

Чтобы распечатать файл, скачайте его (в формате Word).

Ссылка на скачивание - внизу страницы.