Федеральное агентство связи

Государственное образовательное учреждение

высшего профессионального образования

«Сибирский государственный университет

телекоммуникаций и информатики»

(ФГОБУ ВПО «СИБГУТИ»)

кафедра Технической Электроники

«Синтез и исследование базовых элементов ТТЛ, ТТЛШс использованием макромоделей»

Выполнила: ст. гр. Н-05

Осадшая Н.О.

Проверил: доцент, к.т.н.

Брикман А.И.

Новосибирск, 2014

1. Цель работы

Создание ММ для описания TTL/TTLS.

Проверка корректности ММ по результатам исследования основных свойств.

2. Подготовка к работе.

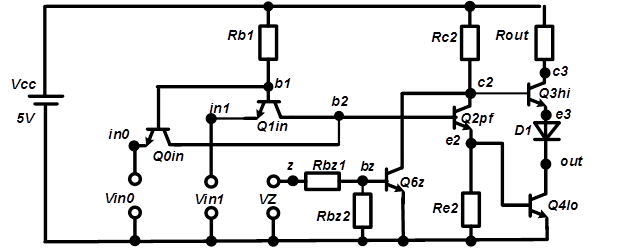

2.1.Схема для составления ММ TTL2Z– Рис.6.3.

В рамках Л.Р. нужно будет создать ММ МЭТ, которая будет присутствовать в схеме 2И-НЕ вместо двух транзисторов Q0in и Q1in.

Имя создаваемой модели – MET. Внешние узлы– in0, in1, b1, b2.

Описание ММ MET находится в том же файле, что и описание основной ММ TTL2Z. Но теперь эти два транзистора входят в нее, как единая ММ со своим ID Xind.

Транзистор KT315E

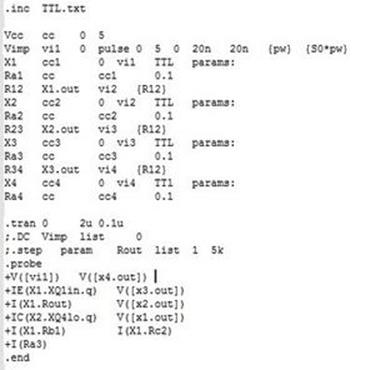

3. Программа описания схемы в PSpice.

3.1. Для лабораторной работы №6.

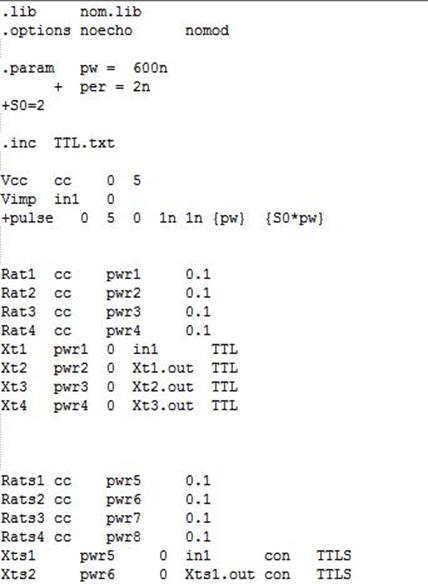

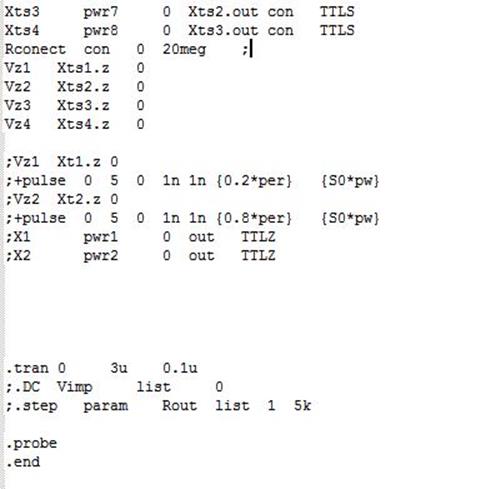

3.2. Для лабораторной работы№7

4. Полученные графики и таблицы.

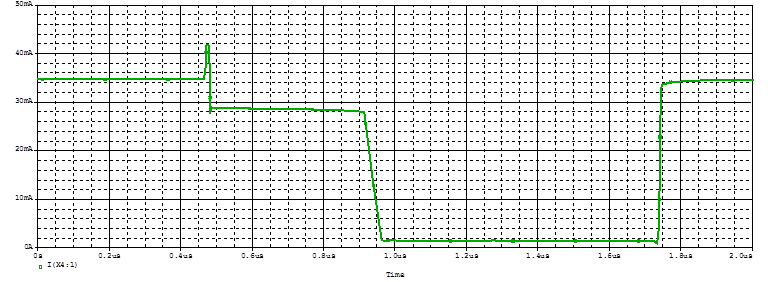

4.1. Определение статического потребления тока.

Таблица 6.1.

|

Iin |

Iout |

I(Rb1) |

I(Rc2) |

|

|

Vin="1" |

0.3m |

36.9m |

0.98m |

2.20m |

|

Vin="0" |

-1.5m |

37.4m |

1.6m |

2.24m |

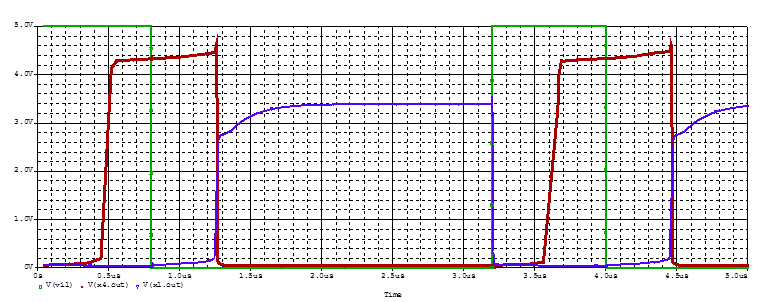

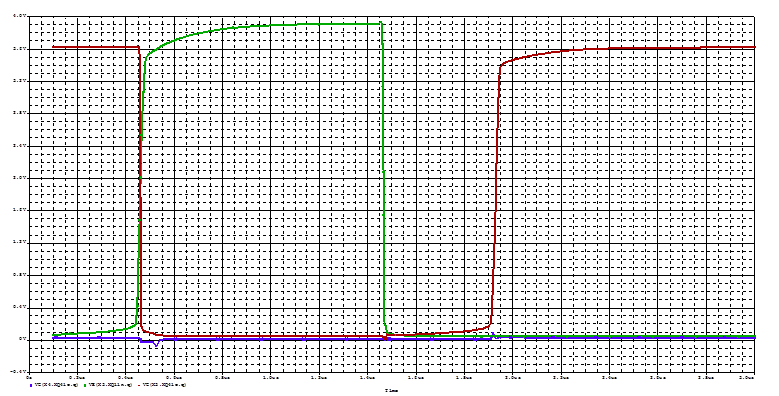

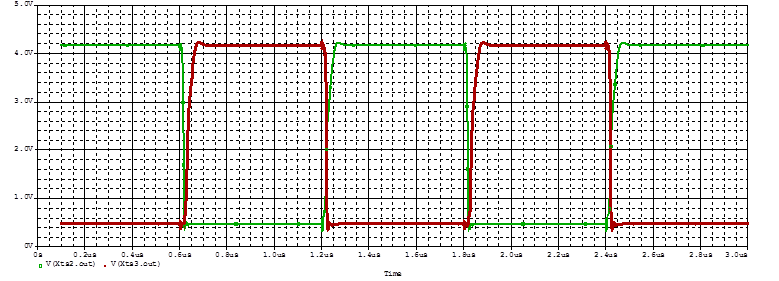

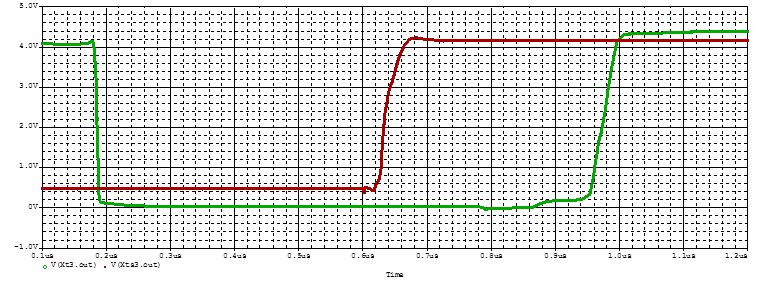

4.2. Исследование динамических свойств элемента TTL.

При определении параметров моделирования, значения pw=200 nsоказалось не достаточным. Для более наглядной работы с графиком, приняли pw=800 ns.

Таблица 6.2.

|

TTL1 |

TTL2 |

TTL3 |

TTL4 |

TTL3 (Z ßà"0") |

TTL3 (Z ßà"1") |

|

|

ton |

0.56u |

2.53n |

0.45n |

1.34n |

0.46n |

1.72n |

|

toff |

1.81n |

1.4u |

0.58u |

0.62u |

0.58u |

1.83u |

|

tdel |

0.28u |

0.7u |

0.29u |

0.31u |

0.29u |

0.9u |

Таблица 6.3.

|

ISTAT("1") |

ISTAT("0") |

ISTAT.СР |

IПОТР.("СР") |

IDIN.CP. |

|

|

S=2 |

24.6m |

3.05m |

18.6m |

25m |

18m |

|

S=3 |

24.5m |

3.5m |

18.6m |

24m |

16.6m |

|

S=1.5 |

24.4m |

14.6m |

19.5m |

23m |

13.8m |

|

S=2, tf=tr=20n |

24.5m |

18.5m |

12.25m |

22.5m |

12.9m |

|

*S=2, f=2∙f0 |

24.3m |

13.7m |

18m |

21m |

12.6m |

|

*S=2, f=0.5∙f0 |

22.0m |

10.5m |

16m |

19m |

11.5m |

4.4. Для доказательства правильности (п.п.3.2.5.)

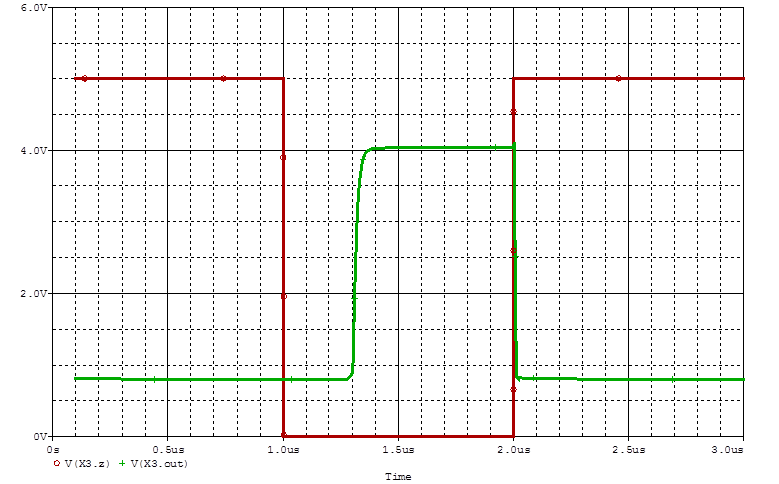

5.Исследование схем с Z-состоянием на выходе.

|

Iin, мА |

Iout, мА |

I(Rb1) , мА |

I(Rc2) , мА |

I(Ra), мА |

|

|

Vin="1" |

3.35 |

25.44 |

0.84 |

0.012 |

26.39 |

|

Vin="0" |

-1.48 |

0 |

1.48 |

2.49 |

3.96 |

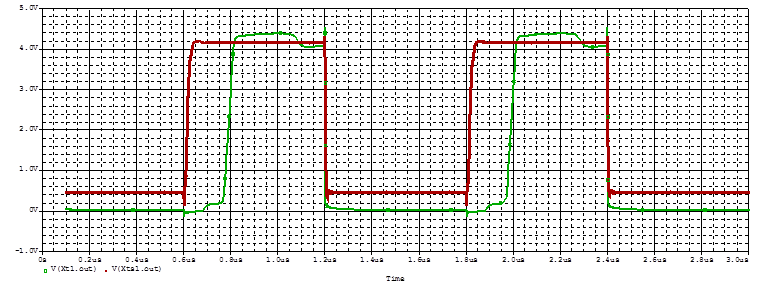

5.1. При Z-состоянии только элемента TTL3

5.2. При Z-состоянии только элемента TTL4

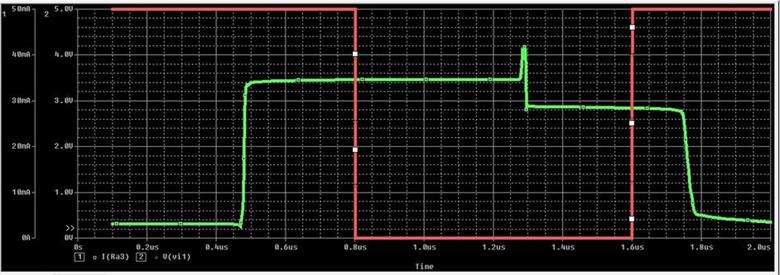

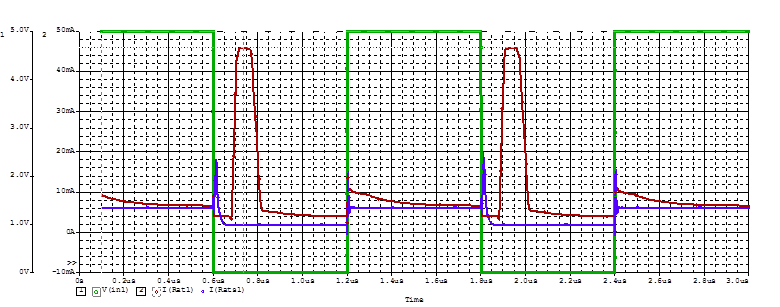

5.3.Определение времен задержки для выхода с Z-состоянием.

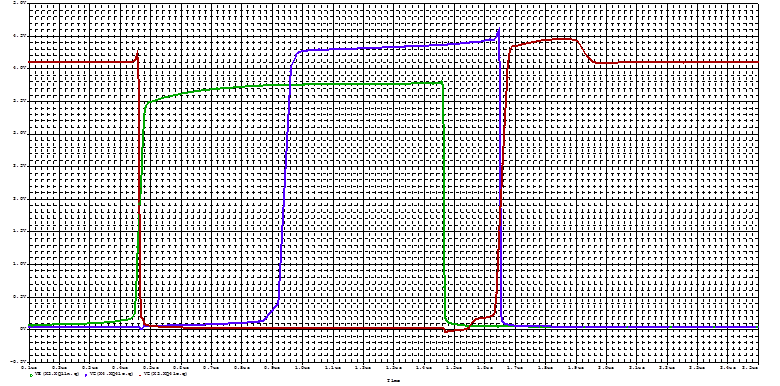

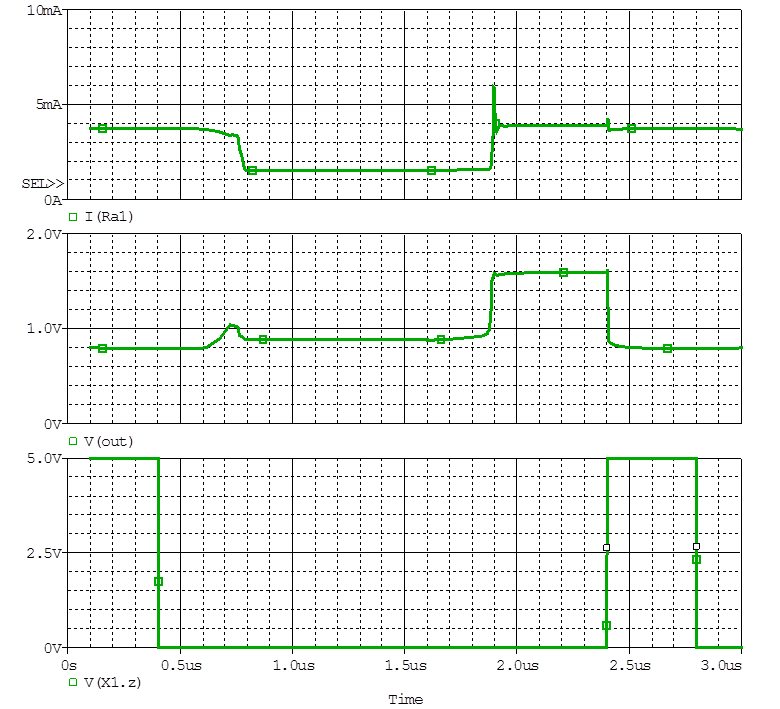

5.4. Конфликты на выходе при наличии/отсутствии Z-состояния.

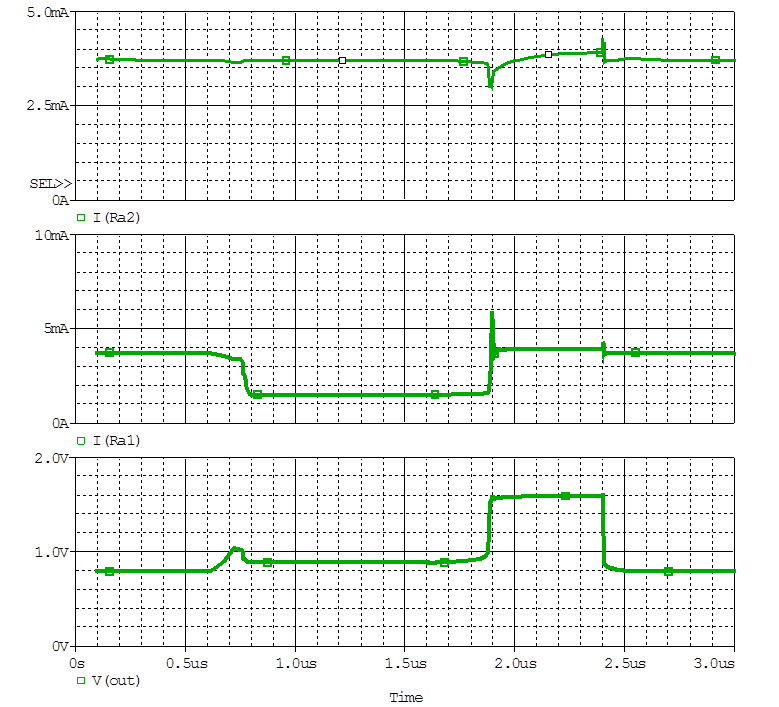

1)

бесконфликтная

ситуация для TTL1: Vin1, Vout, I(Ra1)

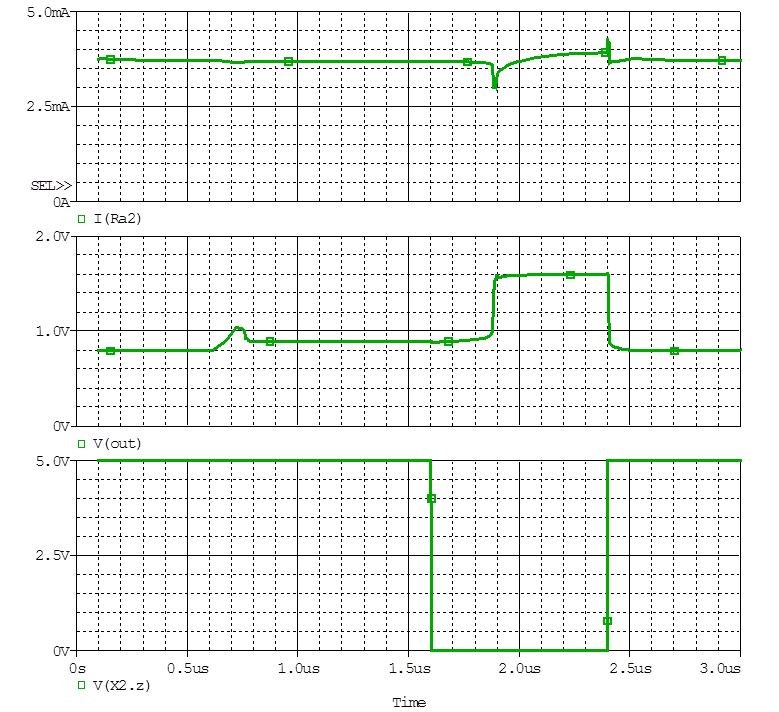

2)

бесконфликтная

ситуация для TTL2, Vin2, Vout, I(Ra2)

3)

конфликтная

ситуация: Vout, I(Ra1), I(Ra2)

Задания к лабораторной работе №7.

6.1. Получение СПХ. Определение порога переключения.

6.2. Определение статического потребления тока.

|

I(Rttl) |

I(Rttls) |

|

|

Vin = «1» |

6.86mA |

6.16mA |

|

Vin = «0» |

45.78mA |

2.004mA |

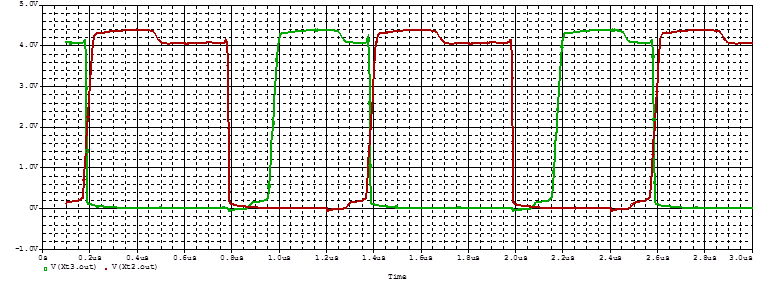

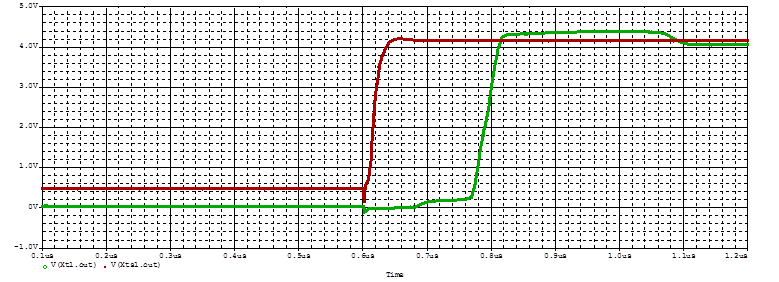

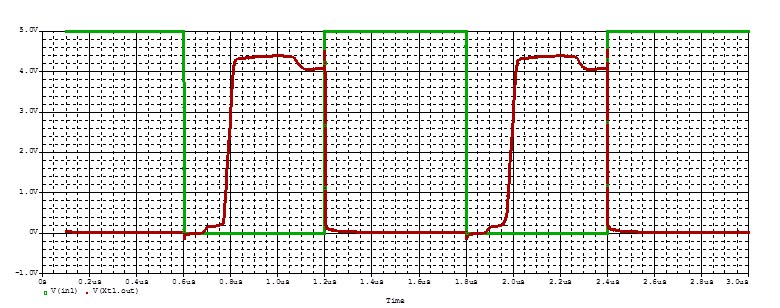

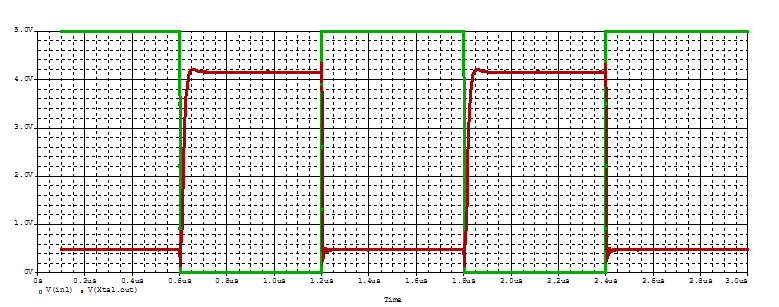

6.3. Сравнение динамических свойств элементов TTL иTTLS.

6.3.1. Измерение времен задержки.

|

TTL3 |

TTLS3 |

|

|

ton |

3.34ns |

0.51ns |

|

toff |

0.19us |

0.16ns |

|

tdel |

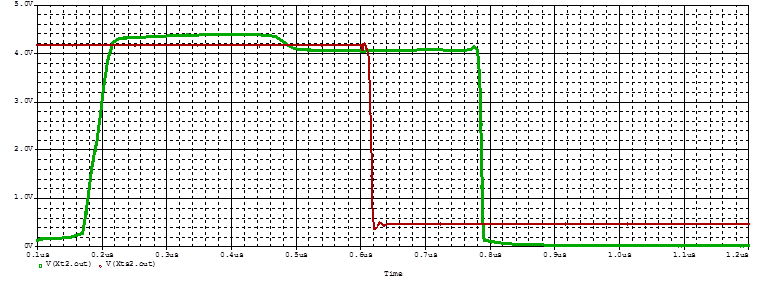

6.3.2. Статическое и динамическое потребление тока.

|

TTL |

TTLS |

|||||

|

Iпотр.(ср) |

Istat.cp |

Idin.cp. |

Iпотр.(ср) |

Istat.cp |

Idin.cp. |

|

|

S=2, tr=tf=1n |

9.78mA |

12.46mA |

7.63mA |

4.33mA |

4.54mA |

4.18mA |

|

S=2, tr=tf=50n |

10.46mA |

11.73mA |

7.71mA |

4.74mA |

5.12mA |

4.46mA |

6.3.3. Определение максимальной частоты.

6.3.4.1. Рост запаздывания переключения у TTL.

6.3.4.2. Выходной сигнал теряет цифровую форму.

Уважаемый посетитель!

Чтобы распечатать файл, скачайте его (в формате Word).

Ссылка на скачивание - внизу страницы.