ЛАБОРАТОРНАЯ РАБОТА №1

ШИФРАТОРЫ

ЦЕЛЬ РАБОТЫ: изучение возможностей построения шифраторов большой емкости на базе интегральных микросхем (ИМС), выполняющих функции шифраторов меньшей емкости.

КРАТКИЕ

СВЕДЕНИЯ ИЗ ТЕОРИИ. Шифратором называется комбинационная схема, преобразующая

код ![]() в двоичный. В шифраторе сигнал поступает

только на один вход, формируя при этом соответствующий ему двоичный код на

в двоичный. В шифраторе сигнал поступает

только на один вход, формируя при этом соответствующий ему двоичный код на ![]() выходах. Полный шифратор имеет

выходах. Полный шифратор имеет ![]() входов и

входов и ![]() выходов.

Для краткости записи будем обозначать его как шифратор

выходов.

Для краткости записи будем обозначать его как шифратор ![]() .

.

В

настоящее время в отдельных сериях ИМС изготовляются микросхемы, выполняющие

функции шифраторов. В таких схемах кроме ![]() информационных

выходов имеется еще служебный выход

информационных

выходов имеется еще служебный выход ![]() . На служебном выходе

формируется сигнал выбора данного шифратора, так что сигнал на выходе

. На служебном выходе

формируется сигнал выбора данного шифратора, так что сигнал на выходе ![]() появляется только при появлении сигнала на

одном из его входов. Условное изображение шифратора приведено на рис. 1.1.

появляется только при появлении сигнала на

одном из его входов. Условное изображение шифратора приведено на рис. 1.1.

Поскольку шифраторы как самостоятельные изделия имеют ограниченное число входов, то если требуемое число входных шин превосходит возможности одной микросхемы, приходится производить наращивание шифратора.

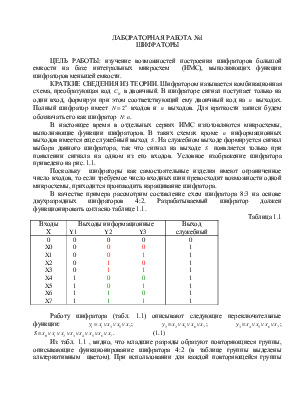

В качестве примера рассмотрим составление схем шифратора 8:3 на основе двухразрядных шифраторов 4:2. Разрабатываемый шифратор должен функционировать согласно таблице 1.1.

ВходыХ |

Выходы информационные Y1 Y2 Y3 |

Выход служебный |

|

0 X0 X1 X2 X3 X4 X5 X6 X7 |

0 0 0 0 0 0 0 0 1 0 1 0 0 1 1 1 0 0 1 0 1 1 1 0 1 1 1 |

0 1 1 1 1 1 1 1 1 |

Работу

шифратора (табл. 1.1) описывают следующие переключательные функции: ![]() ;

; ![]() ;

; ![]() ;

; ![]() . (1.1)

. (1.1)

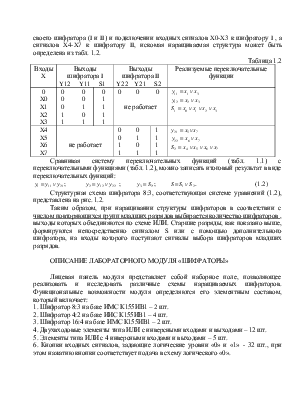

Из табл. 1.1 , видно, что младшие разряды образуют повторяющиеся группы, описывающие функционирование шифратора 4:2 (в таблице группы выделены альтернативным цветом). При использовании для каждой повторяющейся группы своего шифратора (I и II) и подключении входных сигналов X0-X3 к шифратору I , а сигналов X4-X7 к шифратору II, искомая наращиваемая структура может быть определена из табл. 1.2.

ВходыX |

Выходы шифратора I Y12 Y11 S1 |

Выходы шифратора II Y22 Y21 S2 |

Реализуемые переключательные функции |

||

|

0 X0 X1 X2 X3 |

0 0 0 0 0 1 1 0 1 1 |

0 1 1 1 1 |

0 0 0 не работает |

|

|

|

X4 X5 X6 X7 |

не работает |

0 0 0 1 1 0 1 1 |

1 1 1 1 |

|

|

Сравнивая систему переключательных функций (табл. 1.1) с переключательными функциями (табл. 1.2), можно записать итоговый результат в виде переключательных функций:

![]() ;

; ![]() ;

; ![]() ;

; ![]() . (1.2)

. (1.2)

Структурная схема шифратора 8:3, соответствующая системе уравнений (1.2), представлена на рис. 1.2.

Таким образом, при наращивании структуры шифраторов в соответствии с числом повторяющихся групп младших разрядов выбирается количество шифраторов , выходы которых объединяются по схеме ИЛИ. Старшие разряды, как показано выше, формируются непосредственно сигналом S или с помощью дополнительного шифратора, на входы которого поступают сигналы выбора шифраторов младших разрядов.

Лицевая панель модуля представляет собой наборное поле, позволяющее реализовать и исследовать различные схемы наращиваемых шифраторов. Функциональные возможности модуля определяются его элементным составом, который включает:

1. Шифратор 8:3 на базе ИМС К155ИВ1 – 2 шт.

2. Шифратор 4:2 на базе ИИС К155ИВ1 – 4 шт.

3. Шифратор 16:4 на базе ИМС К155ИВ1 – 2 шт.

4. Двухвходовые элементы типа ИЛИ с инверсными входами и выходами – 12 шт.

5. Элементы типа ИЛИ с 4 инверсными входами и выходами – 5 шт.

6. Кнопки входных сигналов, задающие логические уровни «0» и «1» - 32 шт., при этом нажатию кнопки соответствует подача в схему логического «0».

7. Элементы индикации (светодиоды) – 10 шт. Включение светодиодов происходит при подаче нулевого уровня на их свободные входные гнезда, так что свечение индикаторов происходит от сигнала «0».

Микросхема

К155ИВ1, являющаяся шифратором 8:3 (рис.1.3), имеет 8 входных шин: 0, 1, 2, 3,

4, 5, 6, 7; стробирующий вход Е и три информационных выхода 1, 2, 4, на которых

формируется трехразрядное двоичное число, а также один служебный выход ![]() . Следует иметь ввиду, что все входные и

выходные сигналы данной микросхемы являются инверсными.

. Следует иметь ввиду, что все входные и

выходные сигналы данной микросхемы являются инверсными.

Гнезда стробирующих входов Е на лицевой панели модуля отсутствуют, так как все микросхемы модуля поддерживаются в рабочем состоянии за счет подачи на входы Е сигнала нулевого уровня путем соединения с общей точкой панели модуля. Шифраторы на 4 и 16 входов в составе серии ИМС К155 на момент создания стендов не выпускались, поэтому шифраторы на указанное число входов организованы на ИМС К155ИВ1. В качестве логического элемента ИЛИ с инверсными входами-выходами используются элементы К155ЛИ1 и К155ЛИ6, которые являются конъюнкторами с 2 и 4 входами (рис. 1.4).

1. Ознакомиться с описанием лабораторной работы, краткими сведениями из теории и элементным составом модуля.

2. Получить у преподавателя техническое задание, в соответствии, с которым составить таблицу истинности синтезируемого шифратора. Номер варианта задания задается в таблице 1.3.

3.

Составить таблицу функционирования микросхемы шифратора, используемого в

наращиваемой структуре. Для выполнения этого пункта подключить входы микросхемы

к входным кнопкам, а выходы к светодиодам. Подать поочередно входные сигналы

кода ![]() и зафиксировать соответствующие им

выходные комбинации. Обратить внимание на логические уровни входных и выходных

сигналов.

и зафиксировать соответствующие им

выходные комбинации. Обратить внимание на логические уровни входных и выходных

сигналов.

4. Осуществить синтез структуры шифратора.

5. Составить принципиальную схему шифратора п. 4.

6. Набрать схему шифратора на лабораторном стенде и проанализировать его работу.

1. Техническое задание.

2. Таблица истинности синтезируемого (наращиваемого) шифратора.

3. Таблица функционирования используемой микросхемы.

4. Обоснование структуры наращивания шифратора.

5. Принципиальная схема шифратора.

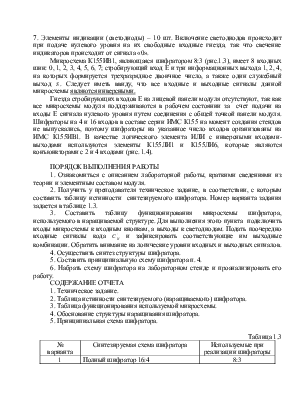

|

№ варианта |

Синтезируемая схема шифратора |

Используемые при реализации шифраторы |

|

1 2 3 4 5 6 |

Полный шифратор 16:4 Полный шифратор 16:4 Полный шифратор 16:4 Полный шифратор 32:4 Шифратор

кода с проверкой на четность Шифратор

для кода с постоянным весом |

8:3 4:2 8:3 и 4:2 16:4 любые любые |

Тутевич В. Н. Телемеханика.-М: Высшая школа.

Применение интегральных микросхем в электронной вычислительной технике /Под ред. Б. Н. Файзулаева, Б. В. Тарабрина. –М: Радио и связь, 1986./

Уважаемый посетитель!

Чтобы распечатать файл, скачайте его (в формате Word).

Ссылка на скачивание - внизу страницы.