|

№ |

С избытком три |

|||

|

0 |

Х |

Х |

Х |

Х |

|

1 |

Х |

Х |

Х |

Х |

|

2 |

Х |

Х |

Х |

Х |

|

3 |

0 |

0 |

1 |

1 |

|

4 |

0 |

1 |

0 |

0 |

|

5 |

0 |

1 |

0 |

1 |

|

6 |

0 |

1 |

1 |

0 |

|

7 |

0 |

1 |

1 |

1 |

|

8 |

1 |

0 |

0 |

0 |

|

9 |

1 |

0 |

0 |

1 |

|

10 |

1 |

0 |

1 |

0 |

|

11 |

1 |

0 |

1 |

1 |

|

12 |

1 |

0 |

1 |

1 |

|

13 |

Х |

Х |

Х |

Х |

|

14 |

Х |

Х |

Х |

Х |

|

15 |

Х |

Х |

Х |

Х |

1. Структурный тип счетчика – параллельный (синхронный).

2. В счетчике предусмотрена возможность переноса в старший разряд.

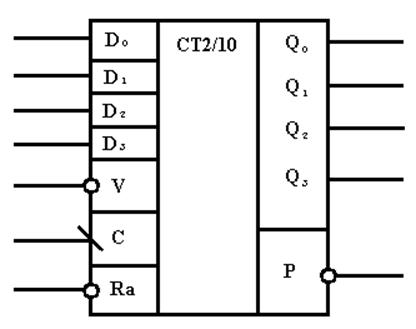

3. Условное графическое обозначение счетчика.

4. Таблица назначение выводов счетчика:

№ выводов |

Назначение |

№ выводов |

Назначение |

D0D1 D2 D3 |

Вход записи |

С |

Вход тактовый |

Вход записи |

Q0Q1 Q2 Q3 |

Выход |

|

Вход записи |

Выход |

||

Вход записи |

Выход |

||

V |

Вх разрешения записи |

Выход |

|

Ra |

Вход асинхронного обнуления |

P |

Выход переноса |

|

Режим |

Вход |

Выход |

||||

|

|

|

|

|

|

|

|

|

Сброс |

0 |

Х |

Х |

Х |

0 |

0 |

|

Параллельная загрузка |

1 |

Х |

0 |

0 |

0 |

0 |

|

1 |

Х |

0 |

1 |

1 |

0 |

|

|

Счёт |

1 |

↓ |

1 |

Х |

Счёт |

X |

* Состояние входа P определяется состоянием выходов счетчика. Если код на выходах счетчика соответствует цифре 9, то на выход Р будет уровень логического «0». Во всех остальных случаях на выходе Р будет уровень логической «1».

4.Выбор и описание работы элементной базы.

В качестве элементной базы в работе задана ТТЛШ (ALS) логика, которая широко используется в быстродействующих цифровых микросхемах. Вместо обычных биполярных транзисторов в этих элементах используется транзистор Шотки, это позволяет сократить время рассасывания избыточного заряда по сравнению с обычным биполярным транзистором на 3-4 порядка.

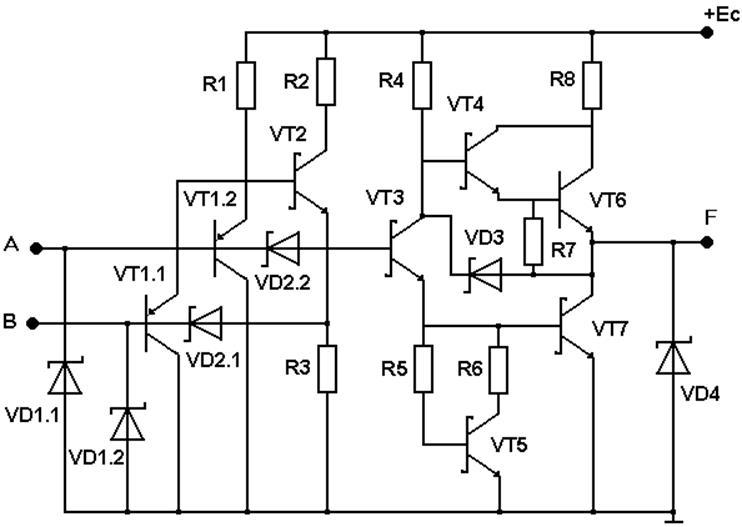

На рис. 2 показана схема базового логического элемента заданной К1533 серии.

Рис. 2 Принципиальная схема базового ЛЭ И-НЕ серии К1533.

Схема содержит три основных каскада: входной, выполненный на транзисторах VT1.1, VT1.2, VT2 диодах VD1.1, VD1.2 и резисторах R1и R2; фазовращательный, включающий транзисторы VT3, VT5, диоды VD2.1 и VD2.2 и резисторы R4 – R6; выходной усилитель состоящий из транзисторов VT4, VT6, VT7 и резисторов R7 и R8.

Повышение быстродействия способствует применение на выходе диодов Шотки с малыми площадью и ёмкостью.

При низком напряжении на входе на базе транзистора VT2поддерживается низкое напряжение, которое недостаточное для его отпирания. Транзисторы VT2,VT3 и VT7 закрыты. Высокое напряжение на входе транзистора VT4 открывает его, а также транзистор VT6. На выходе схемы устанавливается напряжение высокого уровня.

Уважаемый посетитель!

Чтобы распечатать файл, скачайте его (в формате Word).

Ссылка на скачивание - внизу страницы.