Министерство образования и науки РФ

Новосибирский Государственный Технический Университет

Кафедра ВТ

КУРСОВАЯ РАБОТА

по дисциплине «Организация ЭВМ»

Факультет: АВТ

Группа: АМ 211

Студент: Слуцкий А.А.

Проверил: Гребенников В.Ф.

Новосибирск 2005

Цели работы.. 3

Исходные данные. 3

Общие исходные данные. 3

Индивидуальные исходные данные. 3

Разработка структурной схемы ЦП.. 4

Система прерываний. 6

Радиальная структура (с несколькими линиями запроса). 7

Прерывания на макроуровне. 7

Память. 8

Страничная организация памяти. 8

Адресный КЭШ... 9

Адресный сопроцессор. 10

Клавиатура и монитор,таймер. 11

Начальная инициализация ЭВМ. 11

Система ввода-вывода. 11

Разработка функциональной схемы контроллера ПДП. 11

Список литературы. 14

Целью курсового проектирования является углубление и закрепление теоретических знаний студентов, приобретение навыков разработки узлов ЭВМ на структурном, функциональном и алгоритмическом уровнях.

Курсовой проект посвящен разработке структурной схемы гипотетической ЭВМ, принципиальной схемы и алгоритма(ов) работы конкретного блока, входящего в состав этой ЭВМ.

центральное обрабатывающее устройство (ЦОУ);

микропрограммное устройство управления (УУ);

оперативная память (ОП);

блок синхронизации (БС);

система прерывания программ (СПП);

таймер;

система ввода-вывода (СВВ);

монитор, клавиатура, мышь;

структура: 3-х шинная состав и наличие сопроцессора: адресный сопроцессор система прерывания: прерывание ридиальное, макро

КЭШ: адресный КЭШ (буфер TLB)

оперативная память: страничная

Ввод/Вывод: в/в ПДП

наличия системы контроля: контроль по приоритету в/в разрабатываемый блок: разработать блок-контроллер ПДП

В качестве опорного микропроцессорного комплекта было предложено взять серию КМ1804. В томе 2 литературы [1], а так же в книге [2] приведено подробнейшее описание данного комплекта: структурные схемы, временные диаграммы работы, примеры соединения микросхем в функционально законченные устройства.

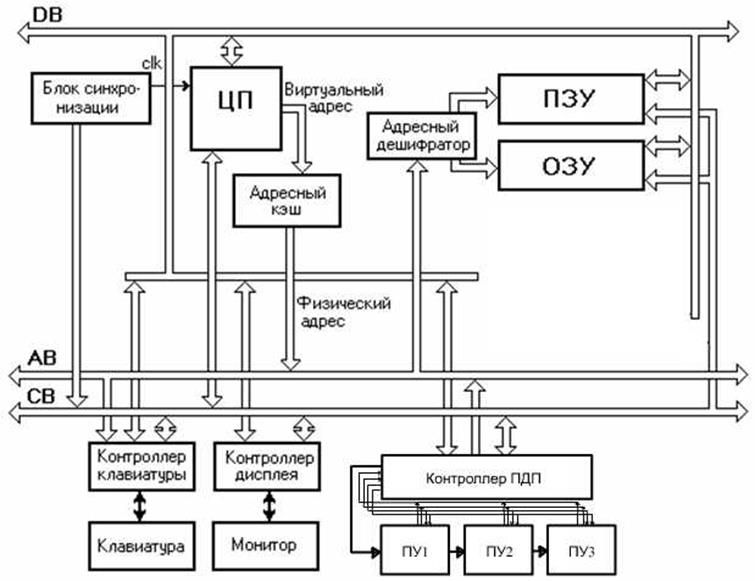

Общая типовая структура для трехшинной ЭВМ приведена ниже (рис. 1). В соответствии с заданием, разрабатывалась ЭВМ с трехшинной организацией: шиной данных, шиной адреса, шиной управления. Двунаправленная шина данных (DB) – 16 разрядная, обеспечивает обмен данными между блоками ЭВМ. Также 16 разрядная, шина адреса (AB) – используется для задания адреса памяти, которым может быть как адрес в ОЗУ, ПЗУ (в соответствии с картой памяти) так и адрес видеопамяти контроллера монитора. Шина управления – осуществляется управления блоками ЭВМ.

|

Один из основных блоков ЭВМ является центральный процессорный модуль (рис. 2).

В состав 16 разрядного (в нашем случае) центрального процессора входит операционный блок (ОБ) и микропрограммное устройство управления (МУУ). МУУ осуществляет управление работой секций, а операционный блок - арифметические, логические, сдвиговые операции, выполняет инструкции МУУ.

Микропрограммное устройство управления (МУУ) – устройство, с помощью которого можно отыскать в микропрограммной памяти (МПП) следующую команду программы и связанные с этой командой данные. МУУ объединяет в себе РгК и средства формирования Мк: ПНА, секвенсор (в нашем случае это КМ1804ВУ4), МПП, а так же конвейерный регистр микрокоманд (Рг.МК)

Код операции из регистра команд поступает на вход преобразователя начального адреса (ПНА), который быть может выполнен на микросхеме ПЛМ К556РТ1. Преобразованный адрес с ПНА поступает на секвенсор. Секвенсор выбирает источник адреса и выдает его на вход МПП. На выходах последней появляется микрокоманда. Далее микрокоманда фиксируется в регистре микрокоманд (КМ1804ИР1/ИР2). Микрокоманда хранится в там в течение времени ее выполнения. В момент, когда микрокоманда начинает выполняться, секвенсор формирует адрес следующей микрокоманды.

ОБ в свою очередь, состоит из:

Уважаемый посетитель!

Чтобы распечатать файл, скачайте его (в формате Word).

Ссылка на скачивание - внизу страницы.