переходу LOW-to-HIGH, при высоком уровне регистр F сохраняет предыдущее содержимое

FT0 – входной, сквозное управление регистром ввода. При высоком уровне регистры R и S прозрачны

FT1 – входной, сквозное управление регистром вывода. При высоком уровне регистры F и состояния (флагов статуса) прозрачны

I0-I1 – входные, линии выбора операции. Каждой операции соответствует свой код

I3 – входной, выбор входного порта S сопроцессора. Низкий уровень выбирает регистр S как входной для порта сопроцессора S, высокий – выбирает регистр F

I4 – входной, выбор входного порта R сопроцессора. Низкий уровень выбирает R0-R31 как входные для регистра R, высокий – выбирает как входной регистр F

![]() - выбор режима

- выбор режима ![]() ,

входной. При высоком уровне выбирается режим IEEE, при

низком DEC

,

входной. При высоком уровне выбирается режим IEEE, при

низком DEC

INEXACT – выходной, флаг неточного результата. Высокий уровень означает, что результат последней операции недостаточно точен вследствие округления

INVALID – выходной, флаг недопустимой операции. Высокий уровень означает, что последняя операция была недопустимой

NAN – выходной, флаг нечислового результата. Высокий уровень означает, что результат последней операции не может быть интерпретирован как число

![]() - входной, разрешает вывод. При низком

уровне содержимое регистра F помещается

в F0-F31, при высоком F0-F31 переходят в высокоимпедансное

состояние

- входной, разрешает вывод. При низком

уровне содержимое регистра F помещается

в F0-F31, при высоком F0-F31 переходят в высокоимпедансное

состояние

ONEBUS – входной, управление входной шиной. Низкий уровень задает работу в двухшинном режиме, высокий – в одношинном

OVERFLOW – флаг переполнения, выходной. Высокий уровень означает, что последняя операция с плавающей точкой вызвала переполнение

![]() - входной, выбирает режим PROJECTIVE (высокий уровень) или AFFINE (низкий).

- входной, выбирает режим PROJECTIVE (высокий уровень) или AFFINE (низкий).

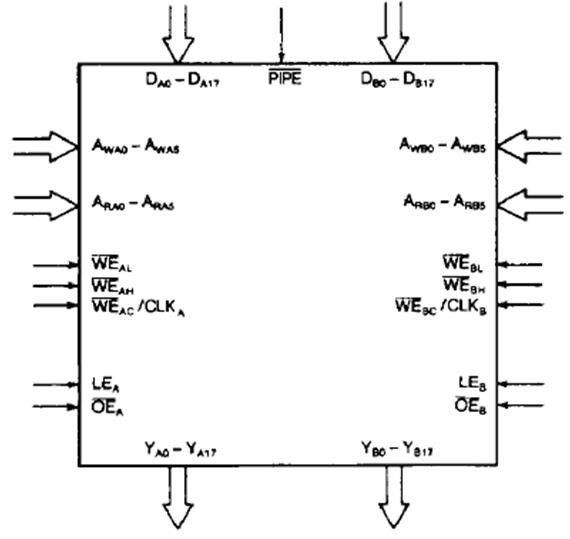

Приложение 5. АМ29334 - четырехпортовый регистровый файл

|

Логический символ АМ29334

Назначение выводов регистрового файла АМ29434

ARA0-ARA5 – входные, адрес чтения A-Side. 6 разрядов адреса выбирают одну из 64 ячеек памяти для вывода на YA регистра-защелки Data Latch

ARB0-ARB5 – входные, адрес чтения B-Side, 6 разрядов адреса выбирают одну из 64 ячеек памяти для вывода на YВ регистра-защелки Data Latch

AWA0-AWA5 – входные, адрес записи A-Side. 6 разрядов адреса записи выбирают одну из 64 ячеек памяти для записи новых данных со входа DA

AWB0-AWB5 – входные, адрес записи B-Side. 6 разрядов адреса записи выбирают одну из 64 ячеек памяти для записи новых данных со входа DB

DA0-DA17 – входные данные A-Side. Новые данные записываются в память с этого входа, если это задано адресным входом AWA

DB0-DB17 – входные данные B-Side. Новые данные записываются в память с этого входа, если это задано адресным входом AWB

![]() -

входной сигнал, низкий уровень разрешает доступ к регистрам ввода и вывода для

конвейерных операций. При низком уровне регистры прозрачные

-

входной сигнал, низкий уровень разрешает доступ к регистрам ввода и вывода для

конвейерных операций. При низком уровне регистры прозрачные

![]() -

входной, активный уровень – низкий. Разрешение записи в A-Side.

Если

-

входной, активный уровень – низкий. Разрешение записи в A-Side.

Если ![]() низкий одновременно с

низкий одновременно с ![]() и

и ![]() ,

новые данные записываются в ячейку, выбранную по адресу AWA. При высоком

,

новые данные записываются в ячейку, выбранную по адресу AWA. При высоком ![]() данные

в RAM через порт А не записываются.

данные

в RAM через порт А не записываются. ![]() работает как тактирующий вход в

конвейерном режиме для стороны А.

работает как тактирующий вход в

конвейерном режиме для стороны А.

![]() -

входной, активный уровень – низкий. Разрешение записи в В-Side.

Если

-

входной, активный уровень – низкий. Разрешение записи в В-Side.

Если ![]() низкий одновременно с

низкий одновременно с ![]() и

и ![]() ,

новые данные записываются в ячейку, выбранную по адресу AWВ. При

высоком

,

новые данные записываются в ячейку, выбранную по адресу AWВ. При

высоком ![]() данные в RAM через порт В

не записываются.

данные в RAM через порт В

не записываются. ![]() работает как

тактирующий вход в конвейерном режиме для стороны В.

работает как

тактирующий вход в конвейерном режиме для стороны В.

![]() -

разрешение записи старшего байта для стороны А (активный уровень – низкий).

Когда

-

разрешение записи старшего байта для стороны А (активный уровень – низкий).

Когда ![]() низкий одновременно с

низкий одновременно с ![]() , новые данные записываются в старший байт

выбранной по адресу AWA ячейки. При высоком

, новые данные записываются в старший байт

выбранной по адресу AWA ячейки. При высоком ![]() данные

в старший байт не записываются.

данные

в старший байт не записываются.

![]() -

разрешение записи старшего байта для стороны В (активный уровень – низкий).

Когда

-

разрешение записи старшего байта для стороны В (активный уровень – низкий).

Когда ![]() низкий одновременно с

низкий одновременно с ![]() , новые данные записываются в старший байт

выбранной по адресу AWВ ячейки.

При высоком

, новые данные записываются в старший байт

выбранной по адресу AWВ ячейки.

При высоком ![]() данные в старший байт не

записываются.

данные в старший байт не

записываются.

![]() -

разрешение записи младшего байта для стороны А (активный уровень – низкий).

Когда

-

разрешение записи младшего байта для стороны А (активный уровень – низкий).

Когда ![]() низкий одновременно с

низкий одновременно с ![]() , новые данные записываются в младший байт

выбранной по адресу AWA ячейки. При высоком

, новые данные записываются в младший байт

выбранной по адресу AWA ячейки. При высоком ![]() данные

в младший байт не записываются.

данные

в младший байт не записываются.

![]() -

разрешение записи младшего байта для стороны В (активный уровень – низкий).

Когда

-

разрешение записи младшего байта для стороны В (активный уровень – низкий).

Когда ![]() низкий одновременно с

низкий одновременно с ![]() , новые данные записываются в младший байт

выбранной по адресу AWВ ячейки.

При высоком

, новые данные записываются в младший байт

выбранной по адресу AWВ ячейки.

При высоком ![]() данные в младший байт не

записываются.

данные в младший байт не

записываются.

GND, VCC – питание для внутренней логики (0,5 В)

GNDА, VCCА – питание для драйверов вывода (0,5 В)

LEA YA – вход разрешения регистра-защелки (активный уровень высокий). Вход LEA управляет защелкой по выходному порту YA. При высоком LEA защелка открыта (прозрачна) и данные из RAM передаются на выход YA по адресу, выбранному адресными входами ARA. При низком уровне LEA защелка закрыта, что сохраняет последние считанные данные. LEA запрещен в конвейерном режиме.

LEВ YВ – вход разрешения регистра-защелки (активный уровень высокий). Вход LEВ управляет защелкой по выходному порту YВ. При высоком LEВ защелка открыта (прозрачна) и данные из RAM передаются на выход YВ по адресу, выбранному адресными входами ARВ. При низком уровне LEВ защелка закрыта, что сохраняет последние считанные данные. LEВ запрещен в конвейерном режиме.

![]() YA – разрешение вывода (активный уровень низкий). При низком

YA – разрешение вывода (активный уровень низкий). При низком ![]() данные с защелки YA

передаются на выход YA, при высоком – выход YA

находится в высокоимпедансном состоянии.

данные с защелки YA

передаются на выход YA, при высоком – выход YA

находится в высокоимпедансном состоянии.

![]() YВ – разрешение вывода (активный уровень низкий). При

низком

YВ – разрешение вывода (активный уровень низкий). При

низком ![]() данные с защелки YВ передаются на выход YВ, при высоком – выход YВ находится в высокоимпедансном состоянии.

данные с защелки YВ передаются на выход YВ, при высоком – выход YВ находится в высокоимпедансном состоянии.

YA0-YA17 – регистр-защелка, 18 бит выхода YA

YВ0-YВ17 – регистр-защелка, 18 бит выхода YВ

|

|||||||||||||||||||

|

|||||||||||||||||||

|

|||||||||||||||||||

|

|||||||||||||||||||

|

|||||||||||||||||||

|

|||||||||||||||||||

|

|||||||||||||||||||

|

|||||||||||||||||||

![]()

![]()

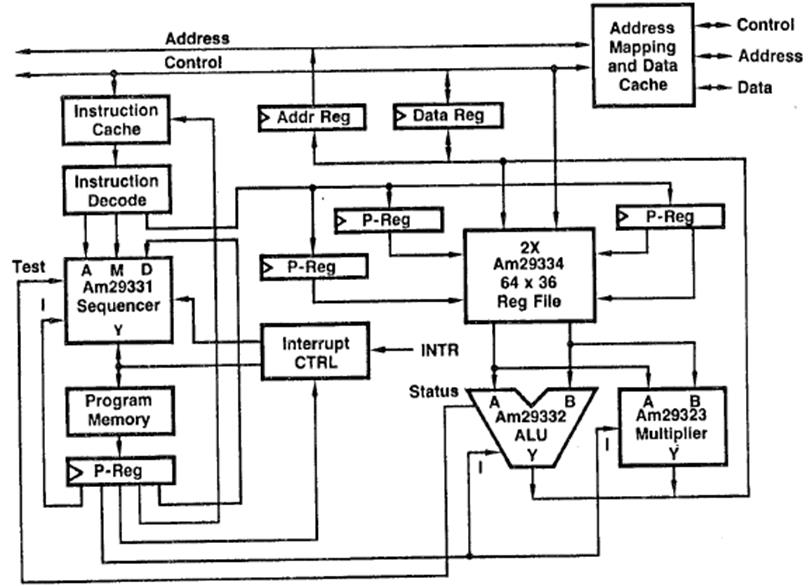

Приложение 6. Функциональная схема операционного

блока

Приложение 7. Структурная схема рекомендуемой фирмой AMD высокопроизводительной

Уважаемый посетитель!

Чтобы распечатать файл, скачайте его (в формате Word).

Ссылка на скачивание - внизу страницы.