![]()

![]()

![]()

![]() Министерство Образования Российской

Федерации

Министерство Образования Российской

Федерации

Пояснительная записка к курсовой работе по дисциплине «Цифровые устройства и микропроцессоры»

|

Проверил: |

Составил: |

|

Преподаватель |

Студент гр. РТ5-04 |

|

Родников В.В. |

Стародубцев А.В. |

Новосибирск

2003

Содержание

Номер варианта задания №53

1. Синтез конечного автомата (КА) Мили

1.1. Построить граф конечного автомата для заданного варианта

1.2. Определить количество элементов памяти

1.3. Составить таблицы переходов и выходов КА

1.4. Составить таблицу возбуждения элементов памяти

1.5. Синтезировать комбинационную часть КА

1.6. Реализовать КА на микросхемах одной из серий: К155, К176, К531, К555, К561, К564 (по указанию преподавателя). Составить полную логическую схему автомата.

2. Программная реализация автомата

2.1. Путем эквивалентного преобразования исходного автомата Мили в автомат Мура построить граф и таблицу переходов автомата Мура

2.2. Составить схему алгоритма и программу, реализующую автомат Мура на языке ассемблера микропроцессора (МП) К580.

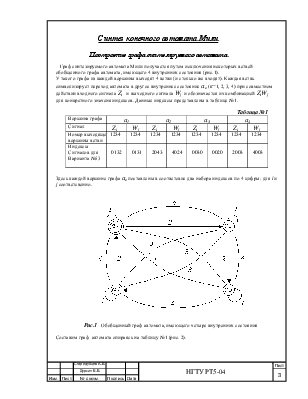

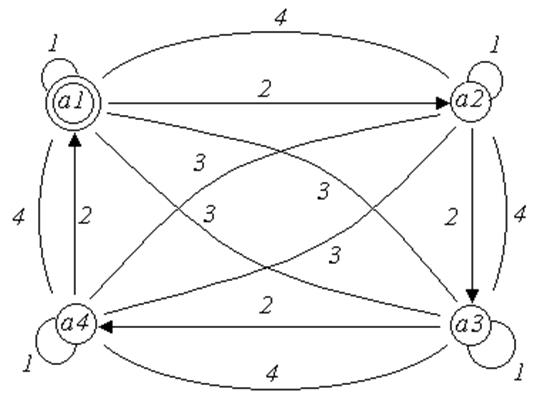

Граф синтезируемого автомата Мили получается путем исключения некоторых ветвей обобщенного графа автомата, имеющего 4 внутренних состояния (рис.1).

У такого графа из каждой вершины выходят 4 ветви (и столько же входят). Каждая ветвь символизирует переход автомата в другое внутреннее состояние ак (к=1, 2, 3, 4) при совместном действии входного сигнала Zi и выходного сигнала Wj и обозначается их комбинацией ZiWj для конкретного значеня индексов. Данные индексы представлены в таблице №1.

Таблица №1

|

Вершина графа |

а1 |

а2 |

а3 |

а4 |

||||

|

Сигнал |

Zi |

Wj |

Zi |

Wj |

Zi |

Wj |

Zi |

Wj |

|

Номер выходящей из вершины ветви |

1234 |

1234 |

1234 |

1234 |

1234 |

1234 |

1234 |

1234 |

|

Индексы Сигналов для Варианта №53 |

0132 |

0131 |

2043 |

4024 |

0030 |

0020 |

2003 |

4003 |

Здесь каждой вершине графа ак поставлены в соответсвие два набора индексов по 4 цифры: для i и j соответсвенно.

|

Рис.1 Обобщенный граф автомата, имеющего четыре внутренних состояния

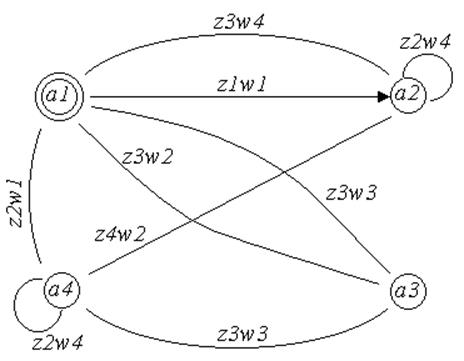

Составим граф автомата опираясь на таблицу №1 (рис. 2).

|

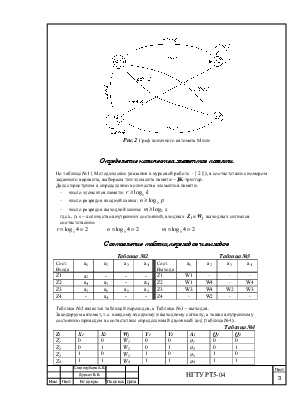

Определение количества элементов памяти

По таблице №1 ( Методические указания к курсовой работе - [ 2 ] ), в соответствии с номером заданного варианта, выбираем тип элемента памяти – JK-триггер.

Далее приступим к определению количества элементов памяти.

-

число элементов памяти: ![]()

-

число разрядов входной шины: ![]()

-

число разрядов выходной шины: ![]()

где k, p, s – количество внутренних состояний, входных Zi и Wj выходных сигналов соответственно.

![]()

Составление таблиц переходов и выходов

Таблица №2 Таблица №3

|

Сост. Входа |

a1 |

a2 |

a3 |

a4 |

Сост. Выхода |

a1 |

a2 |

a3 |

a4 |

|

Z1 |

a2 |

- |

- |

- |

Z1 |

W1 |

- |

- |

- |

|

Z2 |

a4 |

a2 |

- |

а4 |

Z2 |

W1 |

W4 |

- |

W4 |

|

Z3 |

a3 |

a1 |

a1 |

a3 |

Z3 |

W3 |

W4 |

W2 |

W3 |

|

Z4 |

- |

a4 |

- |

- |

Z4 |

- |

W2 |

- |

- |

Таблица №2 является таблицей переходов, а Таблица №3 – выходов.

Закодируем автомат, т.е. каждому входному и выходному сигналу, а также внутреннему состоянию приведем в соответствие определенный двоичный код (таблица №4).

Таблица №4

|

Zi |

X1 |

X2 |

Wj |

Y1 |

Y2 |

Ai |

Q1 |

Q2 |

|

Z1 |

0 |

0 |

W1 |

0 |

0 |

а1 |

0 |

0 |

|

Z2 |

0 |

1 |

W2 |

0 |

1 |

а2 |

0 |

1 |

|

Z3 |

1 |

0 |

W3 |

1 |

0 |

а3 |

1 |

0 |

|

Z4 |

1 |

1 |

W4 |

1 |

1 |

а4 |

1 |

1 |

Переведем таблицы выходов и переходов в двоичный алфавит.

Таблица переходов (δ)

|

X1X2 |

Q1Q2 |

|||

|

00 |

01 |

10 |

11 |

|

|

00 |

01 |

- |

- |

- |

|

01 |

11 |

01 |

- |

11 |

|

10 |

10 |

00 |

00 |

10 |

|

11 |

- |

11 |

- |

- |

Таблица выходов (λ)

|

X1X2 |

Q1Q2 |

|||

|

00 |

01 |

10 |

11 |

|

|

00 |

00 |

- |

- |

- |

|

01 |

00 |

11 |

- |

11 |

|

10 |

10 |

11 |

01 |

10 |

|

11 |

- |

01 |

- |

- |

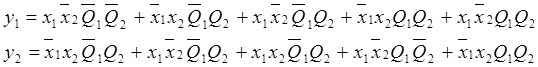

Составим логические уравнения для выходных сигналов y1 и y2.

Составление таблицы возбуждения памяти

Уважаемый посетитель!

Чтобы распечатать файл, скачайте его (в формате Word).

Ссылка на скачивание - внизу страницы.