Процесс происходит до тех пор пока не будет использован в умножении последний (самый младший) разряд множителя. Сумма всех частичных произведе-ний (с учетом сдвигов по разрядной сетке) даст окончательное произведение мантисс.

Для иллюстрации данного алгоритма можно привести пример умножения двух чисел с привязкой к разрядной сетке. Для удобства пример будет приведен в деся-тичной системе счисления.

Пусть необходимо умножить число Y=13721 на число X=49131 (знак произведения вычисляется отдельно, поэтому один разряд у сомножителей отсутствует). В таблице 1 моделируется разрядная сетка с частичными произведе-ниями в ней.

Таблица1.Пример умножения с привязкой к разрядной сетке

|

5 |

4 |

3 |

2 |

1 |

0 |

примечание |

|

0 |

4 |

4х1(не сдвигается) |

||||

|

0 |

8 |

4х2(сдвигается на 1 разряд) |

||||

|

2 |

8 |

4х7(сдвигается на 2 разряда) |

||||

|

1 |

2 |

4х3(сдвигается на 3 разряда) |

||||

|

0 |

4 |

4х1(сдвигается на 4 разряда) |

||||

|

1 |

8 |

9х2(не сдвигается) |

||||

|

6 |

3 |

9х7(сдвигается на 1 разряд) |

||||

|

2 |

7 |

9х3(сдвигается на 2 разряда) |

||||

|

0 |

9 |

9х1(сдвигается на 3 разряда) |

||||

|

0 |

7 |

1х7(не сдвигается) |

||||

|

0 |

3 |

1х3(сдвигается на 1 разряд) |

||||

|

0 |

1 |

1х1(сдвигается на 2 разряда) |

||||

|

0 |

9 |

3х3(сдвигается на 3 разряда) |

||||

|

0 |

3 |

3х1(сдвигается на 3 разряда) |

||||

|

0 |

1 |

1х1(не сдвигается) |

||||

|

0 |

6 |

7 |

4 |

1 |

0 |

←результатат |

4.Проектирование функциональной схемы.

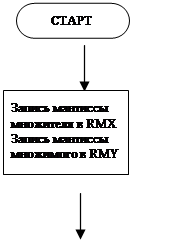

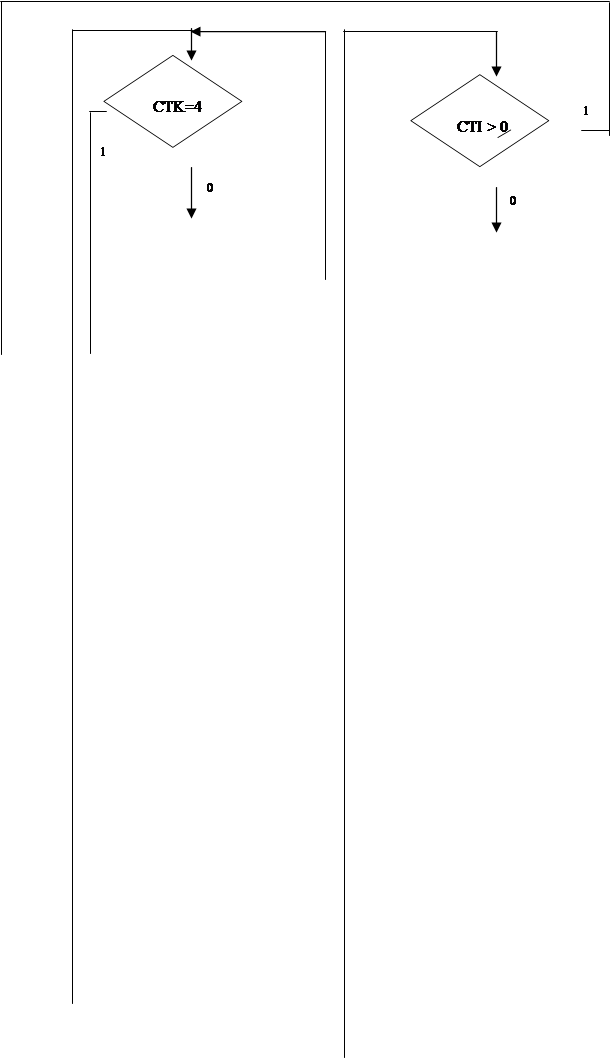

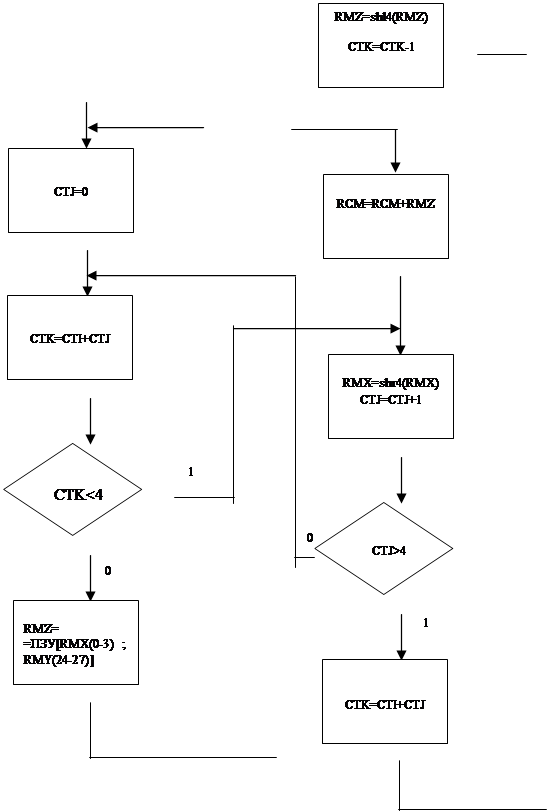

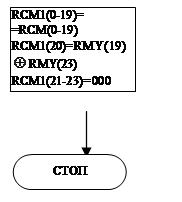

4.1.Регистровая блок-схема алгоритма.

|

|||

|

|||

|

|

|||

|

|||

Рис.1.Регистровая блок-схема алгоритма.

4.2.Описание функциональной схемы.

Функциональная схема строится на основе регистровой блок-схемы. Функциональная схема состоит из операционного и управляющего автомата.

Операционный автомат включает в себя следующие узлы:

– Регистры содержащие операнды: RGX, RGY;

– ПЗУ хранящую таблицу умножения шестнадцатиричных чисел (частичные произведения): ROM1;

– регистр моделирующий разрядную сетку (сдвиги частичных произведений):

RGZ;

– сумматор для суммирования частичных произведений: SM1;

– регистр для накопления суммы частичных произведений: RGCM;

– счетчик разрядов множителя: CT2I;

– счетчик разрядов множимого: CT2J;

– счетчик сдвигов: CT2K;

– компаратор для сравнения с 4 CT2I;

– компаратор для сравнения с 4 CT2K;

– сумматор для сложения содержимого счетчиков CT2I и CT2J: SM2;

– логический элемент «исключающее ИЛИ» для формирования знака результата;

– регистр результата: RGCM1.

Особенностью операционного автомата является загрузка операндов: в регистр

RGX заносится множитель без знкака (так как в RGX требуется циклический сдвиг а знак не должен учавствовать в вычислениях), а в RGY заносится множимое и знаки обоих сомножителей.

Управляющий автомат состоит из :

– ПЗУ управляющих слов (выдающее в операционный автомат сигналы записи данных в регистры, счетчики, сигналы сдвигов и т.д.): ROM2;

– регистр управляющих слов: RG;

– счетчик адресов управляющего ПЗУ: CT2;

– ПЗУ с адресами условных переходов: ROM3;

– КС выдающая сигнал записи в CT2 адреса условного перехода, если встретилось условие;

– схема сброса счетчика при включении питания;

– триггер обеспечивающий протокол обмена (принимающий сигнал старт);

Уважаемый посетитель!

Чтобы распечатать файл, скачайте его (в формате Word).

Ссылка на скачивание - внизу страницы.