Достоинства этого решения в более высокой скорости по сравнению с предыдущим вариантом, недостаток – некоторое аппаратных затрат; при маловероятных сдвигах затраты превышают необходимую величину для достижения аналогичного быстродействия.

На рис.6 представлена схема, являющаяся модификацией схемы , представленной на рис.4. Особенность этой схемы заключается в том, что максимальная частота сдвига достигает частоты тактового генератора.

Недостаток схемы – малое быстродействие. Достоинство – если максимальная частота тактирования близка к частоте тактирования регистра (но все же остается меньше на некоторую величину), то удельный вес затрат на единицу быстродействия минимален. Именно этот вариант выбран в качестве основного для разрабатываемого процессора.

В момент начала обмена внешнее устройство должно вырабатывать импульсы положительной полярности длительностью не менее

После этого внешнее устройство имеет право выставить на шину младший байт аргумента и подобрать синхроимпульс положительной полярности (CLK) через время

![]()

Длительность синхроимпульса положительной полярности должна быть не менее 10 нс (вход синхронизации ТМ8).

Длительность импульса отрицательной полярности по входу CLK должна быть не менее 10нс, при этом время между положительными фронтами CLK должно быть не менее

tCLK =t![]() CLK +

tПУАРГ, где

CLK +

tПУАРГ, где

t![]() CLK= t3

CLK= t3![]() Р ТМ8 + t3

Р ТМ8 + t3![]() Р

ЛАЗ + t3

Р

ЛАЗ + t3![]() Р ИР23=17+11+16=44нс,

Р ИР23=17+11+16=44нс,

tПУАРГ= t3![]() Р

КП16(D1-D0) + tПУИР23=14+10=24нс,

Р

КП16(D1-D0) + tПУИР23=14+10=24нс,

tCLK =68нс

Время предварительной

установки следующего байта аргумента должно быть, отсчитываемым от

положительного фронта CLK, более чем 44нс (t![]() CLK) при сохранении

разности времени предварительной установки и следующего активного переноса по CLK более 24нс (tПУАРГ).

CLK) при сохранении

разности времени предварительной установки и следующего активного переноса по CLK более 24нс (tПУАРГ).

Описанным способом внешнее устройство за 4 такта сигнала CLK осуществляет последовательный ввод 32-ч разрядного аргумента побайтно.

После спада 4-го сигнала CLK внешнее устройство может сразу установить высокий уровень на линии STR и выдерживать его в течении от 1 до 4 тактов синхронизации управляющего автомата спец. Процессора, что соответствует времени от 103 до 412 нс.

После подачи сигнала STR внешнее устройство должно ожидать поступления положительного фронта по линии PONC.

По поступлению фронта сигнала DONE необходимо проверить состояние линии ERR: если ERR= «0», то сформированный результат верный.

Для выборки результата

сигнал RECENE должен быть установлен в «1» по фронту

сигнала DONE через время t3![]() Р КП12(ОЕ-D0)=16нс должна следовать серия из 4-х

импульсов по линии CLK со следующими параметрами:

Р КП12(ОЕ-D0)=16нс должна следовать серия из 4-х

импульсов по линии CLK со следующими параметрами:

- длительность импульса положительной полярности не менее, чем

tпол.п.= t3![]() Р

ТМ8(С-DO) + t3

Р

ТМ8(С-DO) + t3![]() Р КП12(А-DО) =17+21=38нс,

Р КП12(А-DО) =17+21=38нс,

- длительность импульса отрицательной полярности не менее, чем

t 0УD.СТМ8 + tВЫБАРГ =10+ tВЫБАРГ, где

t 0УD.СТМ8 - длительность импульса отрицательной полярности по выходу с триггера ТМ8;

tВЫБАРГ – время, необходимое на извлечение очередного байта результата по внешнему интерфейсу процессора

Выборка результата происходит побайтно младшими байтами вперед. Длина результата - 3 байта. Последний (четвертый) синхроимпульс CLK необходим для синхронизации внешнего устройства со спец.процессором.

По переднему фронту последнего импульса CLK внешнее устройство должно снять сигнал RECEIVE (перевести в «0»).

После спада последнего сигнала CLK процесс вычисления можно повторить, используя либо первый, либо второй регистры обмена.

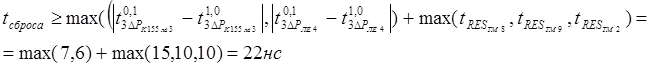

В таблицах 5.1 и 5.2 представлены электрические характеристики интерфейса спец. процессора, рассчитанные по разработанной принципиальной схеме.

Однако при сопряжении со внешними устройствами необходимо учитывать кроме Свх дополнительную монтажную емкость входов, определяемую конкретным способом монтажа.

Уважаемый посетитель!

Чтобы распечатать файл, скачайте его (в формате Word).

Ссылка на скачивание - внизу страницы.