Примечание: PIC16F8X игнорирует PCLATH<4:3> биты, которые используются для программной памяти страниц 1, 2 и 3 (0800h - 1FFFh). Использование PCLATH<4:3> как универсальных R/W бит не рекомендуется поскольку это может повлиять на совместимость с будущими продуктами.

Примечание: Нет инструкции загрузки/извлечения стека. Это происходят по выполнению ВЫЗОВА, ВОЗВРАТА, RETLW, и RETFIE команд, или векторизация в адресе прерывания.

Примечание: Нет битов статуса, чтобы указать переполнение стека .

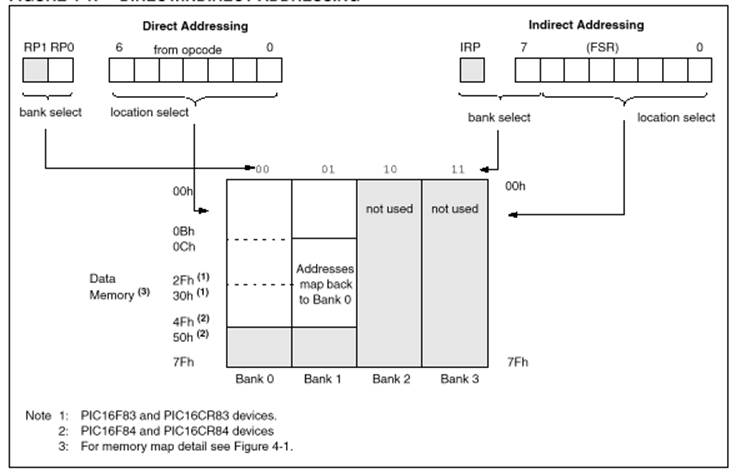

4.5 Косвенная Адресация;

INDF И FSR Регистрирует INDF регистр является не физический регистр. Адрес-ing INDF действительно адресует регистр, который чей адрес содержится в регистре FSR (FSR - указатель). Это - косвенная адресация.

ПРИМЕР 4-1: КОСВЕННАЯ АДРЕСАЦИЯ файл Регистра 05 содержит величину 10h файл Регистра 06 содержит величину 0Ah Загрузка величина 05 в регистр FSR чтение INDF регистра возвратит величину10h

Приращение величина регистра FSR один (FSR = 06)

Чтение INDF регистра теперь возвратит величину 0Ah.

Читая INDF сам косвенно (FSR = 0) произведет 00h. Запись в INDF косвенно результатах регистра в никаком-функционировании (хотя биты СТАТУСА могут были воздействованы на).

Простая программа, чтобы очистить позиции РАМ 20h-2Fh, использующие косвенную адресацию показывается в Примере 4-2.

ПРИМЕР 4-2: КАК ОЧИЩАТЬ ИСПОЛЬЗОВАНИЕ РАМ КОСВЕННОЙ АДРЕСАЦИИ

movlw 0x20 ;проинициализируйте указатель

movwf FSR; чтобы ЗАБИТЬ СЛЕДУЮЩИЙ

clrf INDF ;очистка INDF регистра

incf FSR ;указатель

inc btfss FSR,4 ;все сделанное?

goto ЗАТЕМ ;НИКАКОЕ, очистка затем ПРОДОЛЖАЕТ : ;ДА, продолжитесь

Эффективный 9-битовый адрес получается конкатенацией 8-битовый регистр FSR и битом IRP (STATUS<7>), как показано на Рисунке 4-1. Тем не менее, IRP не используется в PIC16F8X.

5.0 ПОРТЫ I/O

PIC16F8X Имеет два порта, PORTA и PORTB.

Некоторые контакты порта мультиплексные с изменением функций для других характеристик на устройстве.

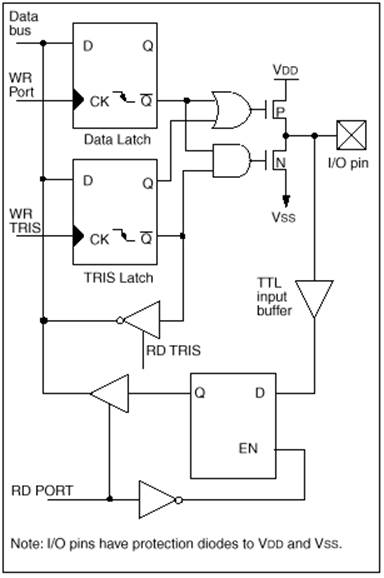

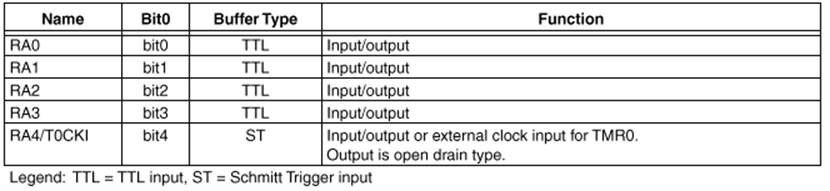

5.1 PORTA И TRISA

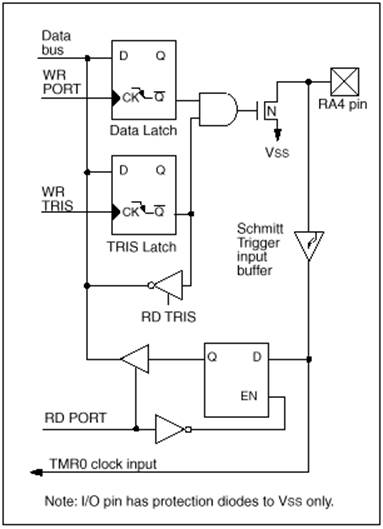

Регистры PORTA является 5-битными. RA4 - вход триггера Шмитта и выход открытой утечки. Все другие контакты порта RA позволяют вводить TTL уровни и выходные преобразователи CMOS. Все контакты имеют биты направления данных (TRIS регистры), которые могут сконфигурировать эти контакты как выход или вход.

Устанавливая TRISA бит (=1) соответствующий контакт PORTA становится входом. Очищая TRISA бит (=0) соответствующий контакт PORTA становится выходом.

При чтении PORTA регистра читает состояние контактов, поскольку запись в порт является записью на блокировку порта. Все операции записи чтение-модификация-запись. Так запись в порт подразумевает, что состояние контактов порта сначала читается, затем эта величина модифицируется и записывается на блокировку данных порта.

Штырек RA4 мультиплексный с входом часов TMR0.

ПРИМЕР 5-1: ИНИЦИАЛИЗАЦИЯ PORTA

CLRF PORTA ; Проинициализируйте PORTA

; установка выходной

; блокировки данных

BSF STATUS, RP0 ; Выберите Банк 1

MOVLW 0x0F ; Величина используется для

; инициализации направления

MOVWF TRISA ; Установите RA<3:0> как входы

; RA4 как выход

; TRISA<7:5> - всегда прочитается как '0’.

РИСУНОК 5-2: БЛОЧНАЯ ДИАГРАММА КОНТАКТОВ RA3:RA0

РИСУНОК 5-3: БЛОЧНАЯ ДИАГРАММА КОНТАКТОВ RA4

5.2 PORTB И TRISB

Регистры PORTB являются 8-битовым широким двунаправленным портом. Соответствующий регистр направления данных - TRISB. Если 1 на любом бите в TRISB регистре устанавливает соотвующий выходной драйвер в состояние высокого импеданса. Если 0 на любом бите в TRISB регистре устанавливает содержимое выходной блокировки на выбранном контакте.

Четыре контакта PORTB, RB7:RB4, имеют прерывание по изменению состояния. Только конфигурация контактов как входов может заставить это прерывание произойти (то есть, любой контакт RB7:RB4 сконфигурированный как выход исключается с прерывания по изменению состояния). Контакты оцениваются во входном режиме - по сравнению со значением, полученным на предыдущем чтении из порта. При несовпадении генерируется прерывание.

Уважаемый посетитель!

Чтобы распечатать файл, скачайте его (в формате Word).

Ссылка на скачивание - внизу страницы.