4.2.1 УНИВЕРСАЛЬНЫЙ РЕГИСТРОВЫЙ ФАЙЛ

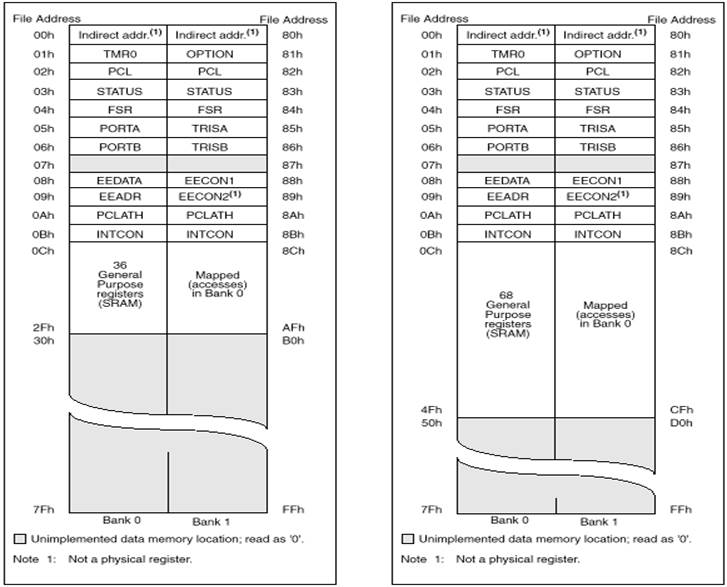

Все процессоры имеют некоторое количество Универсальных Регистров (GPR). Каждый GPR – шириной 8 битов и доступно или непосредственно или косвенно через FSR (Раздел 4.5).

Адреса GPR в банке 1 отображаются в адресах в банке 0. Как пример, при адресации 0Ch или 8Ch получаем доступ к тому же GPR.

4.2.2 СПЕЦИАЛЬНЫЕ РЕГИСТРЫ

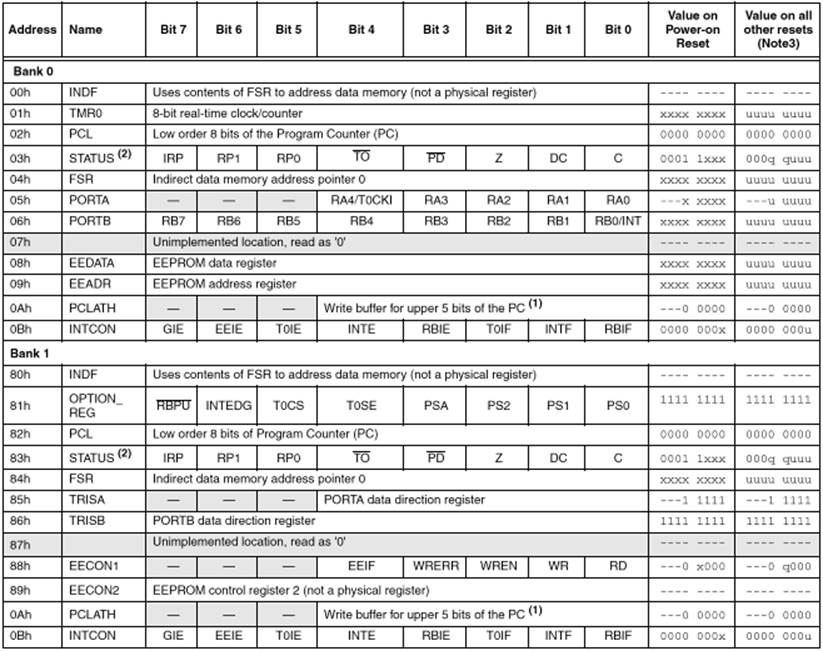

Специальные Регистры (Рисунок 4-1, Рисунок 4-2 и Таблица 4-1) используются CPU и периферийными функциями, чтобы управлять функционированием устройства. Эти регистры являются статическим РАМ.

Специальные регистры могут быть классифицированы в два набора, ядро и периферийное устройство. Связанные с функциями ядра описаны в этом разделе.

4.2.2.1 РЕГИСТР СТАТУСА

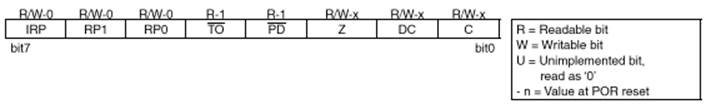

Регистр СТАТУСА содержит арифметический статус ALU, статус СБРОСА и бит банковского выбора для памяти данных. Как и любой регистр, регистр СТАТУСА может быть доступен для любой команды. Если регистр СТАТУСА доступен для команды, которая влияет на Z, DC или биты C, то запись на эти три бита недоступна. Эти биты устанавливаются или очищаются согласно логике устройства. Кроме того, недоступны и биты TO и PD. Следовательно, результат команды, использующей регистр СТАТУСА, может быть другим, чем предполагалось.

Например, CLRF СТАТУС очистит верхние три бита и установит бит Z. Эта команда оставит регистр СТАТУСА как 000u u1uu (где u = неизменный). Только BCF, BSF, SWAPF и MOVWF инструкции могут использоваться, чтобы изменить регистр СТАТУСА (Таблица 9-2) поскольку эти инструкции не влияют на любой бит статуса.

Примечание 1: IRP и RP1 биты (СОСТОЯНИЕ < 7:6) > не используются PIC16F8X и должен программироваться как сброшенные. Использование этих битов как битов общего назначения не рекомендуется, так как это может влиять cовместммость сверху вниз с будущими изделиями.

Примечание 2: C и DC биты используют как заем и цифровой заем разряда из бита, соответственно, в вычитании. См. SUBLW и SUBWF инструкции для примеров.

Примечание 3: Когда регистр СОСТОЯНИЯ используется для команды, которая воздействует на

Z, DC или биты C, запись в эти биты невозможна. Указанный бит (ы) будет модифицирован согласно логике процессора.

бит 7: IRP: бит Выбора Банка Регистра (использованное для косвенной адресации)

0 = Банк 0,1 (00h - FFh)

1 = Банк 2, 3 (100h - 1FFh)

Бит IRP не используется PIC16F8X. IRP должен быть сброшен.

бит 6-5: RP1:RP0: биты Выбора Банка Регистра (использованное для прямой адресации)

00 = Банк 0 (00h - 7Fh)

01 = Банк 1 (80h - FFh)

10 = Банк 2 (100h - 17Fh)

11 = Банк 3 (180h - 1FFh)

Каждый банк - 128 байтов. Только бит RP0 используется PIC16F8X. RP1 должен быть сброшен бит 4: ТО: бит Задержки

1 = После включения питания, команда CLRWDT , или SLEEP команда

0 = задержка WDT произошла бит 3: PD: Мощность-вниз по биту

1 = После включения питания или команды CLRWDT

0 = выполнением команды SLEEP

бита 2: Z: Нулевой бит

1 = Результат арифметической или логической операции - нуль

0 = результат арифметической или логической операции – не нуль бит 1: DC: Цифровой бит переноса/займа (для ADDWF и ADDLW команды ) (Для займа полярность возобновляется)

1 = перенос- с 4-го бита результата произошел

0 = переноса- с 4-го бита результата не было бита 0: C: бит Переноса/займа (для ADDWF и ADDLW инструкций)

1 = перенос из старшего значащего бита результата произошел

0 = перенос из старшего значащего бита результата произошел

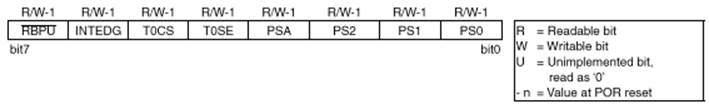

4.2.2.2 OPTION_REG РЕГИСТР

Регистр OPTION_REG является удобным регистром, который содержит различные управляющие биты, чтобы сконфигурировать TMR0/WDT, предварительный делитель частоты, внешнее прерывание INT, TMR0, и записью в PORTB.

Примечание:, когда предварительный делитель частоты присваивается WDT (PSA = '1'), TMR0 имеет 1:1 предварительное назначение делителя частоты.

Бит 7: RBPU: PORTB доступ

1 = PORTB закрыт

0 = PORTB открыт (индивидуальными значениями порта)

Уважаемый посетитель!

Чтобы распечатать файл, скачайте его (в формате Word).

Ссылка на скачивание - внизу страницы.