Хабаровский государственный технический университет

Методическое пособие к изучению курса

“Микропроцессорные системы”

для студентов специальности 220100

“Вычислительные машины, комплексы, системы и сети”

Хабаровск

2003

Фирма DEC выпускала в 80-е годы ЭВМ трех серий - ( LSI-11, PDP-11, Professional ) - системные блоки, клавиатуры и дисплеи которых разработаны на основе единых эргономических принципов. Архитектура ПЭВМ каждой серии определялась исходя из ее функционального назначения и требуемой производительности при приемлемых стоимости и габаритных размерах.

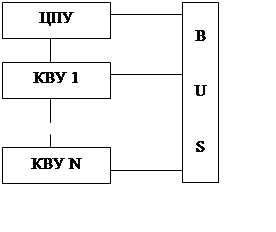

Общий вид архитектуры ЭВМ фирмы DEC представлен на рис.1.

|

ППР

ППР

Рис.1. Общий вид архитектуры ЭВМ фирмы DEC

1974 год:

Апрель:РDP-11/20,первая из семейства 16-битных машин.

PDP-11/20 - миникомпьютер,в котором все элементы системы-процессор,память и периферия-объединены единственной двунаправленной асинхронной шиной.UNIBUS позволила быстрым устройствам посылать,получать и обмениваться данными без промежуточного хранения в буфере.PDP-11 стала самой успешной серией миниЭВМ.

характеристики системного интерфейса UNIBUS

-число линий 56 - 60

-разрядность шины данных 16

-разрядность шины адреса 18 - 22

-число линий управления 22

-число уровней приоритета 5

-число подключаемых устройств до 18

-длина магистраи до 20 м

-время цикла 400 нс

-протокол - асинхроннвй

Структурная схема миниЭВМ PDP-11 (Q-bus)

к ппдO н к ппдI н к ппдO н к ппдI н

┌───────────────────────┐ ┌────────. . .────────────┐

│ ┌──────────┐ │ │ ┌───. . .──────┐ │

┌───────────┴───────┴───┐ ┌────┴────┴───┴────┴─┐ ┌───────────────────────┐

│ к ппрO н│ │к ппрI н к ппрO н│ . . . │к ппрI н к ппрO н │

│ центральный процессор │ │ модуль 1 │ . . . │ модуль N │

└╥─╥─┬─‑─┬─┬─┬─‑─‑─‑─┬─┬┘ └─────┬─‑─‑─‑─┬─┬─┬─‑─‑ └‑─‑─‑─┬─‑─‑─‑─┬─┬─┬─‑─‑┘

┌─┐ ║ ║ │ │ │ │ │ │ │ │ │ │ ║ ║ │ │ │ │ │ │ │ │ │ │ ║ ║ │ │ │ │ │ │ │ │ │ │ ┌─┐

│с╞══╪═╪═╪═╪═╪═╪═╪═╪═╪═╪═╪══╩═╬═╪═╪═╪═╪═╪═╪═╪═╪═╪═╪════════╩═╬═╪═╪═╪═╪═╪═╪═╪═╪═╪═╪═════╡с│к ад 00-15 н

│о╞════╪═╪═╪═╪═╪═╪═╪═╪═╪═╪════╩═╪═╪═╪═╪═╪═╪═╪═╪═╪═╪══════════╩═╪═╪═╪═╪═╪═╪═╪═╪═╪═╪═════╡о│к а 16-21 н

│г├──────┼─┼─┼─┼─┼─┼─┼─┼─┼──────┴─┼─┼─┼─┼─┼─┼─┼─┼─┼────────────┼─┼─┼─┼─┼─┼─┼─┼─┼─┼─────┤г│к сиа н

│л├───────┴─┼─┼─┼─┼─┼─┼─┼─┼─────────┼─┼─┼─┼─┼─┼─┼─┼─────────────┼─┼─┼─┼─┼─┼─┼─┼─┼─────┤л│к сип н

│а├──────────┼─┼─┼─┼─┼─┼─┼──────────┴─┼─┼─┼─┼─┼─┼─┼────────────────┴─┼─┼─┼─┼─┼─┼─┼─────┤с│к ввод н

│с├────────────┼─┼─┼─┼─┼─┼────── ─────┴─┼─┼─┼─┼─┼─┼──────────────────┴─┼─┼─┼─┼─┼─┼─────┤с│к вывод н

│о├──────────────┼─┼─┼─┼─┼──────────────┴─┼─┼─┼─┼─┼────────────────────┴─┼─┼─┼─┼─┼─────┤о│к байт н

│в├───────────────┴─┼─┼─┼─┼───────────────┼─┼─┼─┼─┼───────────────────────┼─┼─┼─┼─────┤в│к тпр н

│а├─────────────────┴─┼─┼─┼─────────────────┼─┼─┼─┼─────────────────────────┼─┼─┼─────┤а│к тпд н

│н├───────────────────┴─┼─┼───────────────────┼─┼─┼───────────────────────────┼─┼─────┤н│к пв н

│и├──────────────────────┼──────────────────────┴─┼────────────────────────────┴─┼─────┤и│к ву н

│е├───────────────────────────────────────────────┴──────────────────────────────┴─────┤е│к сброс н

│ │ │ │

└─┘

Характеристики системного интерфейса С-bus:

-число линий 46

-разрядность шины данных 16

-разрядность шины адреса 22

-шина данных и адреса - мультиплексируемые

-число линий управления 24

-число уровней приоритета 3

-число подключаемых устройств до 8

-длина магистраи до 0.5 м

-время цикла 500 нс

-протокол - асинхроннвй

Структурная схема ЭВМ VAX-11/780

┌────────────┬────────────┐

│акселератор │упарвляющее │

│операций │ЗУ │

│с ПЗ │пользователя│

┌──────────┼────────────┴────────────┤

│пультовая │ценральный ├───────┬───────┬────────────────────┬────────┐

│подсистема│процессор │память │память │многопортовая память│много- │

└──────────┼─────────────────────────┤512К-4М│256К-2М│для межсоединения │портовая│ │ │кеш-память │ │ │процессоров │память │ │ ├─────────────────────────┴───────┴───────┴────────────────────┴────────┤

│ адаптеры ввода/вывода │

└─────────────‑────────────────‑───────────────────‑────────────────────┘

║ ║ ║

║UNIBUS ║MASSBUS ║DR-780

║ ║ ║

ЭВМ VAX11 это 32-битовая машина которая может работать в двух режимах: в естественном и совместимом. Поскольку ЭВМ VAX11 - 32битовая машина , у нее возможно адресное пространство свыше 4Гбайт. В естественном режиме она может выполнять большой набор инструкций (включающий 248 основных инструкций) переменной длины. При установленной операционной системе ЭВМ VAX11 может быть мультипрограммной многопользовательской цифровой вычислительной системой реального времени.

У VAX11 есть два шинных адаптера: адаптер общей шины и адаптер массовой шины. При такой конфигурации все совместимые с общей шиной периферийные устройства могут быть прямо подключены к общей шине, тогда как высокоскоростные устройства массовой памяти могут подключаться к массовой шине через собственные контролеры.

В функции шинных адаптеров входят:

преобразование данных общей шины или массовой шины к формату, определяемому асинхронным соединителем на задней панели;

связь и управление взаимодействием между ЦП, памятью и устройствами на шине.

С помощью вторичной (дисковой) памяти, работающей под воздействием устройства управления памятью совместно с полупроводниковой (первичной) памятью, в системе VAX11 осуществляется механизм виртуальной памяти.

Микропроцессор J11(DCJ -11АС) является СБИС, выполняющей функции 16-разрядного процессора мини-компьютера PDP-11/70. Он состоит из двух комплементарных МОП--интегральных схем : кристалла обработки данных (КОД) и управляющего кристалла (УК)--контроллера последовательности микрокода.

Длительность цикла МП 200нс.

Микропроцессор содержит быстродействующие средства управления КЭШ-памятью, дополнительные системные регистры, функциональные средства управления памятью PDP-11 и полный набор инструкций для выполнения арифметических операций с плавающей точкой.

Микропроцессор превосходит по производительности все модели семейства PDP-11, в том числе модель 11/70,програмно совместим процессорами семейства на уровне макрокода и на уровне ОС.

В применяемый керамический корпус можно устанавливать до трех УК, которые вместе с КОД соединены с помощью двух 22-разрядных шин: микроинструкций и адресов и данных (ШАД) с временным уплотнением.

Микроинструкции, формируемые на УК, поступают на КОД по шине микроинструкций .После этого КОД выдает фактический адрес на ШАД. Устройство управления памятью обеспечивает адресацию 4 Мбайт физической памяти. Виртуальная память может быть расширена путем раздельного преобразования адресов для областей инструкций и данных.

Микропроцессор реализует полный набор инструкций и регистровую

Уважаемый посетитель!

Чтобы распечатать файл, скачайте его (в формате Word).

Ссылка на скачивание - внизу страницы.