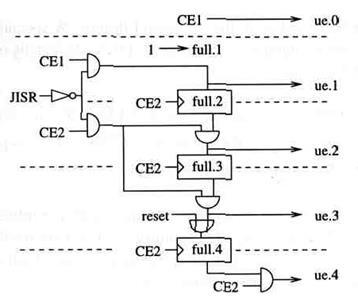

Рисунок 5.19 Механизм останова конструкции DLXП с поддержкой прерываний

Подобно конвейерной конструкции DLXπбез обработки прерываний, есть два сигнала синхронизации. Сигнал CE1 управляет верхними двумя этапами конвейера, а сигнал CE2 управляет остальными этапами.

CEl = (/busy /\ /dhaz) V (JISR /\ /Ibusy)

= (/busy /\ /dhaz) V (/JISR NOR Ibusy)

CE2 = /busy V (/JISR NOR Ibusy) V reset.

Оба синхросигнала неактивны, если одна из памятей занята; CEl также неактивен в случае опасностей данных. Однако, при JISR оба синхросигнала становятся активными как только память команд становится не занятой. Для немедленного отлавливания активного сигнала сброса, синхросигнал CE2 и синхросигнал CA4ceсхемы обработки причин должны быть активны при сбросе

CA4ce = ue.3 V reset.

Чтобы избежать ненужных остановов, флаги занятости рассматриваются только в случае успешного доступа к памяти. Так как блоки памяти никогда не устанавливают эти флаги, когда они простаивают, флаги занятости генерируются как

Ibusy = ibusy /\ (imal NOR ipf)

Dbusy = dbusy /\ (dmal NOR dpf)

/busy = Ibusy NOR Dbusy.

Механизм прерывания требует, чтобы стандартная запись в файл регистров или память отменялась при повторе прерывания. Файлы регистров GPR

и SPR защищены, как и в последовательной конструкции. Специальная запись в файл регистров SPR разрешается сигналом ue.4. Поэтому сигналы записи файлов регистров генерируются как

GPRw' = GPRw /\ ue.4 /\ (JISR NAND repeat)

SPRw' = SPRw /\ ue.4 /\ (JISR NAND repeat)

SPRw'[5 : 0] = SPRw[5 : 0] /\ ue.4.

Для памяти данных защита становится более сложной. Подобно последовательной конструкции DLX∑система памяти DM сама отменяет обновление, если она обнаруживает отсутствие страницы, и в случае отсутствия страницы при выборке сигнал запроса записи заблокирован в течение выполнения

Dmw.3 := Dmw.2 /\![]() .

.

Однако, доступ также должен быть заблокирован при JISR и при сбросе. Таким образом, сигнал Dmw3, который используется контроллером памяти DMC, чтобы генерировать сигналы записи в банк, устанавливается в

Dmw'.3 = Dmw.3 /\ full.3 /\ (JISR NOR reset).

Оставшиеся сигналы синхронизации и записи разрешаются как в конвейерной конструкции DLXπбез обработки прерываний: запрос чтения памяти данных предоставляется, если этап M полон

Dmr'.3 = Dmr.3 /\ full.3,

и обновление регистра R € out(i) разрешается ue.i

Rce' = Rce /\ ue.i.

Подобно конструкции DLX∑(лемма 5.8), из этого немедленно следует, что с этим механизмом останова активный сигнал сброса воспитывает конструкцию DLXП, не зависимо от того, в каком состоянии аппаратура была раньше:

|

Лемма 5.10 |

Пусть T – последний машинный цикл, в котором сигнал сброса активен. Тогда в следующем машинном цикле конструкция DLXП сигнализирует о сбросе и выполняет переход на ISR:

resetT = 1 /\ resetT+1 = 0 -> JISRT+1 = 1 и MCA[0]T+1 = 1.

Таблица 5.11 Начало выполнения после сброса исходя из предположения, что не произошли опасности данных. Пустое место указывает, что значение не определено.

|

T |

reset JISR |

ue[0, 1, 2, 3, 4] |

full[2, 3, 4] |

IF |

|

-1 |

1 |

1 |

||

|

0 |

0 1 |

10001 |

1 |

I0 |

|

1 |

0 0 |

11000 |

000 |

I1 |

|

2 |

0 0 |

11100 |

1 0 0 |

I2 |

|

3 |

0 0 |

11110 |

1 1 0 |

I3 |

|

4 |

0 0 |

11111 |

1 1 1 |

I4 |

Функция планирования

Уважаемый посетитель!

Чтобы распечатать файл, скачайте его (в формате Word).

Ссылка на скачивание - внизу страницы.