Санкт-Петербургский

Государственный Политехнический Университет

Санкт-Петербургский

Государственный Политехнический Университет

Факультет Технической Кибернетики

Кафедра Компьютерные Системы и Программные Технологии

ОТЧЕТ

о лабораторной работе №2.

Тема: Работа устройств на общей шине.

|

Выполнил студент |

гр. 3081/2 Туркин Е.А |

|

Преподаватель |

Максименко С.Л. |

Санкт-Петербург

2010 г.

Часть 1. Исследование трехстабильных буферов и шинных формирователей.

Выполнение работы:

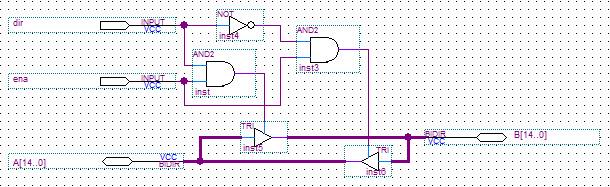

Схема шинного формирователя представлена на Рис. 1.

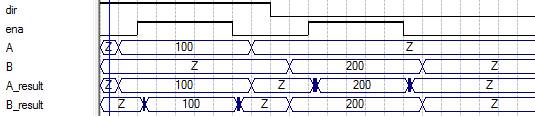

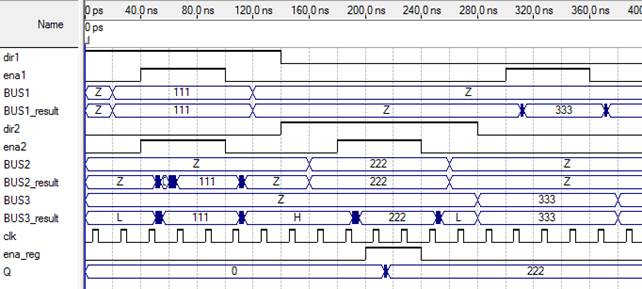

Осуществим попеременную передачу данных в двух направлениях, обеспечив отсутствие конфликтов на шинных преобразователях. Диаграмма работы представлена на Рис. 2.

Данные на шине приёмнике появляются с запаздыванием T ≈ 12нс.

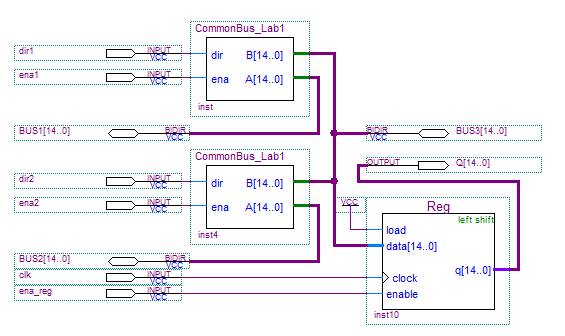

Устройство состоит из двух шинных формирователей и регистра. Схема устройства представлена на Рис. 3. Сигналы ena1, ena2 и ena_reg разрешают работу двух формирователей и регистра соответственно. Сигналы dir1 и dir2 управляют направлением передачи информации. Если dir*=1, то информация выводится с шины BUS* на общую шину, если dir*=0, то информация считывается с шины общей шины на шину BUS*.

Диаграмма передачи представлена на рис. 4.

Для передачи данных по общей шине без конфликтов необходимо устанавливать сигналы в следующей последовательности: установка направления, установка данных, разрешение работы. Для изменения направления или завершения работы сигналы убираются в обратном порядке

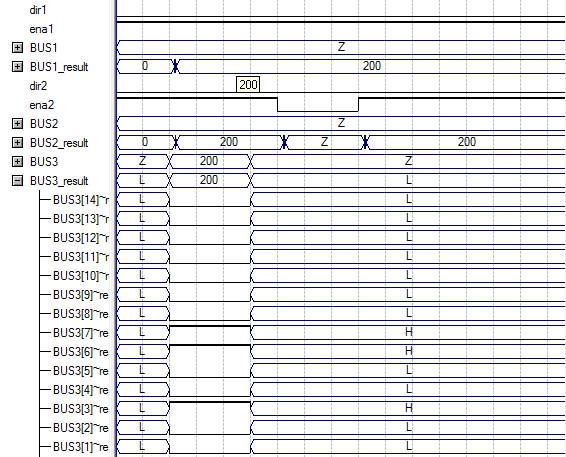

Выполним назначения:

Enable Bus-Hold Circuitry для выводов bus3[n-1..0];

Weak Pull_Up Resistor для выводов bus2[n-1..0].

И вновь смоделируем работу устройства передачи данных. Результат моделирования представлен на Рис. 7.

На рисунке видно, что после снятия сигнала с шины BUS3, состояние каждой линии переходит из жесткого сигнала в мягкий сигнал, благодаря чему результат на шине BUS2 и BUS1 не изменяется. Weak Pull_Up Resistor действует только при программировании платы.

Часть 2. Исследование обмена с внешней статической памятью, имеющей трёхстабильную шину данных.

Выполнение работы:

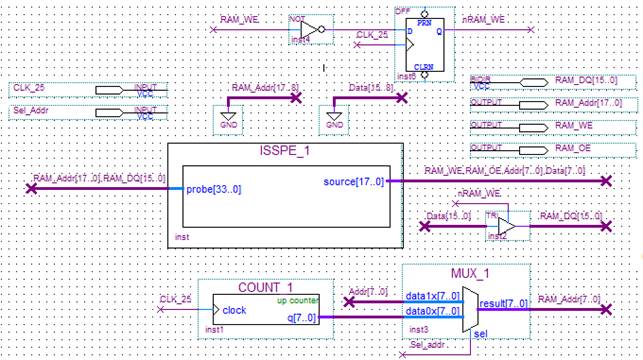

Схема устройства представлена на Рис. 8.

На управляющий вход буфера TRI подаётся сигнал nRAM_WE с задержкой в один такт.

С помощью логического анализатора можно наблюдать последовательность байт в ASCII-коде, задав за источник адресов выход со счётчика COUNT 1 (Рис. 9).

Уважаемый посетитель!

Чтобы распечатать файл, скачайте его (в формате Word).

Ссылка на скачивание - внизу страницы.