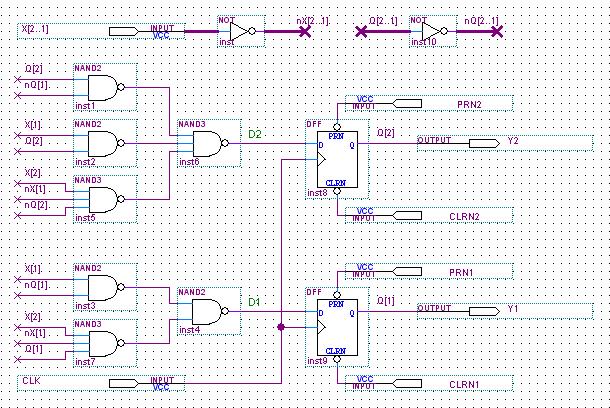

Составим принципиальную схему КА и проведём исследование на СБИС EP2C8F256C-8 в пакете Quartus II.

Рис. 1. Схема КА в пакете Quartus II.

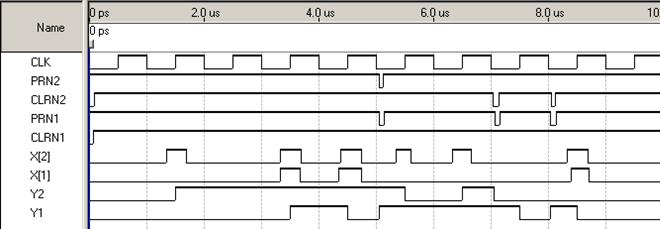

Составим тест для проверки переходов и выходов для всех состояний КА.

Рис. 2. Временная диаграмма работы КА.

|

Установка КА R0 ; На вход е - 00; 0 à 0; На выходе - 00 |

На вход е - 10; 0 à 1; На выходе - 10 |

На вход е - 00; 1 à 1; На выходе - 10 |

На вход е - 11; 1 à 2; На выходе - 11 |

На вход е - 11; 2 à 1; На выходе - 10 |

Установка КА R2 ; На вход е - 10; 2 à 3; На выходе - 01 |

На вход е - 10; 3 à 2; На выходе - 11 |

Установка КА R3 ; На вход е - 00; 3 à 0; На выходе - 00 |

Установка КА R3 ; На вход е - 11; 3 à 0; На выходе - 00 |

Все переходы осуществляются верно.

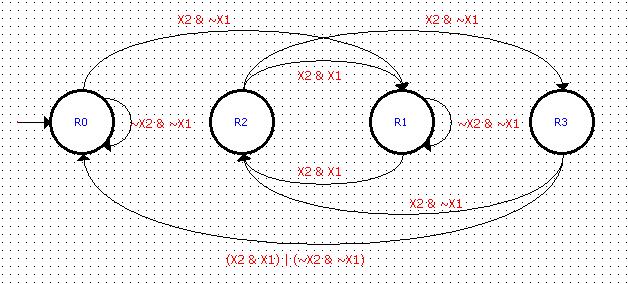

Рис. 3. Граф-схема КА, построенная средствами Quartus II.

Выполним генерацию VHDL кода.

Листинг файла «Lab4_SM.vhd»

|

LIBRARY ieee; |

|

USE ieee.std_logic_1164.all; |

|

ENTITY Lab4_SM IS |

|

PORT ( |

|

clock : IN STD_LOGIC; |

|

reset : IN STD_LOGIC := '0'; |

|

X1 : IN STD_LOGIC := '0'; |

|

X2 : IN STD_LOGIC := '0'; |

|

Y1 : OUT STD_LOGIC; |

|

Y2 : OUT STD_LOGIC |

|

); |

|

END Lab4_SM; |

|

ARCHITECTURE BEHAVIOR OF Lab4_SM IS |

|

TYPE type_fstate IS (R0,R1,R2,R3); |

|

SIGNAL fstate : type_fstate; |

|

SIGNAL reg_fstate : type_fstate; |

|

SIGNAL reg_Y1 : STD_LOGIC := '0'; |

|

SIGNAL reg_Y2 : STD_LOGIC := '0'; |

|

BEGIN |

|

PROCESS (clock,reg_fstate) |

|

BEGIN |

|

IF (clock='1' AND clock'event) THEN |

|

fstate <= reg_fstate; |

|

END IF; |

|

END PROCESS; |

|

PROCESS (fstate,reset,X1,X2,reg_Y1,reg_Y2) |

|

BEGIN |

|

IF (reset='1') THEN |

|

reg_fstate <= R0; |

|

reg_Y1 <= '0'; |

|

reg_Y2 <= '0'; |

|

Y1 <= '0'; |

|

Y2 <= '0'; |

|

ELSE |

|

reg_Y1 <= '0'; |

|

reg_Y2 <= '0'; |

|

Y1 <= '0'; |

|

Y2 <= '0'; |

|

CASE fstate IS |

|

WHEN R0 => |

|

IF (((X2 = '1') AND NOT((X1 = '1')))) THEN |

|

reg_fstate <= R1; |

|

ELSIF ((NOT((X2 = '1')) AND NOT((X1 = '1')))) THEN |

|

reg_fstate <= R0; |

|

-- Inserting 'else' block to prevent latch inference |

|

ELSE |

|

reg_fstate <= R0; |

|

END IF; |

|

reg_Y1 <= '0'; |

|

reg_Y2 <= '0'; |

|

WHEN R1 => |

|

IF ((NOT((X2 = '1')) AND NOT((X1 = '1')))) THEN |

|

reg_fstate <= R1; |

|

ELSIF (((X2 = '1') AND (X1 = '1'))) THEN |

|

reg_fstate <= R2; |

|

-- Inserting 'else' block to prevent latch inference |

|

ELSE |

|

reg_fstate <= R1; |

|

END IF; |

|

reg_Y1 <= '0'; |

|

reg_Y2 <= '1'; |

|

WHEN R2 => |

|

IF (((X2 = '1') AND (X1 = '1'))) THEN |

|

reg_fstate <= R1; |

|

ELSIF (((X2 = '1') AND NOT((X1 = '1')))) THEN |

|

reg_fstate <= R3; |

|

-- Inserting 'else' block to prevent latch inference |

|

ELSE |

|

reg_fstate <= R2; |

|

END IF; |

|

reg_Y1 <= '1'; |

|

reg_Y2 <= '1'; |

|

WHEN R3 => |

|

IF (((X2 = '1') AND NOT((X1 = '1')))) THEN |

|

reg_fstate <= R2; |

|

ELSIF ((((X2 = '1') AND (X1 = '1')) OR (NOT((X2 = '1')) AND NOT((X1 = '1'))))) THEN |

|

reg_fstate <= R0; |

|

-- Inserting 'else' block to prevent latch inference |

|

ELSE |

|

reg_fstate <= R3; |

|

END IF; |

|

reg_Y1 <= '1'; |

|

reg_Y2 <= '0'; |

|

WHEN OTHERS => |

|

reg_Y1 <= 'X'; |

|

reg_Y2 <= 'X'; |

|

report "Reach undefined state"; |

|

END CASE; |

|

Y1 <= reg_Y1; |

|

Y2 <= reg_Y2; |

|

END IF; |

|

END PROCESS; |

|

END BEHAVIOR; |

Уважаемый посетитель!

Чтобы распечатать файл, скачайте его (в формате Word).

Ссылка на скачивание - внизу страницы.