В Assignments Editor выполним следующие назначения:

· Enable Bus-Hold Circuitry для выводов bus3[n-1..0]

· Weak Pull_Up Resistor для выводов bus2[n-1..0]

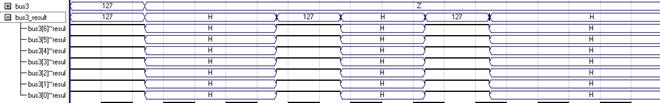

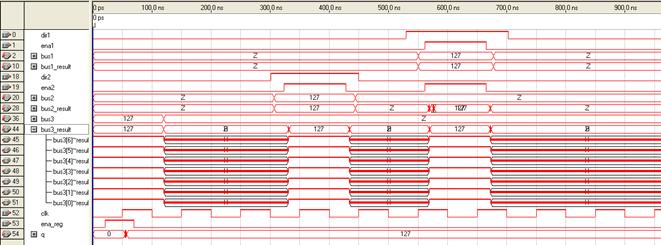

Рис 5. Результат моделирования и сравнение с предыдущим

Enable Bus-Hold Circuitry – шинный фиксатор уровня: когда шина переходит в Z-состояние, шинный фиксатор удерживает ее в предыдущем состоянии. Weak Pull_Up Resistor — подтягивание шины резисторами к источнику питания: при переходе в плавающее состояние на шине устанавливается сигнал высокого уровня (действует только при программировании платы).

3. Исследование обмена с внешней статической памятью, имеющей трехстабильную шину данных

Необходимо организовать управление памятью для записи и считывания данных из нее. Запись осуществляется с использованием редактора In-SystemSourcesandProbesEditor (ISSPE), задающего адреса, данные и управляющие сигналы при записи в память. Чтение осуществляется перебором адресов с помощью счетчика.

Рис 6. Устройство для исследования обмена с внешней памятью

RAM_Addr[17..0] – шина адреса

RAM_DQ[15..0] – двунаправленная трехстабильная шина данных

RAM_WE (запись, активный уровень 0), RAM_OE (разрешение вывода данных из памяти на шину данных) – сигналы управления шиной данных

Таблица: Режимы работы памяти

|

OE |

WE |

DQ[15..0] |

Режим |

|

0 |

1 |

DATA out |

Чтение слова |

|

х |

0 |

DATA in |

Запись слова |

|

1 |

1 |

High Z |

Выходы памяти в Z - состоянии |

Чтение слова: трехстабильный буфер должен находиться в выключенном состоянии, сигнал управления буфером имеет низкий уровень. Запись слова: буфер открыт, сигнал управления имеет высокий уровень.

Для управления трехстабильным буфером используется сигнал nRAM_WE с задержкой, чтобы сначала установился адрес страницы, а уже потом производилось чтение или запись.

С помощью логического

анализатора можно наблюдать последовательность байт в ASCII-коде, задав за

источник адресов выход со счётчика.

С помощью логического

анализатора можно наблюдать последовательность байт в ASCII-коде, задав за

источник адресов выход со счётчика.

Рис 7. Чтение данных из памяти в окне Signal Tap II

Уважаемый посетитель!

Чтобы распечатать файл, скачайте его (в формате Word).

Ссылка на скачивание - внизу страницы.