також не має обмежень, а для ТТЛ обмеження задається потужністю джерел сигналів xo та x1.

Схема рис.3.3.в каскадного розмноження кількості виходів фактично не має ніяких обмежень і використовується в схемах при розводці кіл синхронізації.

Приклад 4. Використовуючи елементи ТТЛ.IC. розробити схему I на 9 входів.

![]()

![]() В серіях ТТЛ. використовуються багатовходові

елементи I 4(2I), 3(3I), 2(4I), а також елементи I-НІ

- 2(4I-HI),

1(8I-HI), 3(3I-HI), 12(I-HI).

В серіях ТТЛ. використовуються багатовходові

елементи I 4(2I), 3(3I), 2(4I), а також елементи I-НІ

- 2(4I-HI),

1(8I-HI), 3(3I-HI), 12(I-HI).

При використанні елементів 3(3I) ( K555ЛI-3) використовується каскадне з’єднання елементів.

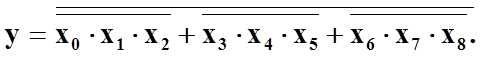

перетворимо до виду:

(3.3)

(3.3)

З (3.3.) витікає, що необхідна схема може бути створена на базі мікросхеми 3(3I-HI), (K155ЛA4), виходи яких об’єднуються елементом 3(АБО-HI) (K155ЛE4).

Приклад 5. Використовуючи елементи ТТЛ IC, розробити схему на 9 входів АБО.

В серіях ТТЛ використовуються мікросхеми 4(2АБО-HI), 2( 5АБО-HI), 3(3АБО-HI).

перетворимо до виду:

(3.4)

Функція (3.4.) реалізується шляхом використання трьох 3АБО-HI (мікросхема К155ЛЕ4), виходи яких об’єднуються одним елементом 3I-HI (K155ЛА4).

Приклад 6. Побудувати схему знаходження суми по модулю 2 на вісім входів, використовуючи двохвходовий елемент ТТЛ.

В серіях ТТЛ використовується мікросхема з двома входами з позначенням ЛП5 та ЛЛ3 ( вихід останньої з відкритим колетором ). Ці мікросхеми мають логіку

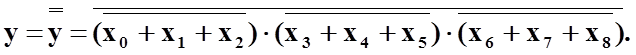

Необхідна логічна функція має вигляд:

![]()

( 3.5.)

Для побудови схеми, що реалізує функцію (3.5.) скористаємось сполучним законом, завдяки якому виконаємо два варіанти перетворень

![]()

( 3.6.)

![]()

( 3.7.)

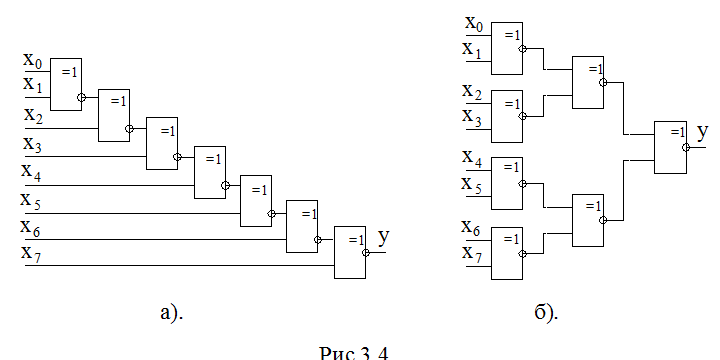

Формула (3.6.) дає можливість створити послідовну схему (рис.3.4.a); (3.7.)- відповідно, пірамідальну (рис.3.4.б).

|

використанням двох

корпусів, наприклад, мікросхеми К555ЛП5. Але

величини часових затримок в них суттєво різні.![]()

|

|

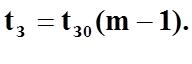

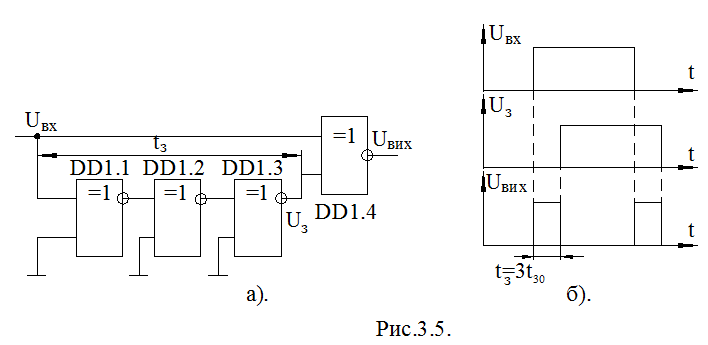

Елементи DD1.1 – DD1.3 виконують затримку імпульса Uвх на величину t3 =3t3o , а DD1.4. виділяє імпульси Uвих відповідно до логіки роботи елемента

Схема приведена на рис.3.4.б. являється основою схем, призначених для перевірки на парність багаторозрядних цифрових слів (наприклад мікросхеми К155IП2 та К561СAI), які широко використовуються в комп’ютерній техніці.

Генератори імпульсів. Одним з напрямків широкого використання

базових елементів цифрової схемотехніки являється побудова генераторів

імпульсних послідовностей, а також перетворювачів імпульсів різного

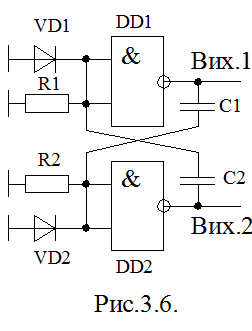

призначення. Рис.3.6. ілюструє один з варіантів побудови

автогенератора імпульсних послідовностей (мультивібратора). Приведена

схема називається симетричним мульти-вібратором. Робота її полягає в

слідуючому. Припустимо, що

на виході DD1

присутній високий потенціал. Тоді на його вході повинен бути нульо-вий

сигнал, а це значить, що через резистор R1 або зовсім не протікає струм, або його величина

на-стільки не значна, що падіння напруги на R1 від його протікання менше порогового рівня DD1. При

використанні КМОП IC вхідний струм мікросхеми можна вважати

нульовим. Це значить, що в колі-Вих2 DD2, C2, R1,

загальна шина -струм не протікає.

Генератори імпульсів. Одним з напрямків широкого використання

базових елементів цифрової схемотехніки являється побудова генераторів

імпульсних послідовностей, а також перетворювачів імпульсів різного

призначення. Рис.3.6. ілюструє один з варіантів побудови

автогенератора імпульсних послідовностей (мультивібратора). Приведена

схема називається симетричним мульти-вібратором. Робота її полягає в

слідуючому. Припустимо, що

на виході DD1

присутній високий потенціал. Тоді на його вході повинен бути нульо-вий

сигнал, а це значить, що через резистор R1 або зовсім не протікає струм, або його величина

на-стільки не значна, що падіння напруги на R1 від його протікання менше порогового рівня DD1. При

використанні КМОП IC вхідний струм мікросхеми можна вважати

нульовим. Це значить, що в колі-Вих2 DD2, C2, R1,

загальна шина -струм не протікає.

Відсутність струму в приведеному колі можливе лише при низькому потенціалі виходу Вих2, що в свій час забезпечується тим, що падіння напруги на R2 відповідає рівню логічної 1. Тобто ми дійшли до того, що при Uвих.1=1 в колі- Вих1, C1, R2 загальна шина- протікає струм заряду конденсатора

Уважаемый посетитель!

Чтобы распечатать файл, скачайте его (в формате Word).

Ссылка на скачивание - внизу страницы.