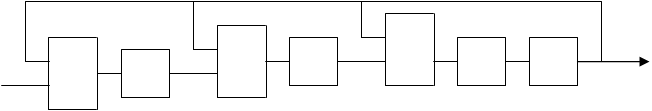

Схема декодера будет более сложная, чем схема кодера, так как он должен не только делить многочлены, но и исправлять ошибки в них. Поэтому декодер будет состоять из двух соединенных последовательно частей. Схема второй части, делящей принятый многочлен на порождающий, приведена на рисунке 3.10.

|

М2 М2 выход

Вход М2 1 2 3 4

Р е г и с т р с д в и г а

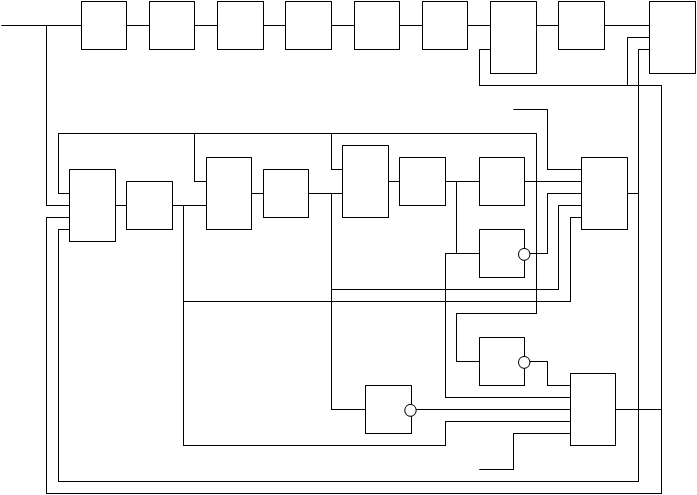

Первая часть декодера должна корректировать ошибки в принятом сообщении. В ее основе лежит схема, идентичная второй части декодера. К ней добавлен сдвиговый регистр, в который заносится принимаемое сообщение. Схема первой части декодера показана на рисунке 3.11. Признаком наличия ошибки является ненулевой остаток в регистре RG2.

Рассмотрим работу декодера на примере. Пусть передается сообщение А(х)=101=х2+1. После умножения на g(х) получим код F(х)=1001011=х6+х3+х+1. Предположим, что сигнал был передан правильно и на декодер поступил без ошибок. Тогда после семи тактовых импульсов в регистре RG2 будет код 0000, а в регистре RG1 - принятый код. После следующих семи импульсов код с регистра RG1 поступит на вторую часть декодера, с выхода которого мы получим переданное сообщение 101.

Теперь предположим, что код был передан с ошибкой в старшем бите: F`(х)=0001011. Тогда после семи импульсов в регистре RG2 будет ненулевой остаток х3+х+1=1011, а на выходе опознавателя №1 будет единица. Благодаря сумматору она повлияет в следующем такте на значение старшего бита, хранимого в регистре RG1. Остальные биты изменены не будут. Далее уже исправленная комбинация поступает на вторую часть декодера, где мы получаем переданное значение.

Если бы ошибка была в другом бите, то и остаток в RG2 конечно был бы другой. Но особенность циклического кода в том, что через несколько тактов мы обязательно получим код 1011. За эти несколько тактов содержимое регистра RG1 сдвинется и неверный бит будет в его старшем разряде. То есть, он будет исправлен.

Р е г и с т р с д в и г а RG1

|

Р е г и с т р с д в и г а RG2 ТИ

Опозн. 1

М2 М2 3 4 &

М2 1 2

1

1 Опозн. 2

1 &

ТИ

Рисунок 3.11 – Первая часть схемы декодера.

Теперь предположим, что принятое сообщение имеет ошибки в двух старших битах: А` (х)=0101011=х5+х3+х+1. Тогда остаток в регистре RG2 снова будет ненулевой:

![]()

![]() х5+х3+х+1

х4+х2+х+1

х5+х3+х+1

х4+х2+х+1

![]() х5+х3+х2+х х

х5+х3+х2+х х

х2+1

х2+1=0101

При таком остатке сработает опознаватель №2 и в следующем такте будут исправлены биты х6 и х5, находящиеся в ячейках 6 и 7 регистра RG1. При других комбинациях смежных ошибок мы будем получать остатки, которые через соответствующее число тактов перейдут в код х2+1=0101. Порядок такого перехода для ошибки вида 0001100 приведен в таблице 3.

Уважаемый посетитель!

Чтобы распечатать файл, скачайте его (в формате Word).

Ссылка на скачивание - внизу страницы.