3) Сигнал Y3 (длительность 160 мкс.)

DW3=160*2=320

4) Тактовая частота для ПСА (65.5 кГц)

DW4=2*106/62500=32

5) Сигнал Y5 (30 мкс., пауза, 30 мкс.)

DW5=2*106*60*10-6=120=78h

6) Сигнал 2 Гц (аварийный датчик)

DW6=62500/2=31250=7A12h

Для разработки запоминающего устройства (ПЗУ и ОЗУ) будем использовать следующие микросхемы, представленные в таблице 1.

Таблица 2

|

Характеристика |

ПЗУ |

ОЗУ |

|

Ёмкость |

1K |

1K |

|

Организация БИС |

1К x 8 |

1024 x 4 |

|

Входы выборки кристалла |

CS |

CS |

|

Тип БИС |

К573РФ1 |

К541РУ2 |

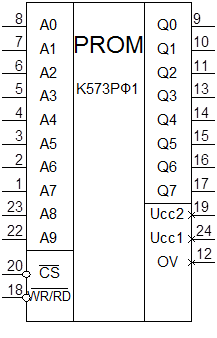

ПЗУ реализовано на одной микросхеме PROM К573РФ1 (рисунок 7), по 1Кбит х

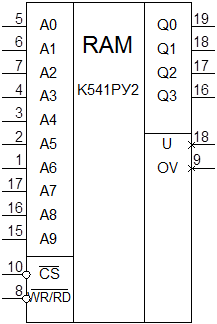

8 каждая. ОЗУ составляют 2 микросхемы RAM К541РУ2, представленные на рисунке 6,

по 1024бит х 4 каждая. Наращивание ёмкости ОЗУ осуществлялось вертикально, т.

е. увеличение разрядности до 8 бит

ПЗУ реализовано на одной микросхеме PROM К573РФ1 (рисунок 7), по 1Кбит х

8 каждая. ОЗУ составляют 2 микросхемы RAM К541РУ2, представленные на рисунке 6,

по 1024бит х 4 каждая. Наращивание ёмкости ОЗУ осуществлялось вертикально, т.

е. увеличение разрядности до 8 бит![]() . Характеристика БИС К573РФ1. Время

выборки адреса не более 500 нс; время хранения информации при включенных или

выключенных источниках питания не менее 15000 ч; число циклов

перепрограммирования не менее 25 (при t = +250C); напряжения питания UCC1 = 5В±5%, UCC2 = 12В±5%, UPR = 5В (в режиме считывания); суммарная

потребляемая мощность: в режиме считывания не менее 700 мВт, в режиме хранения

не менее 200 мВт; диапазон температур: -10 ¸ +700C;

тип корпуса металлокерамический (2121.28-8) с прозрачной для ультрафиолетовых

лучей крышкой.

. Характеристика БИС К573РФ1. Время

выборки адреса не более 500 нс; время хранения информации при включенных или

выключенных источниках питания не менее 15000 ч; число циклов

перепрограммирования не менее 25 (при t = +250C); напряжения питания UCC1 = 5В±5%, UCC2 = 12В±5%, UPR = 5В (в режиме считывания); суммарная

потребляемая мощность: в режиме считывания не менее 700 мВт, в режиме хранения

не менее 200 мВт; диапазон температур: -10 ¸ +700C;

тип корпуса металлокерамический (2121.28-8) с прозрачной для ультрафиолетовых

лучей крышкой.

Таблица 3. Карта памяти.

|

Адрес |

Размер |

Тип памяти |

|

0000-0125h |

293 |

Основная программа |

|

0130-014Eh |

30 |

Программа умножения |

|

0200-0220h |

32 |

Таблица прерываний |

|

03FDh |

1 |

Константа Q |

|

03FEh |

1 |

Константа a1 |

|

03FFh |

1 |

Константа a0 |

|

0400-07FFh |

1K |

ОЗУ |

Подсистема ввода-вывода включает в себя блоки ИУВВ и ИУВЫВ. Через эти блоки осуществляется обмен цифровой и аналоговой информацией. Для этого блоки ИУВВ и ИУВЫВ имеют два адаптера КР580ВВ55А, через разряды которых, осуществляется прием информации и управление выдачей управляющих воздействий.

Обмен аналоговой информацией в блоках ИУВВ и ИУВЫВ осуществляется с помощью БИС К1108ПВ1 (АЦП), К572ПА2 (ЦАП).

Управление АЦП и ЦАП, а также чтение и запись цифровой информации в них осуществляется с помощью каналов БИС КР580ВВ55А. На аналоговых выходах ЦАП установлен ОУ К140УД7.

Коммутация аналоговых сигналов осуществляется БИС К590КН1. Для управления коммутатором используются 2 младших бита порта С параллельного программируемого адаптера ППА2.

Канал В ППА1, настроеный на ввод информации, используется для приема сигналов с датчиков Х1,Х2,X3,X4.

Распределение адресного пространства устройств ввода-вывода осуществляется с помощью дешифратора К155ИД7. В данном курсовом проекте предусмотрено обращение к портам при помощи команд чтения/записи (IN /OUT) .

Для дешифрации адресов будет использована микросхема дешифратора К155ИД7.

Таблица 4 – Порты ввода/вывода

|

Порт |

Устройство |

|

E8h |

ППА1 КР580ВВ55А |

|

ECh |

ППА2 КР580ВВ55А |

|

F0h |

КПП КР580ВН59 |

|

F4h |

ПИТ1 КР580ВИ53 |

|

F8h |

ПИТ2 КР580ВИ53 |

|

FCh |

ПСА КР580ВВ51А |

![]()

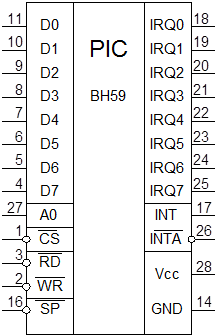

Запросы на

прерывание обслуживаются при помощи контроллера приоритетов прерываний (КПП)

КР580ВН59 представленной на рисунке 7. Возникающие прерывания вызывают

соответствующие подпрограммы их обработки (по таблице прерываний), что

обуславливает реакцию МПС на изменение внешней обстановки. При начальной

инициализации процессора контроллер необходимо переинициализировать заново.

Запросы на

прерывание обслуживаются при помощи контроллера приоритетов прерываний (КПП)

КР580ВН59 представленной на рисунке 7. Возникающие прерывания вызывают

соответствующие подпрограммы их обработки (по таблице прерываний), что

обуславливает реакцию МПС на изменение внешней обстановки. При начальной

инициализации процессора контроллер необходимо переинициализировать заново.

Запросом на прерывание от связного адаптера является сигнал готовности приёмника.

Таблица векторов прерываний располагается под адресом 0200h.

Таблица 5 – Таблица векторов прерываний

Уважаемый посетитель!

Чтобы распечатать файл, скачайте его (в формате Word).

Ссылка на скачивание - внизу страницы.