Каждый вычислительный канал обязан обрабатывать поступающую на него аналоговую и цифровую информацию, вырабатывать выходные воздействия и обрабатывать запросы на прерывания [1]. С АЦП микропроцессор получает три сигнала N1, N2 и N3. Эти сигналы представляют собой цифровую обработку аналоговых сигналов V1, V2 и V3, поступающих на АЦП через коммутатор КН3.

Получив эти сигналы ВЕ51 начинает обработку функции max(N1;N2+K), где К – есть 8-битный код уставки хранящийся в памяти. В памяти так же храниться 8-битная константа Q, с которой сравнивается результат функции. В зависимости от результатов сравнения МПС вырабатывает сигналы Y2=40мкс и Y3=20мкс. МПС вырабатывает сигнал Y4=a0+a1*N3, где а0 и а1 – 8-разрядные коэффициенты, хранящиеся в памяти. Сигнал Y4 поступает через ЦАП на объект управления как управляющее воздействие [1].

Со выходов объекта управления МПС получает битовые сигналы X1-X4 и формирует входную битовую функцию: __ __ __

Y1=X1![]() X2VX3VX4

X2VX3VX4

Эта функция в дальнейшем является контрольной функцией проверки правильности работы вычислительных каналов.

Для обработки всех этих сигналов, а так же для подключения ОЗУ и ПЗУ недостаточно четырех имеющихся портов ВЕ51. Для увеличения количества портов применим портовые регистры ВР43. Подробный принцип работы и подключения описан в [3]. Эти регистры позволяют получить 4 4-битных двунаправленных порта, взяв на входе 6 линий исходного порта. Таким образом, заняв 2 порта ВЕ51, получим 6 8-битных портов. Объединение линий программирования регистров ВР43.2 и ВР43.3 позволяет сэкономить 2 линии исходного порта ВЕ51. На программную реализацию это никак не скажется.

В качестве генератора частоты выберем кварцевый резонатор на 12МГц [5]. Таким образом время одного машинного цикла – 1мкс. Принципиальная схема вычислительного канала приведена в приложении 1. Функциональная схема приведена на рисунке 3.

Рисунок 3 – Функциональная схема вычислительного канала

2.4 Разработка схемы сравнения

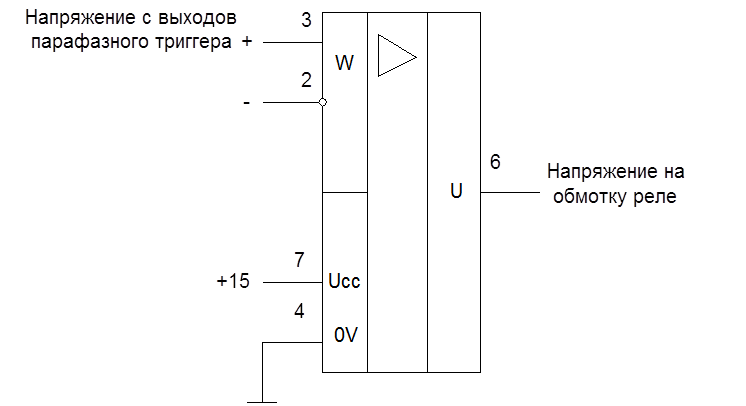

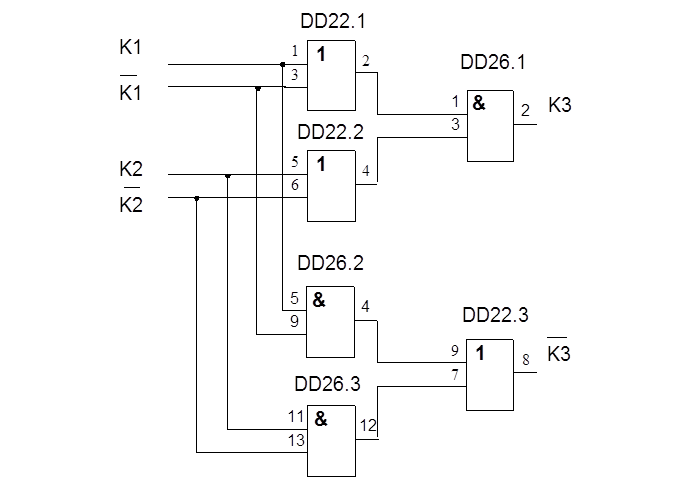

Исходя из задания, необходимо сравнивать результаты работы основного и вспомогательного вычислительных каналов. Для этого сравниваются сигналы Y1 и их инверсии, выработанные обоими каналами. Схема сравнения состоит из каскада понижения разрядности сравниваемого кода [3] и парафазного триггера. В схеме сравнения реле Р подключается через усилитель (ОУ) К140УД708. Принципиальная схема усилителя приведена на рисунке 4. Принципиальная схема парафазного триггера (ПТ) приведена на рисунке 5. Каскад понижения разрядности нужен для преобразования четырех сигналов с выходов вычислительных каналов в два сигнала поступающие на парафазный триггер. Схема работает следующим образом: при поступлении на входы каскада сигналов K1 и K2 как это показано на рисунке 6, на выходе будет сигнал K3 и его инверсия. Как только происходит ошибочное поступление на вход, на выходе сигналы будут синфазными.

|

Рисунок 4 - Усилитель

Рисунок 5 - Парафазный триггер

|

Рисунок 6 – Каскад понижения разрядности (2/4)

К выводам парафазного триггера через усилитель подключается реле Р. При возникновении ошибки на входы схемы сравнения пройдет запрещенная комбинация сигналов. Это приведет парафазный триггер в состояние ошибки, при котором он защелкнется и потенциалы его выходов сравняются. Вследствие этого прекратится подача питания на обмотку реле Р и якорь реле разомкнув фронтовые контакты замкнет тыловые. Через тыловые контакты организована цепь аварийной сигнализации, которая сработает немедленно после отключения питания реле Р. Таким образом можно отработать аварийные сигналы по отказу источника питания и аварийного датчика. Это избавляет нас от программного решения этой проблемы. Схема устройства сравнения приведена на рисунке 7.

Рисунок 7 - Схема сравнения работы вычислительных каналов

Уважаемый посетитель!

Чтобы распечатать файл, скачайте его (в формате Word).

Ссылка на скачивание - внизу страницы.