3 Разработка вычислительного канала МПС

3.1 Разработка функциональной схемы вычислительного канала

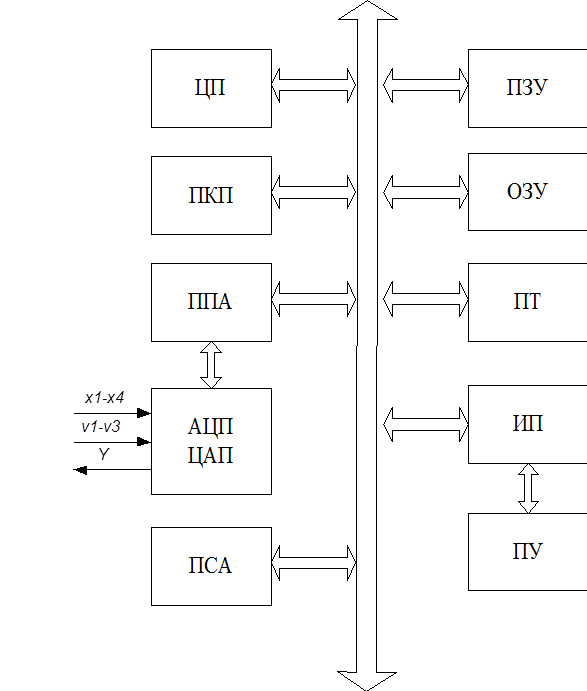

На рисунке 3 представлена функциональная схема вычислительного канала.

|

Рисунок 3 – Функциональная схема вычислительного канала

Центральный процессор (ЦП) в вычислительном канале представлен микросхемой КР580ВМ80А, для функционирования которой необходимы внешняя память ОЗУ и ПЗУ. Параллельный периферийный адаптер (ППА) осуществляет через буферные схемы связь с цифровыми датчиками, АЦП, ЦАП, исполнительными механизмами. Связь с внешней ЭВМ осуществляется через последовательны связной адаптер (ПСА). Обработка исключений и прерываний выполняется по приходу сигнала на контроллер приоритетов прерываний (КПП). Интерфейс пользователя (ИП) – предназначен для подключения к системе пульта управления (ПУ).

Уважаемый посетитель!

Чтобы распечатать файл, скачайте его (в формате Word).

Ссылка на скачивание - внизу страницы.